# ExpressLane PEX 8614-BA 12-Lane, 12-Port PCI Express Gen 2 Switch Data Book

Version 1.3

March 2011

Website www.plxtech.com

Technical Support www.plxtech.com/support

Phone 800 759-3735 408 774-9060

FAX 408 774-2169

Data Book PLX Technology, Inc.

#### **Revision History**

| Version | Date        | Description of Changes                                                                                                                                                        |

|---------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.0     | July, 2009  | Production Release, Silicon Revision BA.                                                                                                                                      |

| 1.3     | March, 2011 | Production update, Silicon Revision BA.  Applied miscellaneous corrections and enhancements throughout the data book.  Added support for Extended temperature (-10 to +85°C). |

#### **Copyright Information**

Copyright © 2009 – 2011 PLX Technology, Inc. All Rights Reserved. The information in this document is proprietary and confidential to PLX Technology. No part of this document may be reproduced in any form or by any means or used to make any derivative work (such as translation, transformation, or adaptation) without written permission from PLX Technology.

PLX Technology provides this documentation without warranty, term or condition of any kind, either express or implied, including, but not limited to, express and implied warranties of merchantability, fitness for a particular purpose, and non-infringement. While the information contained herein is believed to be accurate, such information is preliminary, and no representations or warranties of accuracy or completeness are made. In no event will PLX Technology be liable for damages arising directly or indirectly from any use of or reliance upon the information contained in this document. PLX Technology may make improvements or changes in the product(s) and/or the program(s) described in this documentation at any time.

PLX Technology retains the right to make changes to this product at any time, without notice. Products may have minor variations to this publication, known as errata. PLX Technology assumes no liability whatsoever, including infringement of any patent or copyright, for sale and use of PLX Technology products.

PLX Technology and the PLX logo are registered trademarks and Dual Cast, ExpressLane, *performance*PAK, Read Pacing, and *vision*PAK are trademarks of PLX Technology, Inc.

PCI Express is a trademark of the PCI Special Interest Group (PCI-SIG).

EUI-64 is a trademark of The Institute of Electrical and Electronics Engineers, Inc. (IEEE).

Tri-State is a registered trademark of National Semiconductor Corporation.

All product names are trademarks, registered trademarks, or service marks of their respective owners.

Document Number: 8614-BA-SIL-DB-P1-1.3

March, 2011 Preface

#### **Preface**

The information in this data book is subject to change without notice. This PLX data book to be updated periodically as new information is made available.

#### **Audience**

This data book provides functional details of PLX Technology's ExpressLane PEX 8614-BA 12-Lane, 12-Port PCI Express Gen 2 Switch, for hardware designers and software/firmware engineers.

#### **Supplemental Documentation**

This data book assumes that the reader is familiar with the following documents:

• PLX Technology, Inc. (PLX), www.plxtech.com

The PLX PEX 8614 Toolbox includes this data book and other supporting documentation, *such as* errata, and design and application notes.

- The Institute of Electrical and Electronics Engineers, Inc. (IEEE), www.ieee.org

- IEEE Standard 1149.1-1990, IEEE Standard Test Access Port and Boundary-Scan Architecture

- IEEE Standard 1149.1a-1993, IEEE Standard Test Access Port and Boundary-Scan Architecture

- IEEE Standard 1149.1-1994, Specifications for Vendor-Specific Extensions

- IEEE Standard 1149.6-2003, IEEE Standard Test Access Port and Boundary-Scan Architecture Extensions

- Intel Corporation, www.intel.com

- PHY Interface for the PCI Express Architecture, Version 2.00

- NXP Semiconductors, www.standardics.nxp.com

- The I2C-Bus Specification, Version 2.1

- PCI Special Interest Group (PCI-SIG), www.pcisig.com

- PCI Local Bus Specification, Revision 3.0

- PCI Bus Power Management Interface Specification, Revision 1.2

- PCI to PCI Bridge Architecture Specification, Revision 1.2

- PCI Express Base Specification, Revision 1.0a

- PCI Express Base Specification, Revision 1.1

- PCI Express Base Specification, Revision 2.0

- PCI Express Base Specification, Revision 2.0 Errata

- PCI Express Card Electromechanical Specification, Revision 2.0

- PCI Express Mini Card Electromechanical Specification, Revision 1.1

- PCI Express Architecture PCI Express Jitter and BER White Paper, Revision 1.0

- Personal Computer Memory Card International Association (PCMCIA), www.pcmcia.org

- ExpressCard Standard Release 1.0

- PXI Systems Alliance (PXI), www.pxisa.org

- PXI-5 PXI Express Hardware Specification, Revision 1.0

- SBS Implementers Forum, smbus.org

- System Management Bus (SMBus) Specification, Version 2.0

**Note:** In this data book, shortened titles are associated with the previously listed documents. The following table lists these abbreviations.

| Abbreviation                  | Document                                                                    |  |

|-------------------------------|-----------------------------------------------------------------------------|--|

| PCI r3.0                      | PCI Local Bus Specification, Revision 3.0                                   |  |

| PCI Power Mgmt. r1.2          | PCI Bus Power Management Interface Specification, Revision 1.2              |  |

| PCI-to-PCI Bridge r1.2        | PCI to PCI Bridge Architecture Specification, Revision 1.2                  |  |

| PCI Express Base r1.0a        | PCI Express Base Specification, Revision 1.0a                               |  |

| PCI Express Base r1.1         | PCI Express Base Specification, Revision 1.1                                |  |

| PCI Express Base r2.0         | PCI Express Base Specification, Revision 2.0                                |  |

| PCI ExpressCard CEM r2.0      | PCI Express Card Electromechanical Specification, Revision 2.0              |  |

| PCI ExpressCard Mini CEM r1.1 | PCI Express Mini Card Electromechanical Specification, Revision 1.1         |  |

| IEEE Standard 1149.1-1990     | IEEE Standard Test Access Port and Boundary-Scan Architecture               |  |

| IEEE Standard 1149.6-2003     | IEEE Standard Test Access Port and Boundary-Scan Architecture<br>Extensions |  |

| $I^2C$ Bus $v2.1$             | 7 2 D 2 D 2 D 2 D 2 D 2 D 2 D 2 D 2 D 2                                     |  |

| 12C Bus v2.1 <sup>a</sup>     | The $I^2C$ -Bus Specification, Version 2.1                                  |  |

| SMBus v2.0                    | System Management Bus (SMBus) Specification, Version 2.0                    |  |

a. Due to formatting limitations, the specification name may appear without the superscripted "2" in its title.

March, 2011 Terms and Abbreviations

### **Terms and Abbreviations**

The following table lists common terms and abbreviations used in this data book. Terms and abbreviations defined in the *PCI Express Base r2.0* are not included in this table.

| Terms and Abbreviations | Definitions                                                                                                                                                                                         |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8b/10b                  | Data-encoding scheme used on data transferred across a Link that is operating at either Gen 1 or Gen 2 Link speed (2.5 or 5.0 GT/s, respectively).                                                  |

| ACK                     | Acknowledge Control Packet. Control packet used by a destination to acknowledge data packet receipt. Signal that acknowledges signal receipt.                                                       |

| AMCAM                   | Address-mapping CAM that determines a memory Request route. Contains mirror copies of the PCI-to-PCI bridge <b>Memory Base</b> and <b>Memory Limit</b> registers in the switch.                     |

| ARI                     | Alternative Routing-ID Interpretation.                                                                                                                                                              |

| BAR                     | Base Address register.                                                                                                                                                                              |

| BER                     | Bit error rate.                                                                                                                                                                                     |

| BusNoCAM                | Bus Number-mapping CAM that determines the Completion route. Contains mirror copies of the PCI-to-PCI bridge <b>Secondary Bus Number</b> and <b>Subordinate Bus Number</b> registers in the switch. |

| CAM                     | Content-Addressable Memory.                                                                                                                                                                         |

| CDR                     | Clock Data Recovery.                                                                                                                                                                                |

| CRC                     | Cyclic Redundancy Check.                                                                                                                                                                            |

| CSRs                    | Configuration Space registers.                                                                                                                                                                      |

| DLL                     | Data Link Layer.                                                                                                                                                                                    |

| DMA                     | Direct Memory Access.                                                                                                                                                                               |

| Downstream Device       | Device that is connected to a downstream Port.                                                                                                                                                      |

| Downstream Port         | Port that is used to communicate with a device below it within the system hierarchy. A switch can have one or more downstream Ports.                                                                |

| ECC                     | Error-Correcting Code.                                                                                                                                                                              |

| ECRC                    | End-to-end Cyclic Redundancy Check.                                                                                                                                                                 |

| EIOS                    | Electrical Idle Ordered-Set.                                                                                                                                                                        |

| Electrical Idle         | Transmitter is in a High-Impedance state (+ and - are both at common mode voltage).                                                                                                                 |

| EP                      | Endpoint.                                                                                                                                                                                           |

| FC                      | Flow Control.                                                                                                                                                                                       |

| Field                   | Multiple register bits that are combined for a single function.                                                                                                                                     |

| GPIO                    | General-Purpose Input/Output.                                                                                                                                                                       |

| GT/s                    | Giga-Transfers per second.                                                                                                                                                                          |

| Half Station            | Internal hardware processing partition of Even- or Odd-numbered (Even or Odd) Ports.                                                                                                                |

| INCH                    | Ingress Credit Handler.                                                                                                                                                                             |

| InitFC                  | Initialization Flow Control.                                                                                                                                                                        |

| IOCAM                   | I/O Address-mapping CAM that determines an I/O Request route. Contains mirror copies of the PCI-to-PCI bridge I/O Base and I/O Limit registers in the switch.                                       |

| JTAG                    | Joint Test Action Group.                                                                                                                                                                            |

| Lane                    | A bidirectional pair of differential PCI Express I/O signals.                                                                                                                                       |

| LCRC                    | Link Cyclic Redundancy Check.                                                                                                                                                                       |

| Terms and Abbreviations   | Definitions                                                                                                                                                                                                                                                                        |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Link Interface            | Primary side of the NT Port, connects to external device pins. The secondary side of the NT Port is called the NT Port Virtual Interface, and connects to the internal virtual PCI Express interface.                                                                              |

| Local                     | Reference to PCI Express attributes (such as credits) that belong to the PCI Express Link logic.                                                                                                                                                                                   |

| LTSSM                     | Link Training and Status State Machine.                                                                                                                                                                                                                                            |

| LUT                       | Lookup Table.                                                                                                                                                                                                                                                                      |

| MRL                       | Manually operated Retention Latch.                                                                                                                                                                                                                                                 |

| NACK                      | Negative Acknowledge. Used in the SMBus-related content.                                                                                                                                                                                                                           |

| NAK                       | Negative Acknowledge.                                                                                                                                                                                                                                                              |

| N_FTS                     | Number of Fast Training Sequences field in Training Sets.                                                                                                                                                                                                                          |

| NT                        | Non-Transparent. A bridging technique used in the PCI Express Switch to isolate Memory spaces by presenting the processor as an endpoint rather than another memory system. The PEX 8614 supports one NT Port.                                                                     |

| Partial Completion        | In PCI Express, a single Read can have one or more Completions with data. If more than one Completion is returned, they are referred to as <i>Partial Completions</i> .                                                                                                            |

| PCI Express<br>Link Logic | Functional unit that provides the PCI Express conforming system interface. Includes the Serializer/ De-Serializer (SerDes) hardware interface modules and PCI Express interface, which provides the Physical Layer (PHY), Data Link Layer (DLL), and Transaction Layer (TL) logic. |

| PEC                       | Packet Error Code.                                                                                                                                                                                                                                                                 |

| PEX                       | PCI Express.                                                                                                                                                                                                                                                                       |

| PHY                       | Physical Layer.                                                                                                                                                                                                                                                                    |

| PIPE                      | PHY Interface for PCI Express architecture.                                                                                                                                                                                                                                        |

| PLL                       | Phase-Locked Loop.                                                                                                                                                                                                                                                                 |

| PM                        | Power Management.                                                                                                                                                                                                                                                                  |

| PME                       | Power Management Event.                                                                                                                                                                                                                                                            |

| Port                      | Interface to a group of SerDes and supporting logic that is capable of creating a Link, for communication with another Port.                                                                                                                                                       |

| P-P                       | PCI-to-PCI.                                                                                                                                                                                                                                                                        |

| PRBS                      | Pseudo-Random Bit Sequence.                                                                                                                                                                                                                                                        |

| QoS                       | Quality of Service.                                                                                                                                                                                                                                                                |

| RAS                       | Reliability, Availability, and Serviceability.                                                                                                                                                                                                                                     |

| RoHS                      | Restrictions on the use of certain Hazardous Substances (RoHS) Directive.                                                                                                                                                                                                          |

| RR                        | Round-Robin scheduling.                                                                                                                                                                                                                                                            |

| Rx                        | Receiver.                                                                                                                                                                                                                                                                          |

| SerDes                    | Serializer/De-Serializer. A high-speed differential-signaling parallel-to-serial and serial-to-parallel conversion logic attached to Lane pads.                                                                                                                                    |

| SMBus                     | System Management Bus.                                                                                                                                                                                                                                                             |

| SPI                       | Serial Peripheral Interface.                                                                                                                                                                                                                                                       |

| SSC                       | Spread-Spectrum Clock.                                                                                                                                                                                                                                                             |

March, 2011 Terms and Abbreviations

| Terms and Abbreviations | Definitions                                                                                                                                                                                                                                                                                                                                                                     |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Sticky Bits             | Register bits in which the current values are unchanged by a Hot Reset, Link Down event, or Secondary Bus Reset, while the switch is powered. Sticky bits are reset to default values by a Fundamental Reset. Applies to ROS, RW1CS, and RWS CSR types, and sometimes HwInit. (Refer to Table 13-5, "Register Types, Grouped by User Accessibility," for CSR type definitions.) |

| Sticky State            | Condition that causes a state machine to be stuck in a particular state, unable to make forward progress.                                                                                                                                                                                                                                                                       |

| TC                      | Traffic Class.                                                                                                                                                                                                                                                                                                                                                                  |

| TL                      | Transaction Layer.                                                                                                                                                                                                                                                                                                                                                              |

| TLC                     | Transaction Layer Control. The module performing PCI Express Transaction Layer functions.                                                                                                                                                                                                                                                                                       |

| TLP                     | Transaction Layer Packet. PCI Express packet formation and organization.                                                                                                                                                                                                                                                                                                        |

| Transparent             | Refers to standard PCI Express upstream-to-downstream routing protocol.                                                                                                                                                                                                                                                                                                         |

| TS1                     | Type 1 Training Sequence Ordered-Set.                                                                                                                                                                                                                                                                                                                                           |

| TS2                     | Type 2 Training Sequence Ordered-Set.                                                                                                                                                                                                                                                                                                                                           |

| Tx                      | Transceiver.                                                                                                                                                                                                                                                                                                                                                                    |

| UI                      | Unit Interval – 400 ps at 2.5 GT/s, 200 ps at 5.0 GT/s.                                                                                                                                                                                                                                                                                                                         |

| Upstream Device         | Device that is connected to the upstream Port.                                                                                                                                                                                                                                                                                                                                  |

| Upstream Port           | Port that is used to communicate with a device above it within the system hierarchy.                                                                                                                                                                                                                                                                                            |

| UTP                     | User Test Pattern.                                                                                                                                                                                                                                                                                                                                                              |

| VC                      | Virtual Channel. The PEX 8614 supports two Virtual Channels, VC0 and VC1.                                                                                                                                                                                                                                                                                                       |

| VCO                     | Voltage-Controlled Oscillator.                                                                                                                                                                                                                                                                                                                                                  |

| Vector                  | Address and data.                                                                                                                                                                                                                                                                                                                                                               |

| Virtual Interface       | Secondary side of the NT Port, connects to the internal virtual PCI Express interface.                                                                                                                                                                                                                                                                                          |

| WRR                     | Weighted Round-Robin scheduling.                                                                                                                                                                                                                                                                                                                                                |

## **Data Book Notations and Conventions**

| Notation / Convention     | Description                                                                                                                                                                                                                                                                                                                                 |

|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Blue text                 | Indicates that the text is hyperlinked to its description elsewhere in the data book. Left-click the blue text to learn more about the hyperlinked information. This format is often used for register names, register bit and field names, register offsets, chapter and section titles, figures, and tables.                              |

| PEX_XXXn[x] PEX_XXXp[x]   | When the signal name appears in all CAPS, with the primary Port description listed first, field [x] indicates the number associated with the signal balls/pads assigned to a specific SerDes module/Lane. The lowercase "n" (negative) or "p" (positive) suffix indicates the differential pair of signals, which are always used together. |

| # = Active-Low signals    | Unless specified otherwise, Active-Low signals are identified by a "#" appended to the term (for example, PEX_PERST#).                                                                                                                                                                                                                      |

| Program/code samples      | Monospace font (program or code samples) is used to identify code samples or programming references. These code samples are case-sensitive, unless specified otherwise.                                                                                                                                                                     |

| command_done              | Interrupt format.                                                                                                                                                                                                                                                                                                                           |

| Command/Status            | Register names.                                                                                                                                                                                                                                                                                                                             |

| Parity Error Detected     | Register parameter [bit or field] or control function.                                                                                                                                                                                                                                                                                      |

| Upper Base Address[31:16] | Specific Function in 32-bit register bounded by bits [31:16].                                                                                                                                                                                                                                                                               |

| Number multipliers        | k = 1,000 (10 <sup>3</sup> ) is generally used with frequency response.  K = 1,024 (2 <sup>10</sup> ) is used for Memory size references.  KB = 1,024 bytes.  M = meg.  = 1,000,000 when referring to frequency (decimal notation)  = 1,048,576 when referring to Memory sizes (binary notation)                                            |

| 255d                      | d = Suffix that identifies decimal values.                                                                                                                                                                                                                                                                                                  |

| 1Fh                       | h = Suffix that identifies hex values. Each prefix term is equivalent to a 4-bit binary value (Nibble). Legal prefix terms are 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, A, B, C, D, E, F.                                                                                                                                                              |

| 1010b                     | b = suffix which identifies binary notation ( <i>for example</i> , 01b, 010b, 1010b, and so forth). Not used with single-digit values of 0 nor 1.                                                                                                                                                                                           |

| 0 through 9               | Decimal numbers, or single binary numbers.                                                                                                                                                                                                                                                                                                  |

| byte                      | Eight bits – abbreviated to "B" (for example, 4B = 4 bytes).                                                                                                                                                                                                                                                                                |

| LSB                       | Least-Significant Byte.                                                                                                                                                                                                                                                                                                                     |

| lsb                       | Least-significant bit.                                                                                                                                                                                                                                                                                                                      |

| MSB                       | Most-Significant Byte.                                                                                                                                                                                                                                                                                                                      |

| msb                       | Most-significant bit.                                                                                                                                                                                                                                                                                                                       |

| DWord                     | Double-Word (32 bits) is the primary register size in these devices.                                                                                                                                                                                                                                                                        |

| QWord                     | Quad-Word (64 bits).                                                                                                                                                                                                                                                                                                                        |

| Reserved                  | Do not modify <i>Reserved</i> bits and words. Unless specified otherwise, these bits read as 0 and must be written as 0.                                                                                                                                                                                                                    |

| word                      | 16 bits.                                                                                                                                                                                                                                                                                                                                    |

## **Contents**

| Chapter 1 | Introduction                                            |

|-----------|---------------------------------------------------------|

| •         | 1.1 Overview                                            |

|           | 1.2 Features                                            |

|           |                                                         |

| Chapter 2 | Features and Applications 5                             |

| •         | 2.1 Flexible and Feature-Rich 12-Lane, 12-Port Switch 5 |

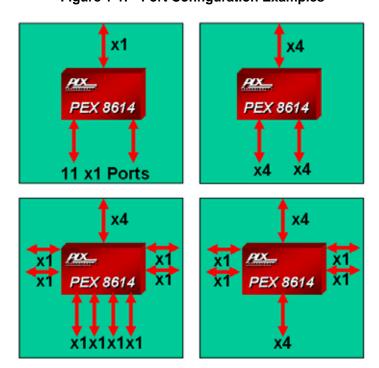

|           | 2.1.1 Highly Flexible Port Configurations               |

|           | 2.1.2 Non-Blocking Crossbar Switch Architecture         |

|           | 2.1.3 Low Packet Latency and High Performance           |

|           | 2.1.3.1 Data Payloads                                   |

|           | 2.1.3.2 Cut-Thru                                        |

|           | 2.1.4 Virtual Channels and Traffic Classes              |

|           | 2.1.5 Port Arbitration                                  |

|           | 2.1.6 End-to-End Packet Integrity                       |

|           | 2.1.7 Configuration Flexibility                         |

|           | 2.1.8 Interoperability                                  |

|           | 2.1.9 Low Power with Granular SerDes Control            |

|           | 2.1.10 Dynamic Lane Reversal                            |

|           | <b>2.1.11</b> <i>performance</i> PAK                    |

|           | 2.1.11.1 Read Pacing                                    |

|           | 2.1.11.2 Dual Cast 9                                    |

|           | 2.1.11.3 Dynamic Buffer Pool                            |

|           | 2.1.12 <i>vision</i> PAK                                |

|           | 2.1.12.1 Performance Monitoring                         |

|           | 2.1.12.2 Error Injection                                |

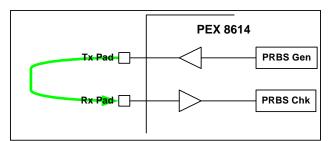

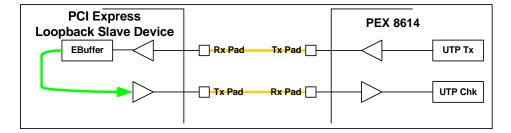

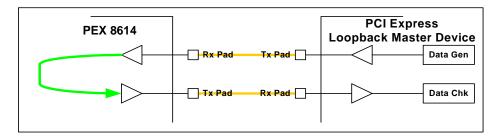

|           | 2.1.12.3 SerDes Loopback                                |

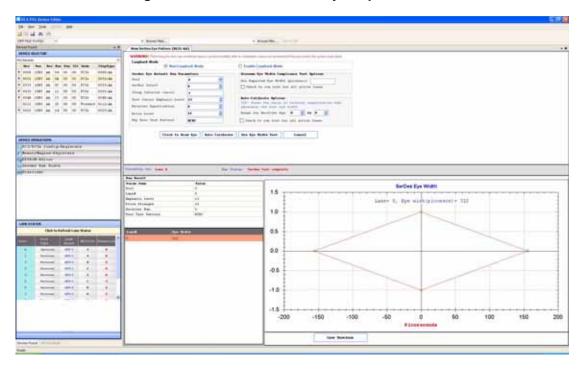

|           | 2.1.12.4 SerDes Eye Capture                             |

|           | 2.1.13 Hot Plug for High Availability                   |

|           | 2.1.14 Fully Compliant Power Management                 |

|           | 2.1.15 General-Purpose Input/Output Signals             |

|           | 2.1.16 Non-Transparent Dual Host and Failover Support – |

|           | NT Mode Only                                            |

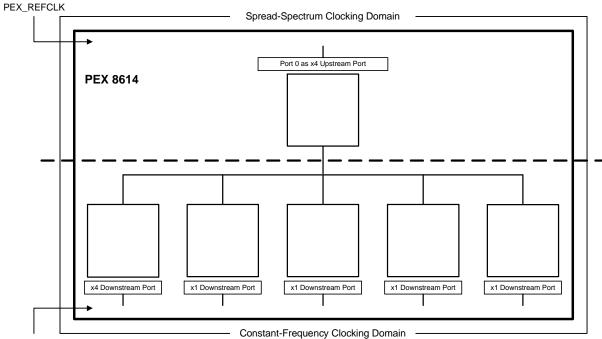

|           | 2.1.17 Spread-Spectrum Clock Isolation                  |

|           | 2.2 Applications                                        |

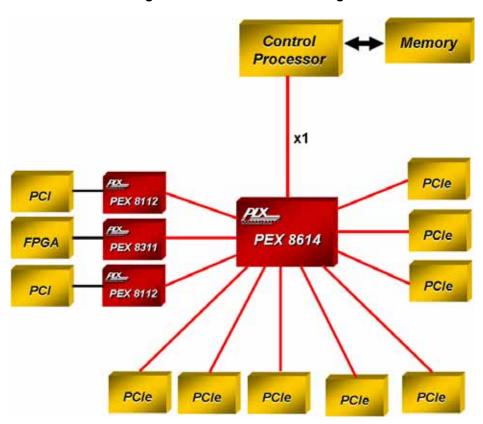

|           | 2.2.1 Host-Centric Fan-Out                              |

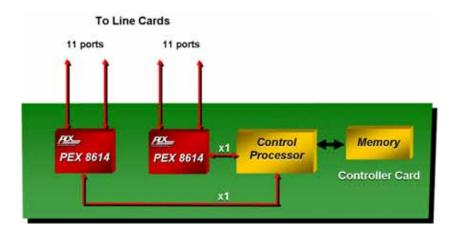

|           | 2.2.2 Control Plane Application                         |

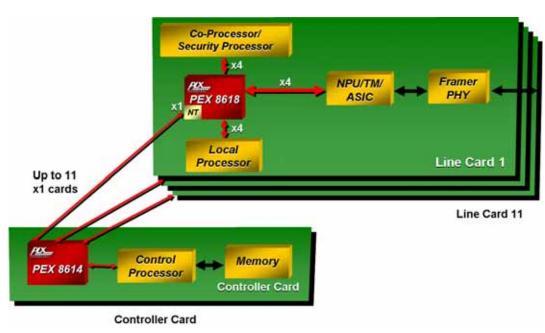

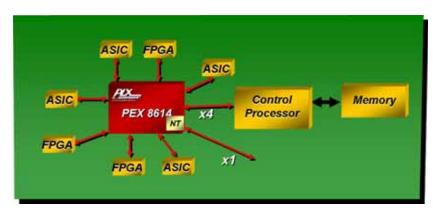

|           | 2.2.3 Embedded Control Planes                           |

|           | 2.2.4 Intelligent Adapter Board Usage – NT Mode Only    |

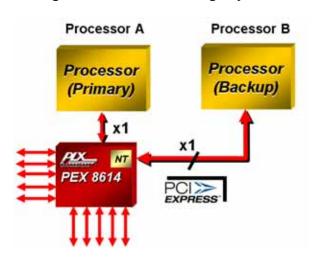

|           | 2.2.5 Active-Standby Failover Model – NT Mode Only      |

|           | 2.3 Software Usage Model                                |

|           | 2.3.1 System Configuration                              |

|           | 2.3.2 Interrupt Sources and Events                      |

| Chapter 3 | Signal Ball Description                              | 19 |

|-----------|------------------------------------------------------|----|

|           | 3.1 Introduction                                     | 19 |

|           | 3.2 Abbreviations                                    | 19 |

|           | 3.3 Internal Pull-Up Resistors                       | 20 |

|           | 3.4 Signal Ball Descriptions                         | 20 |

|           | 3.4.1 PCI Express Signals                            | 21 |

|           | 3.4.2 Serial Hot Plug Signals                        |    |

|           | 3.4.3 Serial EEPROM Signals                          |    |

|           | 3.4.4 Strapping Signals                              |    |

|           | 3.4.5 JTAG Interface Signals                         | 31 |

|           | 3.4.6 I <sup>2</sup> C/SMBus Slave Interface Signals | 32 |

|           | 3.4.7 Device-Specific Signals                        | 34 |

|           | 3.4.8 External Resistor Signals                      | 36 |

|           | 3.4.9 No Connect Signals                             |    |

|           | 3.4.10 Power and Ground Signals                      | 37 |

|           | 3.5 Physical Layout                                  |    |

|           |                                                      |    |

| Chapter 4 | Functional Overview                                  | 39 |

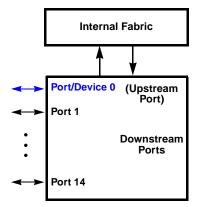

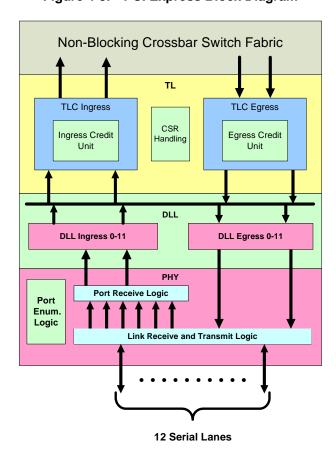

|           | 4.1 Hardware Architecture                            | 39 |

|           | 4.1.1 Port Functions                                 | 40 |

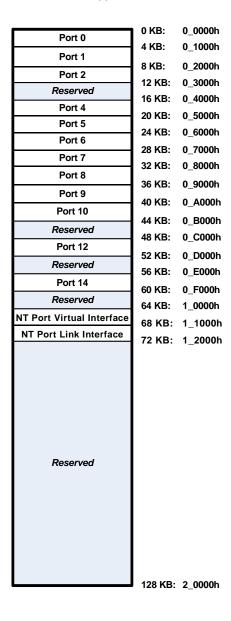

|           | 4.1.1.1 Port Configurations                          | 40 |

|           | 4.1.1.2 Port Numbering                               |    |

|           | 4.2 PCI Express Link Functional Description          |    |

|           | 4.3 Physical Layer                                   |    |

|           | 4.3.1 Physical Layer Features                        |    |

|           | 4.3.2 Physical Layer Status and Command Registers    | 44 |

|           | 4.3.3 Hardware Link Interface Configuration          |    |

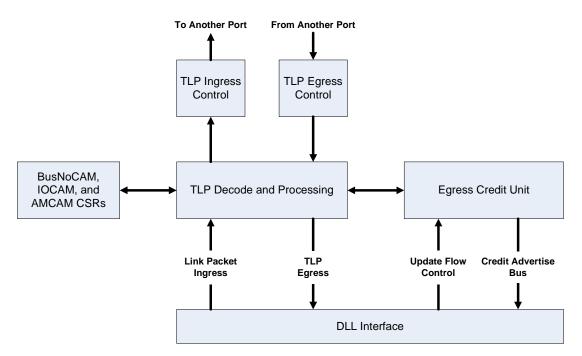

|           | 4.4 Transaction Layer                                |    |

|           | 4.4.1 Locked Transactions                            |    |

|           | 4.4.2 Relaxed Ordering                               | 47 |

|           | 4.4.3 TL Transmit/Egress Protocol – End-to-End       |    |

|           | Cyclic Redundancy Check                              |    |

|           | 4.4.4 TL Receive/Ingress Protocol                    |    |

|           | 4.4.5 Flow Control Credit Initialization             |    |

|           | 4.4.6 Flow Control Protocol                          |    |

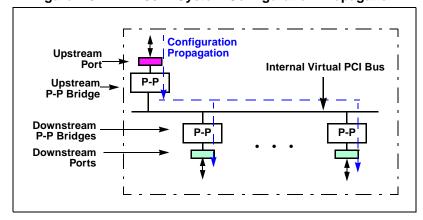

|           | 4.5 PCI-Compatible Software Model                    | 49 |

| Obantan F | Dood and Initialization                              | F4 |

| Chapter 5 | Reset and Initialization                             | _  |

|           | 5.1 Reset                                            |    |

|           | 5.1.1 Fundamental Reset                              |    |

|           | 5.1.2 Hot Reset                                      |    |

|           | 5.1.3 Secondary Bus Reset                            |    |

|           | 5.1.4 Register Bits that Affect Hot Reset            |    |

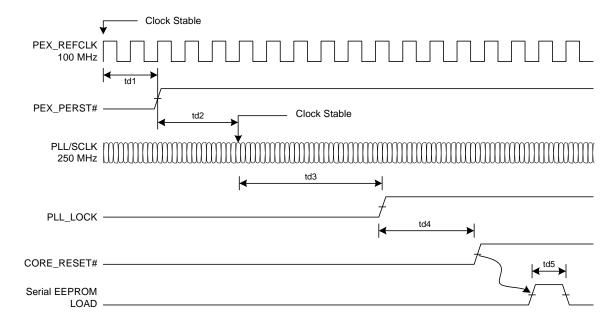

|           | 5.1.5 Reset and Clock Initialization Timing          |    |

|           | 5.2 Initialization Procedure                         |    |

|           | 5.2.1 Default Port Configuration                     |    |

|           | 5.2.2 Default Register Initialization                |    |

|           | 5.2.3 Device-Specific Registers                      |    |

|           |                                                      |    |

|           | 5.2.5 I <sup>2</sup> C Load Time                     | 56 |

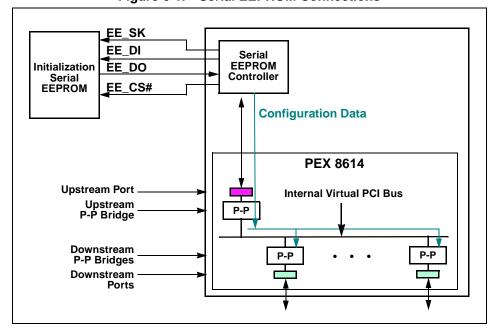

| Chapter 6 | Serial EEPROM Controller                                                | . 57 |

|-----------|-------------------------------------------------------------------------|------|

|           | 6.1 Overview                                                            | . 57 |

|           | 6.2 Features                                                            | . 58 |

|           | 6.3 Serial EEPROM Load following Upstream Port Reset                    |      |

|           | 6.4 Serial EEPROM Data Format                                           |      |

|           | 6.5 Serial EEPROM Initialization                                        |      |

|           | 6.6 PCI Express Configuration, Control, and Status Registers            |      |

|           | 6.7 Serial EEPROM Registers                                             |      |

|           | 6.8 Serial EEPROM Random Write/Read Access                              |      |

|           | 6.8.1 Writing to Serial EEPROM                                          |      |

|           | 6.8.2 Reading from Serial EEPROM                                        | . 65 |

|           | 6.8.3 Programming a Blank Serial EEPROM                                 | . 65 |

|           | 6.9 Serial EEPROM Loading of NT Port Link Interface                     | 00   |

|           | Registers – NT Mode Only                                                |      |

|           | 6.10 NT Port Expansion ROM – NT Mode Only                               | . 66 |

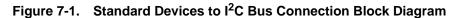

| Chapter 7 | I <sup>2</sup> C/SMBus Slave Interface Operation                        |      |

|           | 7.1 Introduction                                                        |      |

|           | 7.2 I <sup>2</sup> C Slave Interface                                    | . 67 |

|           | 7.2.1 I <sup>2</sup> C Support Overview                                 | . 67 |

|           | 7.2.2 I <sup>2</sup> C Addressing – Slave Mode Access                   |      |

|           | 7.2.3 I <sup>2</sup> C Slave Interface Register                         |      |

|           | _                                                                       |      |

|           | 7.2.1                                                                   |      |

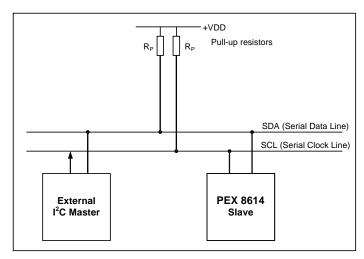

|           | 7.2.5 I <sup>2</sup> C Register Write Access                            |      |

|           | 7.2.5.1 I <sup>2</sup> C Register Write                                 |      |

|           | 7.2.6 I <sup>2</sup> C Register Read Access                             |      |

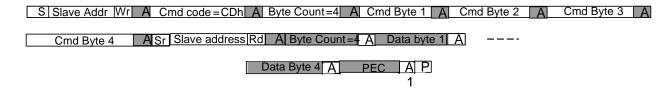

|           | 7.2.6.1 I <sup>2</sup> C Register Read Address Phase and Command Packet |      |

|           | 7.2.6.2 I <sup>2</sup> C Register Read Data Packet                      |      |

|           | 7.3 SMBus Slave Interface                                               |      |

|           | 7.3.1 SMBus Features                                                    |      |

|           | 7.3.2 SMBus Operation                                                   |      |

|           | 7.3.3.1 SMBus Block Write                                               |      |

|           | 7.3.3.2 SMBus Block Read                                                |      |

|           | 7.3.3.3 CSR Read, Using SMBus Block Read - Block Write Process Call     |      |

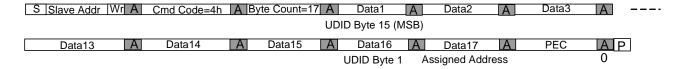

|           | 7.3.4 SMBus Address Resolution Protocol                                 |      |

|           | 7.3.4.1 SMBus UDID                                                      |      |

|           | 7.3.4.2 SMBus Supported ARP Commands                                    |      |

|           | 7.3.5 SMBus PEC Handling                                                |      |

|           | 7.3.6 Addressing PEX 8614 SMBus Slave                                   |      |

|           | 7.3.7 SMBus Timeout                                                     |      |

|           | 7.4 Switching between SMBus and I <sup>2</sup> C Bus Protocols          |      |

| Chapter 8 | Virtual Channels and Port Arbitration                                   | 99   |

| 5ap. 0    | 8.1 Quality of Service Support                                          |      |

|           | 8.2 Virtual Channel Support                                             |      |

|           | 8.2.1 Traffic Class to Virtual Channel Mapping                          |      |

|           | 8.2.2 Ingress VC Arbitration                                            |      |

|           | 8.2.3 Egress VC Arbitration                                             |      |

|           | 8.2.3.1 Fixed-Priority VC Arbitration                                   |      |

|           | 8.2.3.2 Round-Robin VC Arbitration                                      |      |

|           | 8.2.3.3 Weighted Round Robin Arbitration                                | 100  |

| 8.3 Queue Handling                                                     | 101   |

|------------------------------------------------------------------------|-------|

| 8.4 VC1 Ingress Credit                                                 | 102   |

| 8.4.1 VC1                                                              |       |

| 8.4.1.1 VC1 Threshold Registers                                        |       |

| 8.4.1.2 Programming the VC1 Global Enable and Threshold Registers      | 3 103 |

| 8.4.1.3 Usage Example                                                  | 103   |

|                                                                        |       |

| Chapter 9 Performance Features                                         |       |

| 9.1 Introduction                                                       |       |

| 9.2 DLLP Policies                                                      |       |

| 9.2.1 ACK DLLP Policy                                                  |       |

| 9.2.2 UpdateFC DLLP Policy                                             |       |

| 9.2.3 Unidirectional DLLP Policies                                     |       |

| 9.3 Ingress Resources                                                  |       |

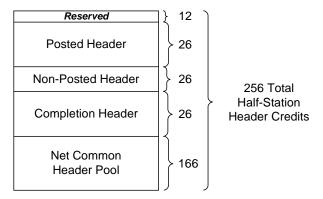

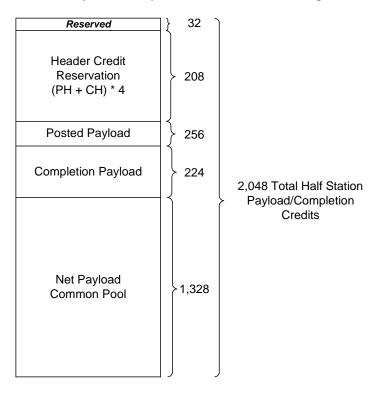

| 9.3.1 Initial Credit Allocation                                        |       |

| 9.3.2 Dynamic Buffering                                                |       |

| 9.3.3 Ingress Credit Handler Threshold Registers (Offsets A00h through |       |

| 9.3.4 Adjusting Initial Credit Values (Ingress Resources)              |       |

| 9.3.5 Credit Allocation When Common Pool Is Consumed                   |       |

| 9.3.6 INCH Port Pool Registers (Offsets 940h through 94Ch)             |       |

| 9.3.7 Wait for ACK – Avoiding Congestion                               |       |

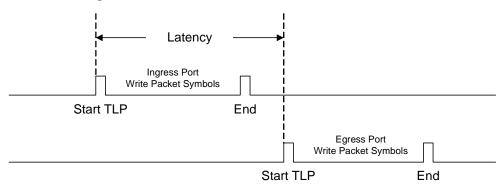

| 9.4 Latency                                                            |       |

| 9.4.1 Host-Centric Latency                                             |       |

| 9.4.2 Peer-to-Peer Latency                                             |       |

| 9.4.3 Other Latency Measurements                                       |       |

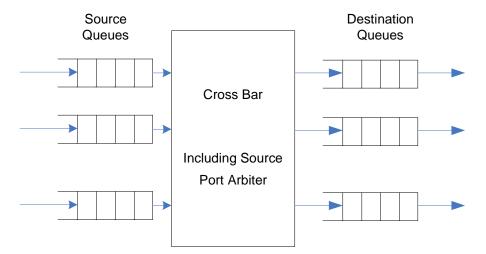

| 9.5 Queuing Options                                                    |       |

| 9.5.1 Destination Queuing                                              |       |

| 9.5.2 Source Queuing                                                   |       |

| 9.5.4 Port Bandwidth Allocation                                        |       |

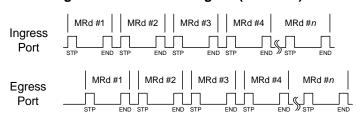

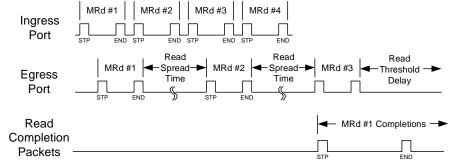

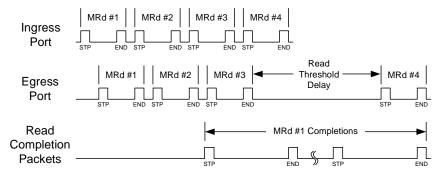

| 9.6 Read Pacing                                                        |       |

| 9.6.1 Read Pacing Example                                              |       |

| 9.6.2 Read Spacing (Spreading) Logic                                   |       |

| 9.6.3 Read Threshold                                                   |       |

| 9.6.4 Read Pacing Benefits                                             |       |

| 9.6.5 Enabling Read Pacing and Read Spreading                          |       |

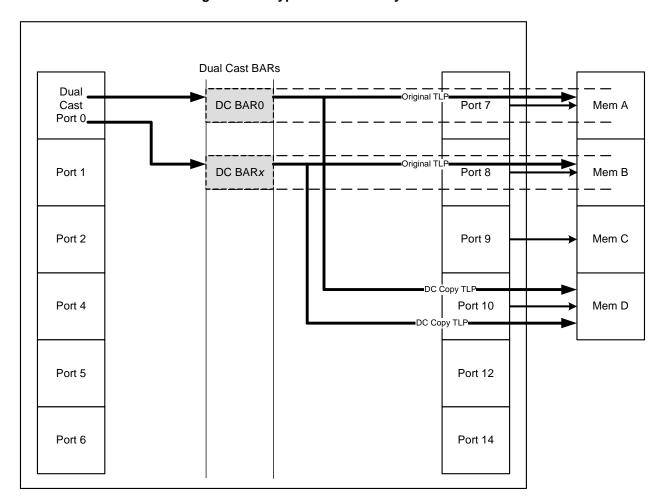

| 9.7 Dual Cast                                                          |       |

| 9.7.1 Introduction                                                     |       |

| 9.7.2 Dual Cast System Model                                           |       |

| 9.7.3 Dual Cast Control Registers                                      |       |

| 9.7.3.1 Dual Cast Low BAR[0-7], Dual Cast High BAR[0-7]                |       |

| 9.7.3.2 Dual Cast Low BAR[0-7] Translation, Dual Cast                  |       |

| High BAR[0-7] Translation                                              |       |

| 9.7.3.3 Dual Cast Low BAR[0-7] Setup, Dual Cast High BAR[0-7] Setu     |       |

| 9.7.3.4 Dual Cast Source Destination Port                              | •     |

| 9.7.4 Dual Cast Programming Example                                    |       |

|                                                                        | 140   |

| 9.7.4.1 Register Programming Steps                                     |       |

| 9.7.4.1 Register Programming Steps                                     | 145   |

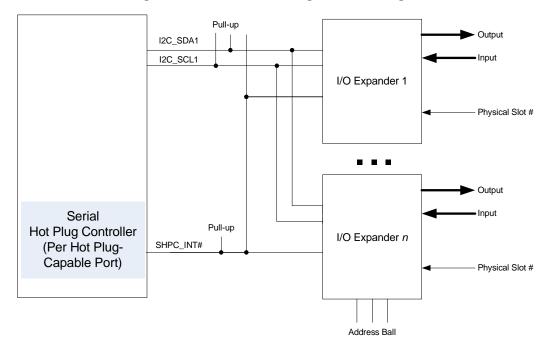

| Chapter 10 | Interrupts.  10.1 Interrupt Support  10.1.1 Interrupt Sources or Events  10.1.2 Interrupt Handling  10.2 INTx Emulation Support  10.2.1 INTx-Type Interrupt Message Re-Mapping and Collapsing  10.2.1.1 Interrupt Re-Mapping and Collapsing – NT PCI-to-PCI Bridge Mode  10.3 MSI Support  10.3.1 MSI Operation  10.3.1.1 NT PCI-to-PCI Bridge Mode MSIs – NT PCI-to-PCI Bridge Mode  10.3.2 MSI Capability Registers  10.4 PEX_INTA# Interrupts  10.5 General-Purpose Input/Output                                                                          | 147<br>148<br>152<br>153<br>154<br>155<br>156<br>157<br>157 |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| Chapter 11 | Hot Plug Support  11.1 Introduction  11.2 Hot Plug Features  11.3 Hot Plug Signals  11.4 Hot Plug Registers  11.5 Hot Plug Interrupts  11.6 Serial Hot Plug Controller  11.6.1 Hot Plug Operations by way of I <sup>2</sup> C I/O Expander  11.6.2 I <sup>2</sup> C I/O Expander Parts Selection and Pin Definition  11.6.3 Serial Hot Plug Port Enumeration and Assignment                                                                                                                                                                                  | 161<br>161<br>161<br>161<br>162<br>163                      |

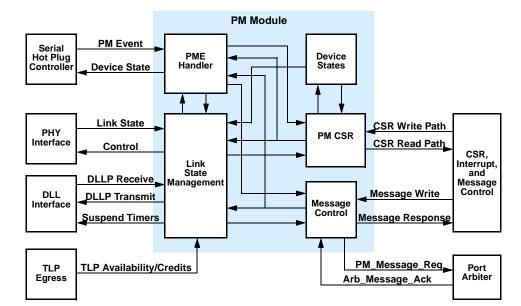

| Chapter 12 | Power Management  12.1 Overview  12.2 Power Management Features  12.3 Power Management Capability  12.3.1 Device Power Management States  12.3.1.1 D0 Device Power Management State  12.3.1.2 D3hot Device Power Management State  12.3.2 Link Power Management States  12.3.3 PCI Express Power Management Support  12.4 Power Management Tracking  12.5 Power Management Event Handler                                                                                                                                                                     | 169 170 171 171 171 173 173                                 |

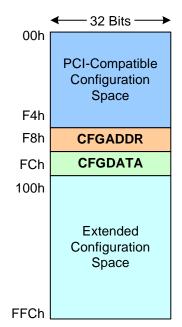

| Chapter 13 | Transparent Port Registers  13.1 Introduction  13.2 Type 1 Port Register Map  13.3 Port Register Configuration and Map  13.4 Register Access  13.4.1 PCI r3.0-Compatible Configuration Mechanism  13.4.2 PCI Express Enhanced Configuration Access Mechanism  13.4.3 Device-Specific Memory-Mapped Configuration Mechanism  13.5 Register Descriptions  13.6 PCI-Compatible Type 1 Configuration Header Registers (Offsets 00h – 3Ch)  13.7 PCI Power Management Capability Registers (Offsets 40h – 44h)  13.8 MSI Capability Registers (Offsets 48h – 64h) | 185 186 191 193 193 195 196                                 |

| 13.9  |      | Express Capability Registers                                                 |     |

|-------|------|------------------------------------------------------------------------------|-----|

|       |      | fsets 68h – A0h)                                                             | 221 |

| 13.10 |      | osystem ID and Subsystem Vendor ID Capability<br>gisters (Offsets A4h – FCh) | 245 |

| 13.11 |      | vice Serial Number Extended Capability Registers                             |     |

| 10.11 |      | fsets 100h – 134h)                                                           | 246 |

| 13.12 |      | ver Budget Extended Capability Registers                                     |     |

| 10.12 |      | fsets 138h – 144h)                                                           | 248 |

| 13.13 |      | ual Channel Extended Capability Registers                                    | 240 |

| 13.13 |      | fsets 148h – 1BCh)                                                           | 251 |

| 12.1  |      | WRR Port Arbitration Table Registers                                         | 251 |

| 13.1  | J. I | •                                                                            | 250 |

| 10 11 | Dai  | (Offsets 1A8h – 1BCh)                                                        | 258 |

| 13.14 |      | vice-Specific Registers                                                      | 004 |

|       | ,    | fsets 1C0h – 51Ch)                                                           | 261 |

| 13.1  | 4.1  | Device-Specific Registers – Error Checking and Debug                         |     |

|       |      | (Offsets 1C0h – 1FCh)                                                        | 262 |

| 13.1  | 4.2  | , , ,                                                                        |     |

|       |      | (Offsets 200h – 25Ch)                                                        | 294 |

| 13.1  | 4.3  | Device-Specific Registers – Serial EEPROM                                    |     |

|       |      | (Offsets 260h – 26Ch)                                                        | 370 |

| 13.1  | 4.4  | Device-Specific Registers – Miscellaneous Control                            |     |

|       |      | (Offset 28Ch)                                                                | 376 |

| 13.1  | 4.5  | Device-Specific Registers – I <sup>2</sup> C Slave Interface                 |     |

|       |      | (Offsets 290h – 2C4h)                                                        | 377 |

| 13.1  | 46   | Device-Specific Registers – Bus Number CAM                                   | 0   |

| 10.1  | 1.0  | (Offsets 2C8h – 304h)                                                        | 378 |

| 13.1  | 47   | Device-Specific Registers – I/O CAM                                          | 070 |

| 10.1  | 7.7  | (Offsets 308h – 340h)                                                        | 383 |

| 13.1  | 1Ω   | Device-Specific Registers – SMBus Slave Interface                            | 303 |

| 13.1  | 4.0  | (Offset 344h)                                                                | 390 |

| 13.1  | 4.0  | Device-Specific Registers – Address-Mapping CAM                              | 390 |

| 13.1  | 4.9  |                                                                              | 202 |

| 40.4  | 4.40 | (Offsets 348h – 444h)                                                        | 392 |

| 13.1  | 4.10 | Device-Specific Registers – Vendor-Specific Dual Cast                        | 400 |

|       |      | Extended Capability (Offsets 448h – 51Ch)                                    | 406 |

| 13.15 |      | S Extended Capability Registers                                              |     |

|       |      | fsets 520h – 52Ch)                                                           | 426 |

| 13.16 |      | vice-Specific Registers                                                      |     |

|       |      | fsets 530h – F8Ch)                                                           | 431 |

| 13.1  | 6.1  | Device-Specific Registers – Virtual Channel Weighted                         |     |

|       |      | Round Robin Arbitration (Offsets 530h – 540h)                                | 433 |

| 13.1  | 6.2  | Device-Specific Registers – Read Pacing                                      |     |

|       |      | (Offsets 544h – 554h)                                                        | 438 |

| 13.1  | 6.3  | Device-Specific Registers – Port Configuration                               |     |

|       |      | (Offsets 574h – 628h)                                                        | 446 |

| 13.1  | 6.4  | Device-Specific Registers – General-Purpose Input/Output                     |     |

|       |      | (Offsets 62Ch – 65Ch)                                                        | 448 |

| 13.1  | 6.5  | Device-Specific Registers – Ingress Control and Port Enable                  |     |

|       |      | (Offsets 660h – 67Ch)                                                        | 467 |

| 13.1  | 6.6  | Device-Specific Registers – IOCAM Base and Limit                             |     |

|       |      | Upper 16 Bits (Offsets 680h – 6BCh)                                          | 480 |

| 13.1  | 6.7  | Device-Specific Registers – Base Address Shadow                              | .00 |

|       | 5.,  | (Offsets 6C0h – 73Ch)                                                        | 484 |

|       |      | \                                                                            |     |

|            | 13.16.8                                                                                                                 | Device-Specific Registers – Virtual Channel Resource Control Shadow (Offsets 740h – 83Ch)                                                                                                                                                                                        | . 497                                                |

|------------|-------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

|            | 13.16.9                                                                                                                 | Device-Specific Registers – Ingress Credit Handler Port Pool (Offsets 940h – 94Ch)                                                                                                                                                                                               |                                                      |

|            | 13.16.10                                                                                                                | Device-Specific Registers – Vendor-Specific Extended                                                                                                                                                                                                                             |                                                      |

|            | 40.40.44                                                                                                                | Capability 2 (Offsets 950h – 95Ch)                                                                                                                                                                                                                                               | 535                                                  |

|            | 13.16.11                                                                                                                | Device-Specific Registers – ACS Extended Capability (Offsets 980h – 9FCh)                                                                                                                                                                                                        | 537                                                  |

|            | 13.16.12                                                                                                                | Device-Specific Registers – Ingress Credit Handler Threshold                                                                                                                                                                                                                     | . 007                                                |

|            |                                                                                                                         | (Offsets A00h – B7Ch)                                                                                                                                                                                                                                                            | 598                                                  |

|            | 13.16.13                                                                                                                | Device-Specific Registers – Physical Layer                                                                                                                                                                                                                                       | C40                                                  |

|            | 13 16 14                                                                                                                | (Offsets B80h – C30h)                                                                                                                                                                                                                                                            | . 610                                                |

|            | 10110111                                                                                                                | (Offsets E00h – E3Ch)                                                                                                                                                                                                                                                            | 631                                                  |

|            | 13.16.15                                                                                                                | Device-Specific Registers – Physical Layer                                                                                                                                                                                                                                       |                                                      |

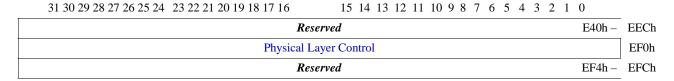

|            | 10.10.10                                                                                                                | (Offsets E40h – EFCh)                                                                                                                                                                                                                                                            | 668                                                  |

|            | 13.16.16                                                                                                                | Device-Specific Registers – Source Queue Weight and Soft Error (Offsets F00h – F3Ch)                                                                                                                                                                                             | 672                                                  |

|            | 13.16.17                                                                                                                | Device-Specific Registers – Error Reporting                                                                                                                                                                                                                                      | 012                                                  |

|            |                                                                                                                         | (Offsets F40h – F4Ch)                                                                                                                                                                                                                                                            | 681                                                  |

|            | 13.16.18                                                                                                                | Device-Specific Registers – ARI Capability                                                                                                                                                                                                                                       |                                                      |

|            | 13.17 Adv                                                                                                               | (Offsets F50h – F8Ch)                                                                                                                                                                                                                                                            | 686                                                  |

|            |                                                                                                                         | gisters (Offsets FB4h – FDCh)                                                                                                                                                                                                                                                    | 693                                                  |

| 01 4 44    |                                                                                                                         |                                                                                                                                                                                                                                                                                  |                                                      |

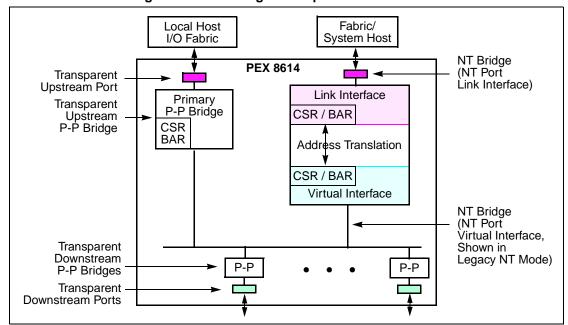

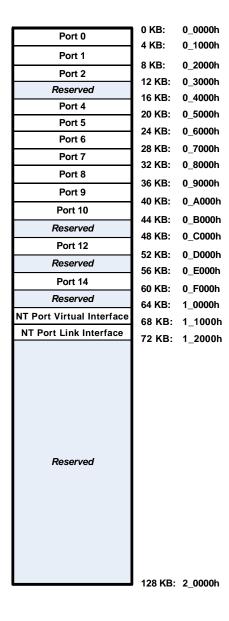

| Chapter 14 |                                                                                                                         | sparent Bridging – NT Mode Only                                                                                                                                                                                                                                                  |                                                      |

|            |                                                                                                                         | Device Type Identification                                                                                                                                                                                                                                                       |                                                      |

|            |                                                                                                                         | NT Port Features                                                                                                                                                                                                                                                                 |                                                      |