# PEX 85XX EEPROM – PEX 8518/8517/8512/8508 Design Note

July 2007, Version 1.1

# Purpose and Scope

Default register values in the PEX 8518/8517/8512/8508 switches may not be appropriate for all designs. Software can program most device registers, however some registers need to be programmed prior to linkup or BIOS/OS enumeration and therefore the optional EEPROM or I<sup>2</sup>C interface can be used to initialize the PEX 8518/8517/8512/8508 registers. This document provides information for engineers to implement the serial EEPROM hardware and software for PEX 8518, PEX 8517, PEX 8512, and PEX 8508 PCI Express<sup>™</sup> switches. This document also lists PEX 8518/8517/8512/8508 RDK EEPROM values that differ from default register values, in Table 26, beginning on page 33.

This document pertains only to the PEX 8518, PEX 8517, PEX 8512, and PEX 8508 devices. These three devices will be referred to as "PEX 85xx" for the remainder of this document.

# 1. EEPROM Usage

The PEX 85xx serial EEPROM controller downloads EEPROM contents to initialize registers when the EEPROM is present (EE\_PR# input strapped low) and one of the following occurs:

- PEX\_PERST# (Reset) input is returned high, following a Fundamental Reset (Cold or Warm Reset)

- Hot Reset is received at the Upstream port or the Upstream port exits a DL-Down condition, and if neither of the following Debug Control register bits are set:

- Hot Reset EEPROM Load Disable (Port 0 offset 1DCh bit 17)

- Upstream Hot Reset Severity Control (Port 0 offset 1DCh bit 16)

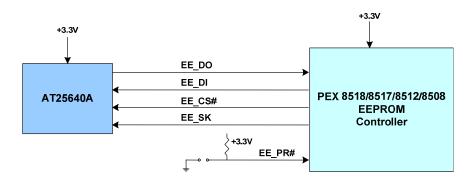

Figure 1. PEX 8518/8517/8512/8508 8KB SPI EEPROM Interface

# 2. **EEPROM** Basics

# 2.1. Compatible EEPROMs

If the optional EEPROM is implemented, the PEX 85xx switch requires an SPI-compatible, 64-Kbit (8-Kbit x 8-bit) to 512-Kbit EEPROM with 16-bit addressing that can operate at a frequency of 7.8MHz with 3.3V signaling. Please refer to the EEPROM manufacturer datasheets for operational specifications.

When the PEX 85xx is operating in either transparent mode or non-transparent mode without the need for Expansion ROM, 8KB of EEPROM storage is sufficient for the 7744 bytes of configuration data. Direct connection between the PEX 8518 and the Atmel AT25640A (8Kbit x 8-bit), 2.7V-5.5V EEPROM is shown in Figure 1 above.

Most SPI EEPROMs are limited to 5MHz operation, or can support higher frequency only at supply voltages greater than 3.3V. EEPROMs that are limited to 5 MHz operation are not compatible. The maximum voltage that the PEX 85xx switches will tolerate on the I/O pins is 4.6V. If the EEPROM is powered at 5V in order to operate at the required 7.8MHz frequency, external voltage level shifting circuitry is required between the EEPROM and the PEX 85xx EEPROM interface.

## 2.2. SPI Interface Pin Description

The PEX 85xx integrated EEPROM controller uses the Serial Peripheral Interface (SPI) bus, which is a 4-wire, synchronous, full duplex, master/slave serial communications interface. The four wires are:

- 1. Chip select EE\_CS#, which the PEX 85xx asserts low to enable the EEPROM. PEX 85xx does not assert EE\_CS# output if EE\_PR# input is high (signaling that no EEPROM is present).

- 2. Serial clock EE\_SK, which provides the interface timing and is driven only by a SPI bus master. PEX 85xx as master drives and toggles the EE\_SK clock to shift serial data between the PEX 85xx and the EEPROM in blocks of 8 bits. PEX 85xx does not drive EE\_SK clock output if EE\_PR# input is high. PEX 85xx drives and toggles the EE\_SK clock output only when it is accessing the EEPROM.

- 3. EE\_DI (PEX 85xx output) carries the master-out slave-in serial data, which the PEX 85xx shifts out on the falling edge of the serial clock EE\_SK.

- 4. EE\_DO (PEX 85xx input) carries the master-in slave-out serial data, which the PEX 85xx latches on the rising edge of the serial clock EE\_SK.

The PEX 85xx switches have weak internal pull-up resistors (~50 k $\Omega$ ) on the EE\_DI, EECS# and EE\_DO signals to keep the SPI bus from floating when it is not being actively driven. The system designer may choose to add stronger pull-ups (5 k $\Omega$ -10 k $\Omega$ ) on these lines.

# 2.3. Sequential Read

When the PEX 85xx reads the serial EEPROM, it asserts the EE\_CS# chip select, and serially transmits the SPI Read command (0000 0011), followed by 16 address bits, on the EE\_DI output (EEPROM DI input). In the 8KB EEPROM, the A15-A13 address bit values are Don't Care. The PEX 85xx then clocks in the serial data on the EE\_DO input (EEPROM DO output). The PEX 85xx reads sequential data from the EEPROM by continuing to drive EE\_CS# low, which causes the EEPROM to automatically increment its internal address register, and shift out the 8 data bits at each new address.

# 2.4. Data Format

All instructions, addresses and input data bytes are shifted with the most significant bit first. Dword data is stored in the serial EEPROM in Little Endian format. For example, the Device/Vendor ID value 851810B5h is stored in the EEPROM with the byte B5h at the lower EEPROM byte address.

The Atmel AT25640A can be programmed directly through the PEX 85xx switch, by using PLX software (PEX GUI and/or APIs) included in the PEX SDK.

# 3. PEX 85xx EEPROM Presence Detection and Error Detection

## 3.1. **EEPROM Presence Detection**

The EE\_PR# input has a weak internal pull-up resistor (~50 k $\Omega$ ), to hold the input in the inactive state when an EEPROM is not present and no trace is connected to this signal.

When the PEX\_PERST# input (Fundamental Reset) is de-asserted, the PEX 85xx latches the EE\_PR# (EEPROM Present) input to determine whether an EEPROM is present. If EE\_PR# input state is detected as low, the PEX 85xx normally downloads data from the serial EEPROM and copies it into the PEX 85xx registers. If the EE\_PR# input is high (EEPROM not present), the PEX 85xx EEPROM interface is disabled. If EE\_PR# at reset is high and is then toggled low at runtime, the PEX 85xx will not detect the state change, and the EEPROM interface will remain disabled.

A corrupted EEPROM can be re-programmed if EE\_PR# input is always low, and the EEPROM is either removed or PEX 85xx is forced to read all 1's from the EEPROM to cause a CRC error. To cause the PEX 85xx to read all 1's, the EE\_DO input could be pulled high, or the EEPROM CS# could be switched off. At runtime, the EEPROM can then be carefully hot-plugged into its socket or otherwise re-enabled to allow the EEPROM to be re-programmed by PEX 85xx software.

## 3.2. CRC Error Detection

The PEX 85xx supports CRC (Cyclic Redundancy Code) error detection of the EEPROM contents. The EEPROM is programmed such that the last Dword of data at EEPROM byte address 1E3Ch is the CRC value, which is calculated as a function of all preceding data in the EEPROM image. When the PEX 85xx downloads initialization data from the EEPROM, it performs the same calculation used to generate the EEPROM CRC value, and compares its result to the CRC value downloaded from the EEPROM. If the calculated CRC value matches the CRC value read from the EEPROM, the probability is high that the EEPROM contents were downloaded correctly.

CRC error detection is enabled as default, by the initial value (0) of the CRC DISABLE bit, at Port 0 register 260h bit 21. If CRC error detection is enabled (default), and the CRC value that the PEX 85xx calculates after downloading the EEPROM contents matches the CRC value downloaded from the serial EEPROM, the PEX 85xx loads its registers with the EEPROM values. If the CRC value that the PEX 85xx calculates after downloading the EEPROM contents does not match the CRC value downloaded from the serial EEPROM, the PEX 85xx discards the downloaded EEPROM values, and instead sets its registers to default values.

CRC error detection can be disabled by setting the CRC DISABLE bit (Port 0 register 260h bit 21) to 1, in the serial EEPROM location corresponding to the CRC DISABLE bit. If the CRC DISABLE bit is set to disable CRC error detection, the PEX 85xx loads its registers with the EEPROM values. Software can also set this bit to cause the PEX 85xx to disable CRC error detection for subsequent runtime EEPROM downloads. However, disabling EEPROM CRC error detection is not recommended.

C/C++ code to compute the CRC value is included in the PLX PEX SDK. The CRC polynomial value is DB710641h. Example code to access and compute the CRC value for the PEX 8518 EEPROM is included in the file (default installation path):

C:\Plx\PlxSdk\Windows\PlxApi\PlxApi.c

# 3.3. EEPROM Presence and CRC Status Reporting

The PEX85xx reports the status of the EE\_PR# (EEPROM Present) input, whether registers were loaded from EEPROM or whether an EEPROM CRC error was detected, in the EEPROM PRESENT bits in the EEPROM Status and Control register, as follows:

Serial EEPROM Present Status (Port 0 register 260h bits [17:16])

- 00b = Not present

- 01b = EEPROM present, no CRC error

- 10b = Reserved

- 11b = EEPROM present with CRC error default reset values used

# 4. Expansion ROM

If the application requires Expansion ROM space, a 64KB EEPROM can be used with additional circuitry requirements. The lowest 8KB will be used for PEX 85xx register storage, while the uppermost 32KB can be Expansion ROM storage.

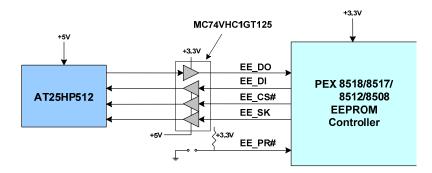

Applications requiring Expansion ROM may use the AT25HP512 (64Kbit x 8-bit) device. This interface requires some external buffering between the PEX 85xx EEPROM controller and the AT25HP512, as shown in Figure 2 below. This EEPROM can operate at 7.8MHz only when it is powered at 5V. Level translation buffers should be used to convert the PEX 85xx 3.3V output levels to 5V input levels compatible with the EEPROM. Similarly, the EEPROM output should be level translated from 5V to 3.3V in order to prevent electrical damage to the PEX 85xx EE\_DO input. On Semiconductor's MC74VHC1GT125 tri-state buffer provides the necessary level translation for both directions. Four of these devices are required (one per pin).

Figure 2. PEX 8518/8517/8512/8508 and 64KB SPI EEPROM Interface

The AT25HP512 EEPROM can be written only by using 128-byte Page Mode writes, which the PEX 85xx cannot perform. Therefore this EEPROM must be programmed by an external EEPROM programmer.

# 5. PEX 85xx EEPROM Software Interface

# 5.1. PEX 85xx EEPROM Control, Status and Data Registers

Software can access the EEPROM using two memory-mapped registers in the PEX 85xx upstream port. Address BAR0 + 260h is the EEPROM Status and Control register, in which bits [31:24] are a copy of the Status register within the EEPROM. Offset 264h is the EEPROM Buffer, which contains 4 bytes of data to either write to, or have been read from, the EEPROM. The register descriptions (Register 1 and Register 2) are shown below.

| Bits  | Name                                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Туре | EEPROM | Initial |

|-------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------|---------|

|       |                                      | EEPROM Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |        |         |

| 12:0  | EEPROM BLOCK<br>ADDRESS              | EEPROM Block Address for 32 KB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | R/W  | Yes    | 0000h   |

| 15:13 | EEPROM<br>COMMAND                    | Commands to serial EEPROM Controller:<br>001b = Write EEPROM STATUS [31:24] bits to the<br>EEPROM internal status register<br>010b = Write four bytes of data from the EEPROM<br>BUFFER into memory location pointed to by<br>the EEPROM Block Address<br>011b = Read four bytes of data from memory<br>location pointed to by the EEPROM Block<br>Address into EEPROM BUFFER<br>100b = Reset Write Enable latch<br>101b = Read EEPROM internal status register and<br>write data to EEPROM STATUS [31:24] bits<br>110b = Set Write Enable latch<br>All other encodings are <i>Reserved</i> | R/W  | Yes    | 000Ь    |

|       |                                      | EEPROM Status                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | i    | 1      | i       |

| 17:16 | EEPROM<br>PRESENT                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      | Yes    | 00b     |

| 19:18 | EEPROM<br>COMMAND<br>STATUS          | Serial EEPROM Command status<br>00b = EEPROM Command complete<br>01b = EEPROM Command <b>not</b> complete<br>10b = EEPROM Command complete with CRC error<br>11b = <i>Reserved</i>                                                                                                                                                                                                                                                                                                                                                                                                          |      | Yes    | 00b     |

| 20    | EEPROM BLOCK<br>ADDRESS<br>UPPER BIT | EEPROM BLOCK ADDRESS upper bit [13]<br>Extends EEPROM to 64K Bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R/W  | Yes    | 0       |

| 21    | CRC DISABLE                          | 0b = EEPROM input data uses CRC<br>1b = EEPROM input data CRC disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | R/W  | Yes    | 0       |

| 23:22 | -                                    | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |        | 00b     |

|       |                                      | Status Data from EEPROM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1    |        |         |

| 24    | EEPROM_RDY#                          | 0b = EEPROM is ready to send data<br>1b = a write cycle is in progress                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | R/W  | Yes    | 0       |

| 25    | EEPROM_WEN                           | 0b = EEPROM Write is disabled<br>1b = EEPROM Write is enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R/W  | Yes    | 0       |

| 27:26 | EEPROM_BP[1:0]                       | EEPROM Block-Write Protect bits (see Table 1 below)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | R/W  | Yes    | 00b     |

| 30:28 | EEPROM WRITE<br>STATUS               | These bits = 000b when EEPROM is not in an<br>internal Write cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R/W  | Yes    | 000b    |

| 31    | EEPROM_WPEN                          | EEPROM Write Protect Enable<br>When this bit:<br>= 0b and EEPROM_WEN = 1b, the EEPROM Status<br>register is writable<br>= 1b, the EEPROM Status register is protected                                                                                                                                                                                                                                                                                                                                                                                                                       | R/W  | Yes    | 0       |

#### Register 1. 260h EEPROM Status and Control Register (only Port 0)

| BP[1:0] | Level       |             | Array Addres | ses Protected |              |

|---------|-------------|-------------|--------------|---------------|--------------|

|         |             | 8 KB Device | 16 KB Device | 32 KB Device  | 64 KB Device |

| 00b     | 0           | None        | None         | None          | None         |

| 01b     | 1 (top 1/4) | 1800 – 1FFF | 3000 – 3FFF  | 6000 – 7FFF   |              |

| 10b     | 2 (top 1/2) | 1000 – 1FFF | 2000 – 3FFF  | 4000 – 7FFF   |              |

| 11b     | 3 (All)     | 0000 – 1FFF | 0000 – 3FFF  | 0000 – 7FFF   |              |

#### Table 1. Serial EEPROM Block-Write Protect Bits

#### Register 2. 264h EEPROM Buffer (only Port 0)

| Bits | Name             | Description   | Туре | EEPROM | Initial |

|------|------------------|---------------|------|--------|---------|

| 31:0 | EEPROM<br>BUFFER | EEPROM Buffer | R/W  | Yes    | 0h      |

In the EEPROM Status and Control register:

- The lower 13 bits contain the Dword EEPROM address (Byte address divided by 4) to be accessed

- The next 3 bits contain the EEPROM command code (operation to be performed)

- Bits [19:16] are Read-Only, so when writing this register the value is Don't Care

- Bits [23:20] must be 0 to read or write PEX 85xx register data to the EEPROM

- Bits [31:24] are a copy of the Status register within the EEPROM, so when writing or reading PEX 85xx register data to/from the EEPROM (using the EEPROM Write Data (Command 010b) or Read Data (Command 011b) instructions in bits [15:13]), bits [31:24] are not written to the Status register within the EEPROM.

The EEPROM will power up in the Write Disable state. Therefore, all programming instructions must be preceded by a Write Enable instruction (Command 110b).

To protect the device against inadvertent writes, the Write Disable instruction (Command 100b) disables all programming modes.

# 5.2. Software Read/Write Software Access to the EEPROM through the PEX 85xx

#### 5.2.1. Reading and Writing Data

Using the PEX 85xx EEPROM Status and Control and EEPROM Buffer registers, software reads or writes 4 bytes (Dword-aligned) in every access to the EEPROM. Dword addresses for each PEX 85xx register are listed in the *PEX 85xx Data Book*, Appendix A, Tables A-1 and A-2. To determine the EEPROM Dword address for a particular PEX 85xx register, select the PEX 85xx register's byte address in the leftmost column, and then in that row select the column for the particular PEX 85xx port. The 13-bit Dword EEPROM address can then be entered directly into EEPROM Block Address field in the EEPROM Control register (Port 0 register 260h). The EEPROM command code, which designates the operation to be performed, is entered as the upper 3 bits [15:13] of the 16-bit EEPROM Control register.

#### 5.2.2. To Write 4 Bytes to the Serial EEPROM

- a. Write the 32-bit data into the EEPROM Buffer register at address Port 0 BAR0 + 264h.

- b. Issue a Write Enable instruction (Command = 110b, Set Write Enable Latch), by writing the value 0000C000h into the EEPROM Status and Control register at address Port 0 BAR0 + 260h.

- c. Calculate the combined Address and Command value to write into the EEPROM Control register (lower 16 bits of Port 0 register 260h), by combining the EEPROM 3-bit Write Data instruction, value 010b, as the upper 3 bits of the Word, with the 13-bit EEPROM Dword address obtained from Table A-1 or A-2. In other words, OR the value 4000h with the EEPROM Dword address value obtained from Table A-1 or A-2. The upper Word of the result should be clear. Then write the 32-bit value to register 260h to write register 264h data to the EEPROM.

- d. Issue a Write Disable instruction (Command = 100b, Reset Write Enable Latch), by writing the value 00008000h to register 260h.

- e. **WARNING!** Changing a value in the EEPROM will cause the CRC to be incorrect. Unless the CRC is recalculated and programmed into EEPROM byte address 1E3Ch (Dword address 78Fh), when the PEX 85xx reads the EEPROM to initialize its registers, it will detect the bad CRC and discard the EEPROM values, and instead load the registers with default values (unless Port 0 register 260h bit 21 is set in the EEPROM, which is strongly discouraged).

#### 5.2.3. To Read 4 Bytes from the Serial EEPROM

- a. Calculate the value to write into the EEPROM Control register (lower 16 bits of Port 0 register 260h), by combining the EEPROM 3-bit Read Data instruction, value 011b, as the upper 3 bits of the Word, with the 13-bit EEPROM Dword address obtained from Table A-1 or A-2. In other words, OR the value 6000h with the EEPROM Dword address value obtained from Table A-1 or A-2. The upper Word of the result should be clear. Then, write the 32-bit value to register 260h at Port 0 BAR0 + 260h.

- b. Read the four bytes of EEPROM data from register 264h, at Port 0 BAR0 + 264h.

#### 5.2.4. Reading and Writing EEPROM Status

Bits within the EEPROM Status register can enable write protection for data and/or the EEPROM Status register itself.

For hardware write protection, the serial EEPROM pinout includes the **WP#** (Write Protect) input; when WP# is held low, write operations to the EEPROM Status register are inhibited.

- Bit 31, WPEN, overrides WP# and enables/disables writes to the Status register.

When WP# is high or WPEN = 0, and WEN = 1, the Status register is writable.

When WP# is low and WPEN = 1, or WEN = 0, the Status register is protected.

- Bit 25, WEN, enables/disables writes to Unprotected Blocks of the memory array. When WEN = 0, writes to Unprotected Blocks in memory are disabled. When WEN = 1, writes to Unprotected Blocks in memory are enabled.

- Bits 27:26, BP[1:0], provide write protection for blocks of the memory array. Block Protection options protect the upper ¼, upper ½, or all of the EEPROM. PEX 85xx configuration data is stored in the lower addresses, so when using Block Protection, the entire EEPROM should be protected with BP[1:0] = 11b.

For board manufacturing with a blank EEPROM, the WP# input signal can be always strapped low and EEPROM can still be later initially programmed. Hardware write protection of the data is not enabled until software sets the Block Protection bits BP[1:0], and write protection of the Status register (protection of the BP[1:0] bits) is not enabled until software sets the WPEN bit. If WP# is low, once software sets the WPEN bit to write-protect the EEPROM status register, the WPEN value cannot be changed back to 0, nor can the BP[1:0] bits can be cleared to disable Block Protection. Write protection can be subsequently disabled after WP# is brought high.

Table 2 below summarizes write protection in the serial EEPROM.

| WPEN | WP#  | WEN | Protected<br>Blocks | Unprotected<br>Blocks | Status<br>Register |

|------|------|-----|---------------------|-----------------------|--------------------|

| 0    | Х    | 0   | Protected           | Protected             | Protected          |

| 0    | Х    | 1   | Protected           | Writable              | Writable           |

| 1    | low  | 0   | Protected           | Protected             | Protected          |

| 1    | low  | 1   | Protected           | Writable              | Protected          |

| х    | high | 0   | Protected           | Protected             | Protected          |

| Х    | high | 1   | Protected           | Writable              | Writable           |

Table 2. WPEN, WP# and WEN Operation

WPEN, WEN, and BP[1:0] status can be determined by reading the EEPROM Status register in PEX 85xx Port 0 register 260h bits [31:24]. To copy the EEPROM Status register contents into register 260h bits [31:24], issue a Read Status Register instruction (RDSR, Command = 101b), by writing the value 0000A000h to Port 0 register 260h.

The only writable bits in the EEPROM Status register are WPEN (bit 31) and BP[1:0] (bits [27:26]).

To enable Block Protection, write the following values to Port 0 register 260h:

00006000h (Write Enable) 0C002000h (Write BP[1:0] = 11b) 00008000h (Write Disable)

To disable Block Protection, write the following values to Port 0 register 260h:

00006000h (Write Enable) 00002000h (Write BP[1:0] = 00b) 00008000h (Write Disable)

To enable Block Protection and write protection of the EEPROM status register, write the following values to Port 0 register 260h:

00006000h (Write Enable) 8C002000h (Write BP[1:0] = 11b, WPEN = 1) 00008000h (Write Disable)

The EEPROM does not respond to Command Codes 000b or 111b.

## 5.3. **EEPROM Programming Software**

The PEX SDK includes software that can read and program the serial EEPROM that is connected to the switch. For information and instructions on using this application, please refer to the PEX SDK User's Manual.

# 6. **EEPROM Content**

It is convenient to use the EEPROM image for the PEX 8518RDK, PEX 8517RDK, PEX 8512RDK or PEX 8508RDK, included in the PEX SDK, as the basis for EEPROM content. Then use the PEX SDK GUI included in the PEX SDK to modify the image for the specific application. The following subsections list EEPROM settings that Differ from default registers, as well as other registers and bits that generally need to be evaluated for each specific application.

## 6.1. Silicon Revision

In Revision AB silicon, Revision ID (offset 08h) bit 0 is hardwired to 1.

• If the EEPROM is programmed with the value AAh, reading the register will return the value ABh.

In Revision AC silicon, Revision ID (offset 08h) bits [2:1] are reversed.

- If the EEPROM is programmed with the value AAh, reading the register will return the value ACh.

- If the EEPROM is programmed with the value ABh, reading the register will return the value ADh.

- If the EEPROM is programmed with the value ACh, reading the register will return the value AAh.

## 6.2. Switch Configuration

Modification of the RDK EEPROM image is most likely required in order to set the port configuration to match that defined by the PEX 85xx strapping pins, since these pins may be configured differently from that used in the PEX 85xx RDK. Registers that must be modified are:

1. Port 0 Port Configuration, offset 224h, to set number and width of ports as defined by strapping signals listed in Table 3 below. The EEPROM values overwrite the strapping signal values.

#### Table 3. Port Configuration Register and Corresponding Strapping Signals

| Port Configuration Register<br>(224h) | Default<br>Value | Strapping Signals       |

|---------------------------------------|------------------|-------------------------|

| Port 0                                | 0h               | STRAP_STN0_PORTCFG[4:0] |

Valid Port Configuration Codes are shown in Table 4, Table 5and Table 6 below.

Table 4. PEX 8508 Configuration Codes

| Code        | Port<br>0 | Port<br>1 | Port<br>2 | Port<br>3 | Port<br>4 |

|-------------|-----------|-----------|-----------|-----------|-----------|

| 0,1,7,10-31 | x2        | x2        | x2        | x2        |           |

| 2           | x4        | x4        |           |           |           |

| 3           | x4        | x2        | x2        |           |           |

| 4           | x4        | x2        | x1        | x1        |           |

| 5           | x4        | x1        | x1        | x2        |           |

| 6           | x4        | x1        | x2        | x1        |           |

| 8           | x4        | x1        | x1        | x1        | x1        |

| 9           | x2        | x2        | x2        | x1        | x1        |

Table 5. PEX 8512 Configuration Codes

| Code | Port<br>0 | Port<br>1 | Port<br>2 | Port<br>3 | Port<br>4 |

|------|-----------|-----------|-----------|-----------|-----------|

| 3    | x4        | x4        | x4        |           |           |

| 8    | x4        | x2        | x2        | x2        | x2        |

Table 6. PEX 8517 and PEX 8518 Configuration Codes

| Code        | Port<br>0 | Port<br>1 | Port<br>2 | Port<br>3 | Port<br>4 |

|-------------|-----------|-----------|-----------|-----------|-----------|

| 0,1,7,10-31 | x4        | x4        | x4        | x4        |           |

| 2           | x8        | x8        |           |           |           |

| 3           | x8        | x4        | x4        |           |           |

| 4           | x8        | x4        | x2        | x2        |           |

| 5           | x8        | x2        | x2        | x4        |           |

| 6           | x8        | x2        | x4        | x2        |           |

| 8           | x8        | x2        | x2        | x2        | x2        |

| 9           | x4        | x4        | x4        | x2        | x2        |

2. Port 0 can be forced to train to x1 (rather than the width configured by register 224h), by setting Port 0 offset 228h bit 2, as shown in Table 7 below.

Table 7. Physical Layer Test Register (Offset 228h in Port 0)

| Bit | Bit Field<br>Name | Default<br>Value | Value                                                                                                 |

|-----|-------------------|------------------|-------------------------------------------------------------------------------------------------------|

| 2   | Port_0_X1         | 0                | <ul><li>1 = Port 0 is configured as x1 only</li><li>0 = Port 0 is not forced to train as x1</li></ul> |

Setting this bit does not result in any additional power savings on unused SerDes.

Port 0 Debug Control, offset 1DCh, to select Transparent or Non-Transparent mode, one upstream port, and a single NT port (if Intelligent Adapter or Dual Host NT modes are enabled). The EEPROM values for the bit fields in register 1DCh overwrite the corresponding strapping signals, as listed in Table 8 below.

Table 8. Debug Control Register Bits and Corresponding Strapping Signals

| Debug Control (1DCh) bits   | Strapping Signals             |

|-----------------------------|-------------------------------|

| Upstream Port Number [10:8] | STRAP_UPSTRM_PORT_SEL[2:0]    |

| Mode Select [19:18]         | STRAP_MODE_SEL[1:0]           |

| NT-Port Number [27:24]      | STRAP_NT_UPSTRM_PORT_SEL[3:0] |

## 6.2.1. Changing the Switch Configuration

Changing the switch configuration (Ports 0 register 224h, number and/or width of ports) generally requires changes to additional register values in the EEPROM:

- 1. Port offset 160h, VC0 Resource Status register bits [17, 1]. Refer to Section 6.6.

- 2. Port offset 1F8h, ACK Transmission Latency Limit register bits [7:0]. Refer to Section 6.7.

- 3. Port offset 1F8h, Replay Timer Limit register bits [23:16]. Refer to Section 6.8.

- 4. Port 0 offset 668h, TIC Port Enable register bits [12:8, 3:0]. Refer to Section 6.9.

- 5. Port 0 offsets C00h[15:0] and C04h[31:16], ITCH VCnT Threshold registers. Refer to Section 6.10.

#### 6.2.2. Changing the Upstream Port

Changing the designated upstream port (Port 0 register 1DCh bits [10:8]) generally requires changes to additional registers in the EEPROM:

- 1. Port offset 68h, PCI Express Capabilities register. Refer to Section 6.3 below.

- a. Device / Port Type, bits [23:20].

- b. Slot Implemented, bit 24.

- 2. Port offset 7Ch, Slot Capabilities register. Refer to Section 6.5.2 below.

# 6.3. Port Configuration

Each configured port's PCI Express Capabilities register, at offset 68h, may need to be modified depending upon whether a port other than 0 is defined as the upstream port, and whether downstream ports are connected to a device rather than a slot. Refer to Table 9 below.

| Bits  | Bit Field Name                                | Default<br>Value                 | Value                                                                                                                                                                                           |

|-------|-----------------------------------------------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |                                               | Upstream<br>5                    | Upstream port = 5h<br>Downstream transparent port = 6h<br>Non-Transparent port (NT-Virtual & NT-Link):<br>Legacy PCI Express Endpoint                                                           |

| 23:20 | Device / Port Downstream<br>Type 6<br>NT<br>0 | Downstream<br>6                  | <ul> <li>(I/O BAR1 required) = 1h</li> <li>PCI Express Endpoint</li> <li>(I/O BAR1 not required,</li> <li>OS can close I/O space) = 0h</li> <li>Note: BAR1 is enabled as default, in</li> </ul> |

|       |                                               | _                                | registers:<br>NT-Virtual: BAR1 Setup D0h<br>BAR1 Setup Shadow D80h<br>NT-Link: BAR Setup E4h                                                                                                    |

| 24    | Slot<br>Implemented                           | Upstream<br>1<br>Downstream<br>0 | Upstream and NT ports (not programmable) = 0<br>Downstream transparent port:<br>1 if Slot<br>0 if Device, or configured port is disabled                                                        |

Table 9. PCI Express Capabilities Register (Offset 68h in All Ports)

# 6.4. RefClk Source

Link Status and Control register (78h) includes the Slot Clock Configuration bit that defines whether the upstream port, each downstream port, and the NT-Link port share a common clock source with the device at the other end of each link. Refer to Table 10 below.

| Bit | Bit Field Name              | Default<br>Value                         | Value                                                                                                                                                                  |

|-----|-----------------------------|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 28  | Slot Clock<br>Configuration | Upstream<br>& NT<br>0<br>Downstream<br>1 | <ul> <li>1 = RefClk to PEX 85xx and RefClk at connector are from a common source.</li> <li>0 = RefClk to PEX 85xx and RefClk at connector are asynchronous.</li> </ul> |

Table 10. Link Status and Control Register (Offset 78h in All Ports)

Since PEX 85xx Active State Power Management (ASPM) should remain disabled (78h[1:0] = 00b) due to errata, the L0s Exit Latency and N\_FTS values, which can normally be reduced if the RefClk to all devices is synchronous, should remain the default values.

# 6.5. Hot Plug Signals

## 6.5.1. Upstream and NT-Link Ports

The PEX 85xx Upstream and NT ports are Hot Plug clients; Hot Plug signals associated with these ports are not used.

#### 6.5.2. Downstream Transparent Ports

The PEX 85xx provides 9 Hot Plug signals for each downstream transparent port. The Hot Plug Controller in a downstream transparent port is enabled if the Power Controller Present bit in the Slot Capabilities register for that port is set (7Ch bit 1 = 1). This register also defines whether Hot Plug is supported by a PCle slot, which Hot Plug signals are used by that port, Power Limits for slots connected to downstream transparent ports, and the Physical Slot Number assigned for physical slots that connect downstream transparent ports. Refer to Table 11 and Table 12 below.

| Inputs     | Slot Capabilities (7Ch)<br>Register Enable Bit | Functionality                                                                                                                |

|------------|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| HP_BUTTON# | 0                                              | Attention Button                                                                                                             |

| HP_MRL#    | 2                                              | Manually operated Retention<br>Latch Sensor                                                                                  |

| HP_PRSNT#  |                                                | Presence Detect<br>Register 1E0h bit 5 controls<br>whether Presence is detected<br>by HP_PRSNT# or SerDes<br>Receiver Detect |

| HP_PWRFLT# |                                                | Power Fault                                                                                                                  |

| Outputs    |                                                |                                                                                                                              |

| HP_ATNLED# | 3                                              | Attention Indicator                                                                                                          |

| HP_CLKEN#  | 1                                              | Power Controller Present                                                                                                     |

| HP_PERST#  |                                                | Reset output                                                                                                                 |

| HP_PWREN#  | 1                                              | Power Controller Present                                                                                                     |

| HP_PWRLED# | 4                                              | Power Indicator Present                                                                                                      |

| Table 11. Downstream | <b>Transparent Port Hot</b> | Plug Signals |

|----------------------|-----------------------------|--------------|

|----------------------|-----------------------------|--------------|

# Table 12. Slot Capabilities Register (7Ch, Exists Only in Transparent Ports),Valid Only for Downstream Transparent Ports)

| Bits  | Bit Field Name Default Value |                                     | Value                                                                                                                                                                                        |

|-------|------------------------------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5     | Hot Plug<br>Surprise         | Upstream<br>0<br>Downstream<br>1    | <ul> <li>Downstream Transparent port value:</li> <li>0 if Slot does not support removal without prior notification</li> <li>1 if Slot supports removal without prior notification</li> </ul> |

| 6     | Hot Plug<br>Capable          | Upstream<br>0<br>Downstream<br>1    | Downstream Transparent port value:<br>0 if Device, or Slot does not support Hot Plug<br>1 if Slot supports Hot Plug                                                                          |

| 14:7  | Slot Power Limit<br>Value    | Upstream<br>0h<br>Downstream<br>19h | If Slot Implemented bit is set,<br>Downstream transparent port value is<br>Max power (25W = 19h)                                                                                             |

| 16:15 | Slot Power Limit<br>Scale    | 00b                                 | If Slot Implemented bit is set,<br>Downstream transparent port value is<br>00=1.0, 01=0.1, 10=0.01, 11=.001                                                                                  |

| 31:19 | Physical Slot<br>Number      | 0h                                  | Downstream Transparent port value:<br>System unique non-zero value                                                                                                                           |

If the Hot Plug Controller is enabled in a downstream transparent port, output signal timing must also be defined in that port's Power Management Hot Plug User Configuration register (1E0h). Refer to Table 13 below.

#### Table 13. Hot Plug Controller

| Slot Capabilities Register (7Ch)<br>Power Controller Present Bit (1) | Default<br>Value | Hot Plug Controller                                                                                                                                                                                                                                                                                                                                                             |

|----------------------------------------------------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0                                                                    |                  | Disabled                                                                                                                                                                                                                                                                                                                                                                        |

| 1                                                                    | 1                | <ul> <li>Enabled</li> <li>1. Set delay from power-applied to power-valid (TPEPV, 1E0h bits [4:3]) <ul> <li>delay from when HP_PWREN# and HP_PWRLED# outputs assert after PERST# input assertion, until HP_CLKEN# output is asserted.</li> </ul> </li> <li>2. Set delay from power-valid (HP_CLKEN# asserted) to HP_PERST# output de-assertion (TPVPERL), 1E0h bit 6)</li> </ul> |

#### 6.5.3. Downstream Transparent Port HP\_PERST# (Reset) Output

Whether HP\_PERST# output is de-asserted is controlled by the Power Controller Control bit (Slot Control Register (80h) bit 10).

1. If the Hot Plug Controller is enabled (Power Controller Present, 7Ch bit 1 = 1 (default without EEPROM, or programmable only by EEPROM)), and if the Power Controller Control bit is clear (80h bit 10 = 0):

HP\_PERST# output de-asserts after TPVPERL delay (1E0h bit 6, 20 ms or 100 ms default) after power is valid at the slot (HP\_CLKEN# asserted). Power is valid at the slot (HP\_PWREN# and HP\_PWRLED# (if enabled) outputs are asserted), after TPEPV delay (1E0h bits [4:3]) following completion of the EEPROM load. If HP\_MRL# input is enabled (7Ch bit 2 = 1 (default without EEPROM, or programmable only by EEPROM)), the Hot Plug power up sequence ending with HP\_PERST# de-assertion does not start until HP\_MRL# is low (following 10 ms de-bounce).

- 2. If the Hot Plug Controller is enabled (Power Controller Present, 7Ch bit 1 = 1), and the Power Controller Control bit is set (80h bit 10 = 1), HP\_PERST# output is not de-asserted.

- 3. If the Hot Plug Controller is disabled (Power Controller Present, 7Ch bit 1 = 0 (programmable only by EEPROM)), and the following conditions are true:

- The Power Controller Control bit is clear (80h bit 10 = 0)

- HP\_MRL# is disabled (7Ch bit 2 = 0 (programmable only by EEPROM)) or if HP\_MRL# is enabled (7Ch bit 2 = 1 (default without EEPROM, or programmable only by EEPROM)) with HP\_MRL# input asserted, then HP\_PERST# output de-asserts immediately after the EEPROM load.

Otherwise, HP\_PERST# output remains de-asserted.

HP\_PERST# can also be toggled at runtime by toggling the Power Controller Control bit (80h bit 10), provided HP\_PERST# initially de-asserts under one of the conditions listed above. Value of 1 asserts HP\_PERST# (low) and value of 0 de-asserts HP\_PERST# (high).

# 6.6. VC0 Negotiation Pending bit (All Ports, Offset 160h Bit [17])

The VC0 Negotiation Pending bit in each enabled port (as defined by Port 0 register 224h) must be set in the programmed EEPROM.

Software must first check that the VC0 Negotiation Pending bit in the Virtual Channel Extended Capability registers of each successive device in the link path is cleared (indicating link flow control initialization has completed), prior to attempting to access the device at the other end of the link.

# 6.7. ACK Transmission Latency Limit (All Ports, Offset 1F8h Bits [7:0])

The ACK Transmission Latency Limit register places a minimum amount of time (in clocks) that the switch port waits before prioritizing an ACK transmission.

Set the ACK Transmission Latency Limit in each transparent port, and in the NT-Virtual port. Recommended values for the ACK Transmission Latency Limit are based upon port width and Maximum Payload Size (128 or 256 bytes, as determined offset 70h bits [7:5]), as shown in Table 14 below.

| Maximum      | Port Width |     |     |     |  |  |

|--------------|------------|-----|-----|-----|--|--|

| Payload Size | x1         | x2  | x4  | x8  |  |  |

| 128B         | FAh        | 80h | 49h | 43h |  |  |

| 256B         | FFh        | D9h | 76h | 6Bh |  |  |

Table 14. ACK Transmission Latency Limit, 1F8h [7:0]

If the recommended value is increased, there is greater chance of ACK collapsing, which can increase egress TLP throughput since ACK DLLP traffic is reduced. However, increasing the register value could slow ingress TLP throughput if the Replay buffer in the external device is not sufficiently deep to prevent it from throttling TLP transmission while waiting for an ACK.

For the NT-Virtual port width, use the port width of the NT-Link port. For example, if the NT-Link port width is x4 and Maximum Payload Size (70h[7:5]) is 128 bytes, set the NT-Virtual value to the x4 value 49h. The ACK Latency Timer value in the NT-Link port can remain at its default value 0h.

## 6.8. Replay Timer Limit, Upper 8 Bits (All Ports, Offset 1F8h Bits [23:16])

If a port's Transmit Retry Buffer contains TLPs for which no ACK or NAK has been received for a time period exceeding the programmed value of the Replay timer, the switch port's transmitter initiates a replay.

Set the Replay Timer Limit in each transparent port, and in the NT-Virtual port if Non-Transparent mode is enabled (in Port 0 register 1DCh bits [19:18]). Recommended values for the Replay Timer Limit are based upon link width and are calculated for Maximum Payload Size of 256 bytes; the same value should be used for Maximum Payload Size of 128 bytes (due to timer tolerance). Refer to Table 15 below.

#### Table 15. Replay Timer Limit, 1F8h [23:16]

| Link Width  |     |     |     |  |  |

|-------------|-----|-----|-----|--|--|

| x1 x2 x4 x8 |     |     |     |  |  |

| 05h         | 03h | 02h | 02h |  |  |

For the NT port width, use the link width of the NT-Link port. For example, if the NT-Link port width is x4, set the NT-Virtual value to the x4 value, 02h. The Retry Timer Limit value in the NT-Link port can remain at its default value FFh.

# 6.9. TIC Control Register (Port 0 Offset 668h)

When a programmed EEPROM is present, the TIC Control register is loaded from EEPROM. The value indicates which ports are enabled (even if unused), as defined by Port 0 register 224h. To determine the value, start with FFFF\_0000h, and then set the bit positions that correspond to enabled ports. For example, if Ports 0, 1 and 2 are enabled, the correct value is FFFF\_0007h. Refer to Table 16 below.

| Port<br>Configuration   | Number of<br>Enabled Ports | TIC Control             |

|-------------------------|----------------------------|-------------------------|

| Port 0<br>Register 224h |                            | Port 0<br>Register 668h |

| 0,1,4-7,10-31           | 4                          | FFFF000Fh               |

| 2                       | 2                          | FFFF0003h               |

| 3                       | 3                          | FFFF0007h               |

| 8,9                     | 5                          | FFFF001Fh               |

Table 16. TIC Control Register (Offset 668h in Port 0)

The number of enabled ports is normally the same as the value of the Number of Ports Enumerated register value (Port 0 register 220h bits [22:20]), which is automatically updated by the switch after reset.

## 6.10. INCH Threshold Port Virtual Channel Registers (Port 0 Offsets A00h–A68h)

#### 6.10.1. Flow Control Initialization Credits

With respect to system performance, of all register values, the Ingress Credits that are advertised to other devices can have the greatest impact.

The Station contains an Ingress Packet RAM of 1024 rows x 5 DW columns, which can be allocated among up to 5 enabled ports in the Station. Each packet requires 1 Header Credit, which allocates up to 5 DW of which 3 or 4 DW are for the packet header, and 1 DW is for the ECRC (if enabled).

Port 0 can be allocated a maximum of 32 Header Credits, for Posted, Non-Posted, and Completion transactions, for both Virtual Channels (VC0 and VC1). Credits for Posted, Non-Posted, and Completion transactions can be assigned different values for Virtual Channel 0 (VC0) and Virtual Channel 1 (VC1); however, the sum of all Header Credits for VC0 and VC1 together must not exceed the maximum value of 32 Header Credits.

Ports 1 and 2 can each be allocated a maximum of 24 Header Credits, for Posted, Non-Posted, and Completion transactions, for both Virtual Channels (VC0 and VC1). Credits for Posted, Non-Posted, and Completion transactions can be assigned different values for Virtual Channel 0 (VC0) and Virtual Channel 1 (VC1); however, the sum of all Header Credits for VC0 and VC1 together must not exceed the maximum value of 24 Header Credits per port.

Ports 3 and 4 can each be allocated a maximum of 16 Header Credits, for Posted, Non-Posted, and Completion transactions, for VC0 only (VC1 is not supported on Ports 3 and 4). The sum of all VC0 Header Credits for Ports 3 and 4 must not exceed the maximum value of 16 Header Credits per port.

Each Payload Credit corresponds to 16 bytes of data. Enough Payload Credits should be assigned for each header to accommodate the maximum packet size for each transaction type. Each Non-Posted transaction carries a maximum payload of 4 bytes. Posted and Completion Header Credit should be assigned at least the number of Payload Credits required to accommodate the Maximum Payload Size used in the system.

[The Maximum Payload Size (Device Control register, offset 70h bits [7:5],) is programmed by software to the lowest value of Maximum Payload Size Supported (Device Capability register, offset 6Ch bits [2:0],) among all devices in the system. The value 000b indicates 128 bytes, and the value 001b indicates 256 bytes.]

Headers can only occupy the first column of the Packet RAM. The Payload data immediately follows the 3- or 4-Dword header, on the same row of RAM and on successive row(s) if the row containing the header fills up. If ECRC is enabled, the 1-Dword ECRC immediately follows the Payload data. Any remaining empty space in a row following the Payload and/or ECRC is unused. The number of rows of RAM that a packet will occupy is calculated by dividing the sum of the number of bytes in the header, payload, and ECRC (if enabled), by 20; if the result includes any non-integral remainder, increment the quotient.

For example, each Memory Read (Non-Posted, without data) packet occupies one row of the Packet RAM. A Posted or Completion packet having a 64-byte payload and 3 DW header (or a 4 DW header and no ECRC) occupies four rows of the Packet RAM. A Posted or Completion packet having a 3 DW header, 128-byte payload and no ECRC will occupy seven rows of RAM (8 rows if the header is 4 DW and/or if ECRC is enabled). A packet with a 256-byte payload will occupy fourteen rows of RAM.

Payload Credits can be calculated to include only the Payload Data, or alternatively to include any unused RAM in the remainder of a row. The number of Payload Credits is programmed into the lowest 9 bits ([8:0]) of each Ingress Credit (INCH) register; the number of Payload Credits for Posted and Completion packets is always a multiple of 8, since the lowest three bits ([2:0]) of the Posted and Completion registers are *Reserved*.

Table 17 below lists the maximum effective value for Payload Credits, for combinations of selected Header Credits and Maximum Payload Size.

|     | eaders   |     | Max | kimum P | ayload | Size |     |

|-----|----------|-----|-----|---------|--------|------|-----|

|     | eauers   | 4   | 4   | 128     |        | 256  |     |

| dec | hex << 9 | dec | hex | dec     | hex    | dec  | hex |

| 1   | 0200     | 1   | 01  | 8       | 08     | 16   | 10  |

| 2   | 0400     | 2   | 02  | 16      | 10     | 32   | 20  |

| 3   | 0600     | 3   | 03  | 24      | 18     | 48   | 30  |

| 4   | 0800     | 4   | 04  | 32      | 20     | 64   | 40  |

| 5   | 0A00     | 5   | 05  | 40      | 28     | 80   | 50  |

| 6   | 0000     | 6   | 06  | 48      | 30     | 96   | 60  |

| 7   | 0E00     | 7   | 07  | 56      | 38     | 112  | 70  |

| 8   | 1000     | 8   | 08  | 64      | 40     | 128  | 80  |

| 9   | 1200     | 9   | 09  | 72      | 48     | 144  | 90  |

| 10  | 1400     | 10  | 0A  | 80      | 50     | 160  | A0  |

| 11  | 1600     | 11  | 0B  | 88      | 58     | 176  | B0  |

| 12  | 1800     | 12  | 0C  | 96      | 60     | 192  | C0  |

| 13  | 1A00     | 13  | 0D  | 104     | 68     | 208  | D0  |

| 14  | 1C00     | 14  | 0E  | 112     | 70     | 224  | ΕO  |

| 15  | 1E00     | 15  | 0F  | 120     | 78     | 240  | FO  |

| 16  | 2000     | 16  | 10  | 128     | 80     | 256  | 100 |

| 17  | 2200     | 17  | 11  | 136     | 88     | 272  | 110 |

| 18  | 2400     | 18  | 12  | 144     | 90     | 288  | 120 |

| 19  | 2600     | 19  | 13  | 152     | 98     | 304  | 130 |

| 20  | 2800     | 20  | 14  | 160     | A0     | 320  | 140 |

| 21  | 2A00     | 21  | 15  | 168     | A8     | 336  | 150 |

| 22  | 2C00     | 22  | 16  | 176     | B0     | 352  | 160 |

| 23  | 2E00     | 23  | 17  | 184     | B8     | 368  | 170 |

| 24  | 3000     | 24  | 18  | 192     | CO     | 384  | 180 |

| 25  | 3200     | 25  | 19  | 200     | C8     | 400  | 190 |

| 26  | 3400     | 26  | 1A  | 208     | D0     | 416  | 1A0 |

| 27  | 3600     | 27  | 1B  | 216     | D8     | 432  | 1B0 |

| 28  | 3800     | 28  | 1C  | 224     | E0     | 448  | 1C0 |

| 29  | 3A00     | 29  | 1D  | 232     | E8     | 464  | 1D0 |

| 30  | 3C00     | 30  | 1E  | 240     | FO     | 480  | 1E0 |

Table 17. Effective Maximum Payload Credits for Header Credits and Payload Sizes

INCH Threshold register values can be calculated by ORing the "hex << 9" column with the value in the appropriate "hex" column (the "4" column for Non-Posted, and the "128" or "256" hex column (as appropriate) for Posted and Completion transaction types.

Ingress Credits for the PEX 85xx RDK EEPROMs are programmed to the default values listed in the PEX 85xx Data Books. The Ingress Credit registers for Port 0 contain one set of default values, the Ingress Credit registers for Ports 1 and 2 share a different set of default values, and the Ingress Credit registers for Ports 3 and 4 share yet another different set of default values. Ingress Credits for the PEX 85xx RDK EEPROMs are programmed to the default register values shown in Table 18,

Table 19 and Table 20 below.

|                | Headers |     | Pay | load | Register Value |

|----------------|---------|-----|-----|------|----------------|

|                | dec     | hex | dec | hex  | hex            |

| VC0 Posted     | 12      | С   | 120 | 78   | 1878           |

| VC0 Non-Posted | 7       | 7   | 7   | 7    | 0E07           |

| VC0 Completion | 10      | А   | 104 | 68   | 1468           |

| VC1 Posted     | 1       | 1   | 16  | 10   | 0210           |

| VC1 Non-Posted | 1       | 1   | 1   | 1    | 0201           |

| VC1 Completion | 1       | 1   | 16  | 10   | 0210           |

| Total          | 32      |     | 263 |      |                |

#### Table 18. PEX 85xx Default Ingress Credit Values for Port 0

#### Table 19. PEX 85xx Default Ingress Credit Values for Ports 1 and 2

|                | Headers |     | Pay | load | Register Value |

|----------------|---------|-----|-----|------|----------------|

|                | dec     | hex | dec | hex  | hex            |

| VC0 Posted     | 9       | 9   | 88  | 58   | 1258           |

| VC0 Non-Posted | 5       | 5   | 5   | 5    | 0A05           |

| VC0 Completion | 7       | 7   | 72  | 48   | 0E48           |

| VC1 Posted     | 1       | 1   | 16  | 10   | 0210           |

| VC1 Non-Posted | 1       | 1   | 1   | 1    | 0201           |

| VC1 Completion | 1       | 1   | 16  | 10   | 0210           |

| Total          | 24      |     | 198 |      |                |

#### Table 20. PEX 85xx Default Ingress Credit Values for Ports 3 and 4

|                | Headers |     | Pay | load | Register Value |

|----------------|---------|-----|-----|------|----------------|

|                | dec     | hex | dec | hex  | hex            |

| VC0 Posted     | 6       | 6   | 64  | 40   | 0C40           |

| VC0 Non-Posted | 4       | 4   | 4   | 4    | 0804           |

| VC0 Completion | 6       | 6   | 56  | 38   | 0C38           |

| Total          | 16      |     | 124 |      |                |

These values are selected for a mixture of packet types moving across the link, with all credits allocated to VC0 (since the concept of multiple Virtual Channels requires a system (hardware and software) solution and current systems have not implemented multiple VCs).

Credit values can be modified for optimization of the types of traffic in a system. For example, if all transactions to Port 0 are Posted, then credits could be changed (in the EEPROM) to 30 Posted header credits, 1 Non-Posted header credit, and 1 Completion header credit. A minimum of 1 Header Credit must always be allocated for each of VC0 Posted, VC0 Non-Posted, and VC0 Completion packets, along with the minimum number of Payload Credits to accommodate at least 1 packet carrying the Maximum Payload Size for each of the three packet types.

While the Ingress Packet RAM is large, it is possible to allocate more credits than the RAM can hold. In a working system, even though packets are continually being emptied from the Ingress Packet RAM to the Egress Packet RAM, the number of programmed credits for all ports should not be allowed to exceed the amount of Packet RAM, otherwise there is a potential for the RAM to overflow. The RAM will not overflow if all five ports are enabled and default Ingress Credit values are used.

# 6.11. Internal Credit Handler VCnT Threshold Registers (Port 0 Offsets C00h–C08h)

The ITCH VCnT Threshold registers define internal credits between the egress queue of one port and the ingress queues of ingress ports. The ITCH VCnT Threshold registers are programmed in the EEPROM with values to prevent filling of the Egress RAM with Posted packets, which might prevent Completion packets from making forward progress from the ingress queue to the egress queue inside the switch. The programmed values apply to all ports in the Station. While separate registers exist for Posted, Non-Posted and Completion packet counts, programming only the registers for Posted counts will prevent clogging of the Egress RAM for any combination of packets.

Recommended register values are based upon the number of ports enabled in the Station (as configured in Port 0 register 224h). A port is considered as enabled even if it is unused. The number of enabled ports is normally the same as the value of the Number of Ports Enumerated register value (Port 0 register 220h bits [22:20]), which is automatically updated by the switch after reset.

Recommended values for the VC0 Posted Lower and Upper Packet Count registers, based upon the number of enabled ports and only VC0 enabled, are listed in Table 21 below.

|   | Ports | 224h<br>Value | Destination<br>RAM Entries | VC0 Posted<br>Lower Packet<br>Count<br>C00h[15:8] | VC0 Posted<br>Upper Packet<br>Count<br>C00h[7:0] |

|---|-------|---------------|----------------------------|---------------------------------------------------|--------------------------------------------------|

|   | 2     | 2             | 256-256                    | 8Ch                                               | DCh                                              |

|   | 3     | 3             | 250-131-131                | 46h                                               | 62h                                              |

|   | 4     | 0,4,5,6       | 152-120-120-120            | 46h                                               | 62h                                              |

| I | 5     | 8,9           | 120-100-100-96-96          | 2Ah                                               | 46h                                              |

#### Table 21. ITCH VCnT VC0 Posted Packet Count, for One VC Enabled (VC0 only)

Recommended values for the VC0 and VC1 Posted Lower and Upper Packet Count registers, based upon the number of enabled ports, with both VC0 and VC1 enabled, are listed in Table 22 and Table 23 below.

Note: It is not recommended to use two VCs with 5 ports enabled, due to inefficient RAM utilization in this configuration.

#### Table 22. ITCH VCnT VC0 Posted Packet Count, for Two VCs Enabled

| Ports | 224h<br>Value | Destination<br>RAM Entries | VC0 Posted<br>Lower Packet<br>Count<br>C00h[15:8] | VC0 Posted<br>Upper Packet<br>Count<br>C00h[7:0] |  |

|-------|---------------|----------------------------|---------------------------------------------------|--------------------------------------------------|--|

| 2     | 2             | 256-256                    | 54h                                               | 8Ch                                              |  |

| 3     | 3             | 250-131-131                | 1Ch                                               | 3Fh                                              |  |

| 4     | 0,4,5,6       | 152-120-120-120            | 1Ch                                               | 38h                                              |  |

| 5     | 8,9           | 120-100-100-96-96          | 1Ch                                               | 2Ah                                              |  |

|   | Ports | 224h<br>Value | Destination<br>RAM Entries | VC1 Posted<br>Lower Packet<br>Count<br>C04h[31:24] | VC1 Posted<br>Upper Packet<br>Count<br>C04h[23:16] |  |

|---|-------|---------------|----------------------------|----------------------------------------------------|----------------------------------------------------|--|

|   | 2     | 2             | 256-256                    | 2Ah                                                | 46h                                                |  |

| ſ | 3     | 3             | 250-131-131                | 14h                                                | 2Ah                                                |  |

|   | 4     | 0,4,5,6       | 152-120-120-120            | 14h                                                | 2Ah                                                |  |

| I | 5     | 8,9           | 120-100-100-96-96          | 12h                                                | 22h                                                |  |

Table 23. ITCH VCnT VC1 Posted Packet Count, for Two VCs Enabled

# 6.12. SerDes Electrical Characteristics

SerDes Electrical Characteristics are programmed in Port 0 register addresses 248h - 258h of the PEX 85xx RDKs. The values are chip-specific and tuned to meet PCI-SIG amplitude and de-emphasis specifications with VTT = 1.5V. Other values can be programmed based upon oscilloscopic eye patterns measured for the particular design.

# 6.13. Non-Transparent Mode Registers

#### 6.13.1. Device/Vendor ID, Subsystem ID and Subsystem Vendor ID

Some operating systems might require that the non-transparent bridges (NT-Virtual and NT-Link), which utilize device drivers, have different Vendor/Device IDs from that of the Transparent mode bridges (upstream and downstream transparent ports), which normally use a system driver included in the operating system.

Besides the Vendor/Device ID, the NT ports include a Subsystem ID and Subsystem Vendor ID. Normally the Vendor/Device ID identify the interface chip (the PLX switch), and the Subsystem ID and Subsystem Vendor ID identify the board. Therefore, normally the Vendor/Device ID in the NT ports should contain the default register values. This scheme allows a generic driver associated only with the Device/Vendor ID to be used with the board, or a specific driver associated with the Device/Vendor ID as well as the Subsystem and Subsystem Vendor ID to be used for the specific functionality and software developed for the board design. The Subsystem Vendor ID value must be a valid Vendor ID assigned to PCI-SIG members. If the board vendor is a member of PCI-SIG and uses it own Vendor ID, the company can freely assign its own Subsystem ID(s) to identify the board.

However, in the case of the NT-Link port, if the NT-Link interface receives a Hot Reset or its link goes down, the NT-Link registers are reset, and consequently the NT-Link registers containing the Device ID, Vendor ID, Subsystem ID and Subsystem Vendor ID are reset to PLX default values, and the EEPROM is not reloaded. Therefore, it is recommended that the NT Link Device ID, Vendor ID, Subsystem ID and Subsystem Vendor ID values remain PLX default values. In contrast, if the upstream port receives a Hot Reset or its link goes down, the transparent ports and NT-Virtual port registers are reset (unless Port 0 offset 1DCh[20] is set to disable such resets), and the EEPROM is reloaded (unless Port 0 offset 1DCh[17 or 16] is set).

Consequently, if the OS requires different Device/Vendor ID values for Transparent and Non-Transparent ports, it is recommended to change the value in the Transparent ports rather than the Non-Transparent ports.

The Subsystem IDs for the NT-Virtual and NT-Link ports can be the same value, or different values. Different Subsystem IDs might be desirable because the register sets for the NT-Virtual and NT-Link ports are different, and different software drivers for the two ports might be utilized.

If a company is not a member of PCI-SIG, PLX can assign, at no cost, Device ID(s) or Subsystem ID(s) for the product. In this case, the Vendor ID and Subsystem Vendor ID remain the default PLX value, 10B5h.

#### 6.13.2. NT-Virtual BAR Setup and BAR Setup Shadow Registers

The BAR Setup (D4h-E0h) and corresponding BAR Setup Shadow (D84h-D90h) register pairs (for BARs 2-5) both need to be programmed prior to enabling NT-Virtual BIOS/OS configuration access to the NT-Virtual BAR registers, and therefore typically the BAR Setup and BAR Setup Shadow registers are both programmed by EEPROM (to the same value). Address space size must be a power of 2, and the corresponding size value to program into the BAR Setup and Shadow registers and enable the corresponding NT-Virtual BAR registers must be the two's complement of the address space size.

#### **NT-Virtual BARs:**

- BAR1 is an I/O BAR and is enabled as default in BAR1 Setup (D0h) and BAR1 Setup Shadow (D80h) registers. BAR1 should be disabled to conserve limited I/O resources, as recommended by the PCI Express Base Specification.

- BAR2 is a 32-bit memory BAR; minimum BAR size is 4 KB.

- BAR3 is a 32-bit memory BAR that uses a Look-Up Table (LUT) with 60 entries for individual address translation for each page. Page Size is programmable from 4 KB to 32 MB, corresponding to BAR3 sizes of 256 KB to 2 GB, respectively. LUT entries 30, 31, 32, and 33 are not available for use when a programmed EEPROM is used, and must be programmed to the same values as the NT-Virtual BAR Setup registers 2 through 5 (D4h through E0h), respectively.

- The BAR 4/5 group provides a 64-bit memory BAR; minimum BAR size is 4 KB. BAR4 can be used alone as a 32-bit BAR, in which case BAR5 is *reserved*.

While BAR Setup (and Shadow) registers are typically programmed by EEPROM, in certain applications it is possible that NT-Link host software can program the NT-Virtual BAR Setup and Shadow registers (the NT-Virtual register addresses are offset from NT-Link BAR0). If software, rather than the EEPROM, programs the BAR Setup and Shadow registers, the Virtual Interface Access Enable bit (Port 0 register 1DCh bit 28) should be initially disabled (0), to prevent enumeration of the NT-Virtual BAR registers from occurring until after the BAR Setup registers are programmed. After the BAR Setup registers are programmed. After the BAR Setup registers are programmed, the Virtual Interface Access Enable bit should be set to allow NT-Virtual domain software to perform Type 0 accesses to configure the NT-Virtual BAR registers. Until this bit is set, Type 0 accesses to the NT-Virtual registers are retried (Completion with Completion Status Code set to Configuration Request Retry Status (CRS)). The Virtual Interface Access Enable bit default value is 1 if the EEPROM is not present, and otherwise 0.

## 6.13.3. NT-Link BAR Setup Registers

The BAR Setup registers (E8h-F4h) for BARs 2-5 need to be programmed prior to BIOS/OS configuration of the NT-Link BAR registers, and therefore typically the BARS are programmed by EEPROM. Address space size must be a power of 2, and the corresponding size value to program into the BAR Setup registers and enable the corresponding NT-Link BAR registers must be the two's complement of the address space size.

#### NT-Link BARs:

- BAR1 is an I/O BAR and is enabled as default in the BAR0/BAR1 Setup register (E4h). BAR1 can be disabled to conserve limited I/O resources.

- The BAR 2/3 group provides a 64-bit memory BAR; minimum BAR size is 4 KB. BAR2 can be used alone as a 32-bit BAR, in which case BAR3 is *reserved*.

- The BAR 4/5 group provides a 64-bit memory BAR; minimum BAR size is 4 KB. BAR4 can be used alone as a 32-bit BAR, in which case BAR5 is *reserved*.

While BAR Setup registers are typically programmed by EEPROM, in certain applications it is possible that NT-Virtual host software can program the NT-Link BAR Setup registers (the NT-Link register addresses are offset from Upstream Port BAR0); if software rather than the EEPROM programs the BAR Setup registers, the Link Interface Access Enable bit (Port 0 register 1DCh bit 29) should be initially disabled, to prevent enumeration of the NT-Link BAR registers from occurring until after the BAR Setup registers are programmed. After the BAR Setup registers are programmed, the Link Interface Access Enable bit should be set to allow NT-Link domain software to perform Type 0 accesses to configure the NT-Link BAR registers. Until this bit is set, Type 0 accesses in Intelligent Adapter mode are retried, and in Dual-Host mode, aborted. The Link Interface Access Enable bit default value in NT mode is 1.

#### 6.13.4. BAR Limit Registers

BAR Limit registers, if used (for efficient use of memory resources) are typically programmed at runtime (because BARs are typically programmed at runtime, such as in a Plug 'n' Play system). BAR Limit registers contain an address; if the value is outside the range of the associated BAR register, the BAR Limit is ignored.

#### 6.13.5. Memory BAR Address Translation Registers