## アプリケーションノート1078

### はじめに

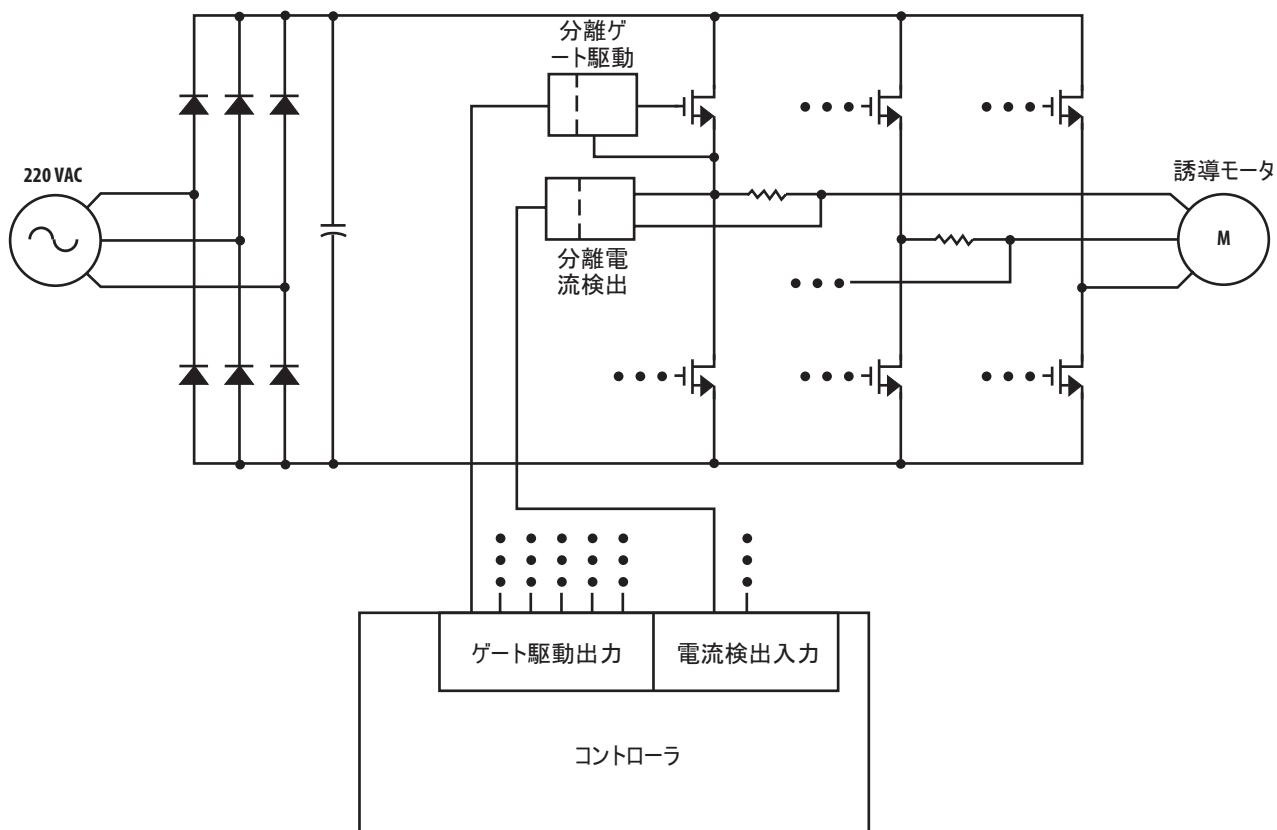

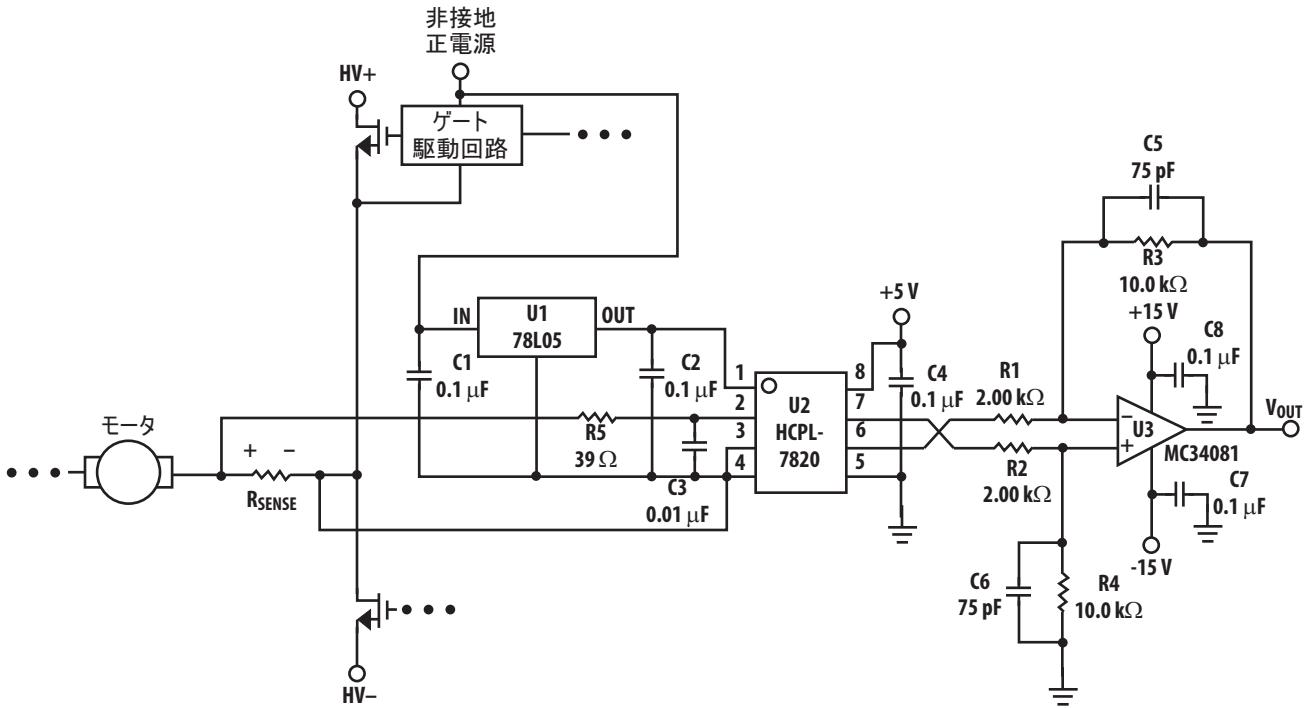

設計者が直面する難しい問題の1つは、ノイズがきわめて多い環境で高精度アナログ信号を分離することです。一つの例として、高性能モータ駆動の相電流の監視があります。図1に示す標準的な三相誘導モータ駆動では、最初に、三相ACライン電圧を整流しフィルタリングして高電圧直流電源にした後、出力トランジスタが直流電源電圧を、三相誘導モータを駆動する交流信号に戻します。モータ駆動は、一般的に、パルス幅変調方式(PWM)によって、モータ用の可変電圧可変周波数の駆動信号を生成します。高性能なモータ駆動には、一般的に、電流検出機能が組み込まれています。高精度アナログ信号を分離する際の問題は、インバータトランジスタのスイッチングによって引き起こされる大きな電圧過渡事象によって生じます。このきわめて大きな過渡事象(少なくとも直流電源電圧と振幅が等しい)は、急激な増大率を示すことがあります( $10\text{kV}/\mu\text{s}$ を超える)

、モータの各位相に流れる電流の検出をきわめて困難にします。

アバゴ・テクノロジーのアイソレーション・アンプは、特に、この種の設計問題を解決するため小型低コスト・ソリューションとして開発されました。これらのアイソレーション・アンプは、優れたゲイン精度とオフセット精度を維持しながらきわめてノイズの多い環境で電流を検出することができます。また、これらのアイソレーション・アンプは、時間と温度両方で高い安定性を示し、また非常に優れた同相雑音除去(CMR)性能を備えています。入力電圧範囲が小さいため、電流検出抵抗(電流シャント)の電力損失を最小限に抑えることができ、また+5V入力電源だけで正と負両方の入力電圧を検出することができます。

図1. 典型的な三相交流誘導モータ駆動

アバゴ・テクノロジーのアイソレーション・アンプは、よく一般的に使用される別の電流検出素子であるホール効果センサよりも温度変化に対するドリフトがきわめて小さい優れたゲインおよびオフセット特性を備えています。さらに、このアイソレーション・アンプは、高い同相雑音耐性を示し、外部磁界による影響を受けにくく、オフセットに悪影響を及ぼす残留磁化効果はありません。また、プリント回路基板への取り付けが容易であり、設計者は、状況に応じて柔軟に使用することができます。この柔軟性により、同じ回路とレイアウトを使用し、異なる電流検出抵抗器と交換して様々な範囲の電流を検出することができます。このような特徴により、アバゴ・テクノロジーのアイソレーション・アンプは、様々な用途で電流を検出するための優れた選択肢となります。

## 機能

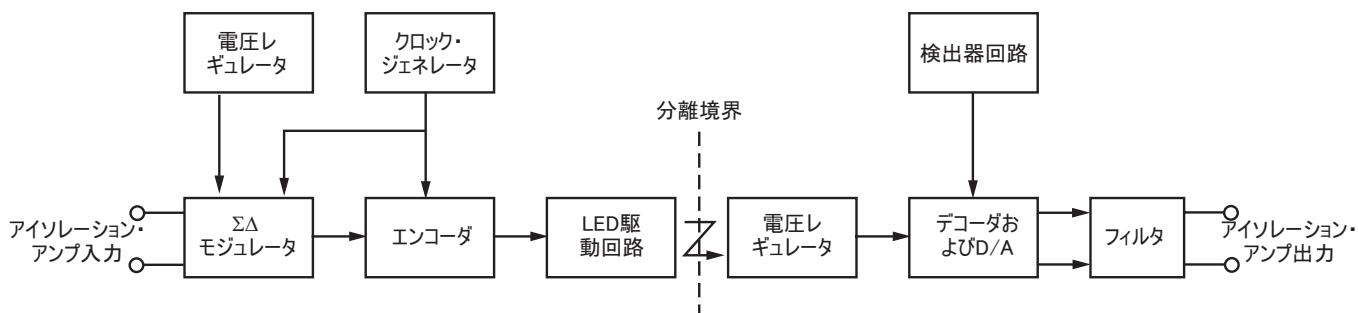

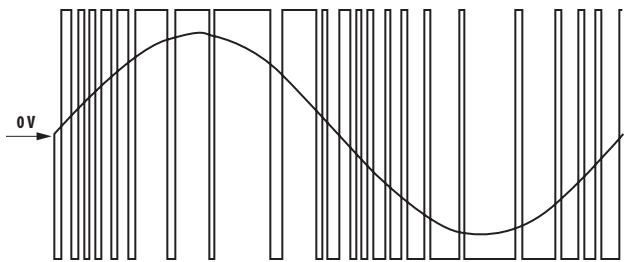

図2は、アバゴ・テクノロジーの代表的なアイソレーション・アンプHCPL-7820の主要機能ブロックを示しています。その動作は、シグマーデルタ・モジュレータが、アナログ入力信号を高速のシリアル・ビット・ストリームに変換し、ビット・ストリームの時間平均は、図3に示したように入力信号に正比例します。デジタル・データのこの高速ストリームは、符号化され、検出回路に光伝送されます。検出信号は、復号され、アナログ信号に変換され、フィルタリングされて最終的な出力信号が得られます。

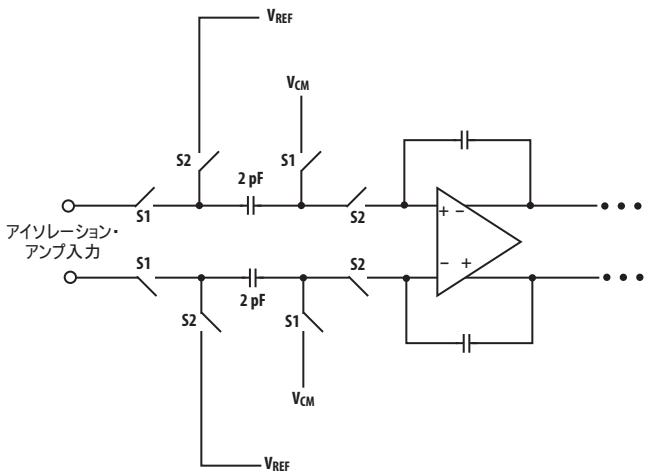

シグマ-デルタ・モジュレータでは、入力信号が、図4と類似のスイッチト・キャパシタ回路を使用して、きわめて高いレート(500~1000万サンプル/秒)でサンプリングされます。入力サンプリング・キャパシタをクロック周期のわずか半分以内で完全に充電しなければならないので、アイソレーション・アンプのピーク入力電流が

平均入力電流より大きくなることがあります。このピーク入力電流があるため、アイソレーション・アンプの入力にバイパス・コンデンサを設けることを推奨します。

また入力バイパス・コンデンサは、簡単なアンチエイリアス・フィルタの一部を構成し、高周波数ノイズが低周波数にエイリアシングするのを防ぎ、また入力信号の干渉を防ぐために推奨しています。

アバゴ・テクノロジーのアイソレーション・アンプは、電流検出用途、特にモータ駆動の性能を高めるように設計された付加機能を備えています。主要な内部アンプのチョッパ安定化と全差動構成により、優れた入力オフセットとオフセット・ドリフト性能を維持しつつ小さいフルスケール入力電圧での動作が可能です。低い入力電圧は、外部電流検出抵抗器の電力損失を最小限に抑えるのに役立ちます。さらに、独自の入力回路によって、グランドより低い入力信号を正確に検出することが可能になり、入力に追加の電源が不要になり、単一+5V電源での使用が可能になります。

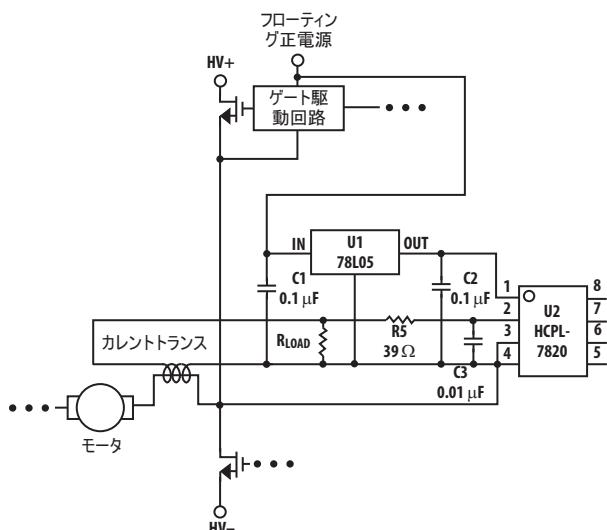

## 応用回路

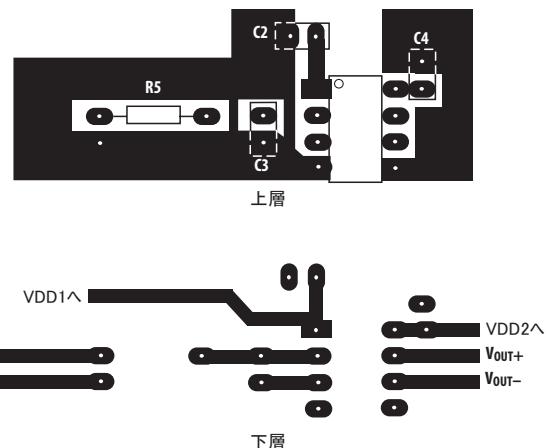

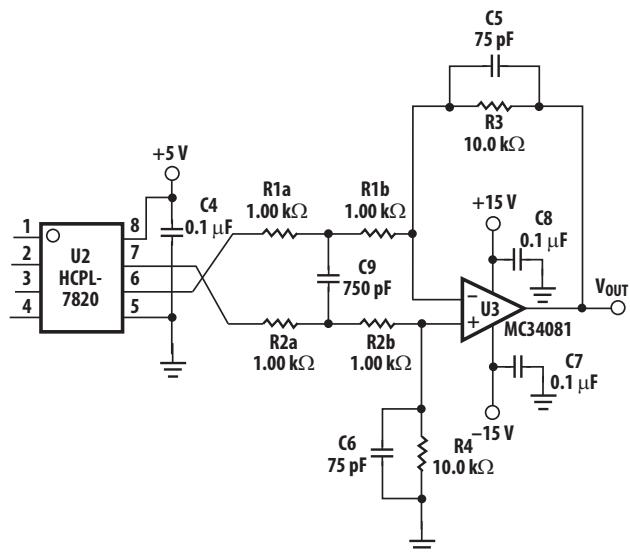

推奨応用回路を図5に示します。フローティング電源(多くの用途で高電圧側パワートランジスタを駆動するために使用される電源と同じ電源でよい)が、簡単な三端子電圧レギュレータ(U1)を使用して5Vに整流されます。電流検出抵抗器すなわちシャント(Rsense)からの電圧が、RCアンチエイリアシング・フィルタ(R5とC3)を介してHCPL-7820(U2)の入力に印加されます。また、アイソレーション・アンプの差動出力は、最終的に、簡単な差動アンプ回路(U3と関連した構成要素)によってグランド基準のシングルエンド出力電圧に変換されます。この応用回路は比較的簡単ですが、最適な性能を引き出すため次に推奨するいくつかの方法に従ってください。

図2. HCPL-7820ブロック図

## 電源とバイパス

アイソレーション・アンプの電源は、ほとんどの場合、パワートランジスタのゲート駆動回路に電力供給するために使用されるものと同じ電源から取ることができます。専用電源が必要な場合は、多くの場合、既存の変圧器に巻線を追加することで得ることができます。他には、ライン電源変圧器や高周波数DC-DCコンバータなどの簡単な絶縁電源を使用することができます。

前に述べたように、安価な78L05三端子レギュレータ(U1)を使用してゲート駆動の電源電圧を5Vに下げるることができます。高周波電源ノイズすなわちリップルを減衰させるために、レギュレータの入力と直列に抵抗器またはインダクタを使用して、レギュレータの入力バイパス・コンデンサと低域フィルタを構成することができます。

図5に示すように、アイソレーション・アンプ(U2)の入力電源端子と出力電源端子のできるだけ近くに $0.1\mu F$ のバイパス・コンデンサ(C2とC4)を入れてください。このバイパス・コンデンサは、アイソレーション・アンプ内部のデジタル信号が高速なために必要なものです。入力回路のスイッチト・キャパシタの特性から、入力端子に $0.01\mu F$ バイパス・コンデンサ(C3)を挿入することを推奨します。

電源バイパス・コンデンサと入力バイパス・コンデンサの配置により、アイソレーション・アンプの入力のオフセットを変化させることができます。オフセットのこの変化は、入力電源バイパス・コンデンサと、入力バイパス・コンデンサとアイソレーション・アンプの入力配線を含む入力回路との誘導結合から生じます。高周波電源バイパス電流の一部は、入力信号のサンプリング周波数であり、この周波数の誘導電圧は、直流までエイリアシングし、アイソレーション・アンプの実効オフセットが大きくなります。この作用により、入力回路のすぐ近くの金属物体が、関連インダクタンスを変化させる金属の透磁率によりオフセットに影響を及ぼす可能性もあります。

図3. シグマーデルタ変調の例

図4. 入力サンプリング回路網

図5. HCPL-7820の推奨応用回路

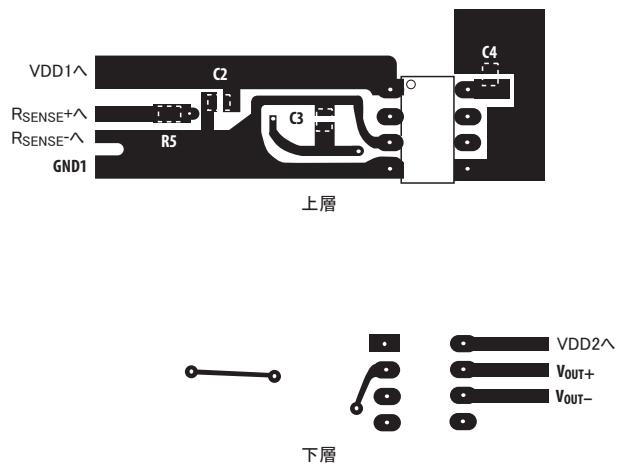

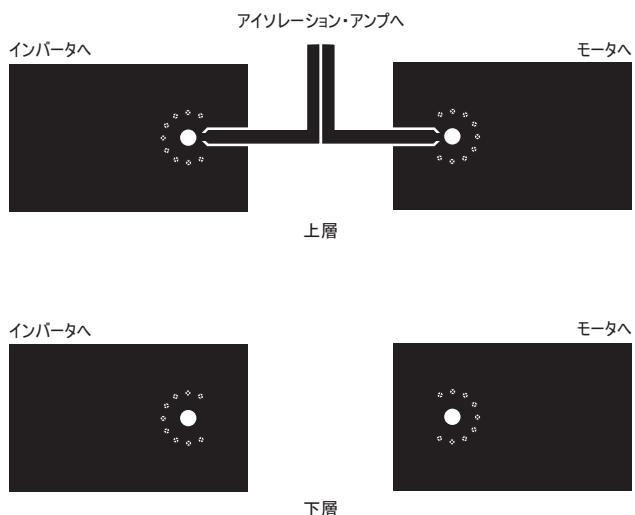

いくつかのステップをとることにより回路のこれらの2つの部分の相互結合を最小にすることができます、それにより設計のオフセット性能を改善することができます。2つのバイパス・コンデンサ(C2とC3)を、各バイパス・コンデンサの全リード長(トレースを含む)を20mm未満にしたまま、できるだけ遠くに配置します(プリント回路基板の両面に配置している場合も同様にしてください)。プリント回路基板トレースは、ループ面積と漂遊磁界のピックアップを最小にするために、できるだけ短く、また近くに配置するか接地平面上に配置しなければなりません。ソケットは、一般的にループ面積とインダクタンスの両方を大きくするので使用を避けてください。最後に、小型サイズのキャパシタを使用し、それらのキャパシタ(C2とC3)をPC基板上で互いに垂直に向けることが有効な場合もあります。図6は、上記で提案した案を反映したアイソレーション・アンプ入力回路のスルーホールPC基板レイアウトの例です。図6に示したレイアウトは、説明のためのものであり、写真通りに再現しても実際のプリント基板を作成することはできません。

この相互結合を有効に利用することもできます。たとえば、図6に示したレイアウトを修正して磁気結合を大きくし、図7に示したように温度変化に対するオフセット・ドリフトを最小にすることができます。このレイアウトの目的は、相互結合効果をできるだけ相殺することです。そのため、入力リードは、パッケージの近くに互いに重なり、入力バイパス・キャパシタ(C3)とループを構成します。この入力ループは、電源トレースと電源バ

イパス・キャパシタ(C2)で構成された別のループ内にあります。これらの2つのループ間の結合の極性は、前述の望ましくない相互結合効果を相殺しやすい極性です。内部ループの面積を調整することによって(たとえば、レイアウトの入力バイパス・キャパシタの位置を左右にずらすことによって)、結合の大きさを変化させて相殺量を適切にすることができます。このオフセット温度係数相殺方法は、素子の平均温度係数をゼロに近づけますが、部品ばらつきによってすべての素子の温度係数を完全に相殺することはできません。オフセット温度係数は、一般に、半分以下に減少させることができます。残念ながら、オフセット・ドリフトのこの減少は、初期オフセットをわずかに増大(HCPL-7820の場合は約1~2mVのオフセット増大)させることになります。図7のレイアウトは、図6と同じように単なる説明用ですので注意してください。

## シャント抵抗

電流検出シャント抵抗は、低抵抗(電力損失を最小にする)、低インダクタンス(動作に悪影響を及ぼすdi/dt誘導電圧スパイクを最小にする)、および適切なばらつき精度(回路全体の精度を維持する)を備えていなければなりません。シャントの値の選択は、一般的に、電力損失を最小にすることと精度を最大にすることの妥協になります。シャント抵抗を小さくするほど電力損失が小さくなり、シャント抵抗を大きくすることで、アイソレーション・アンプの入力範囲全体を利用することになり回路精度を改善することができます。

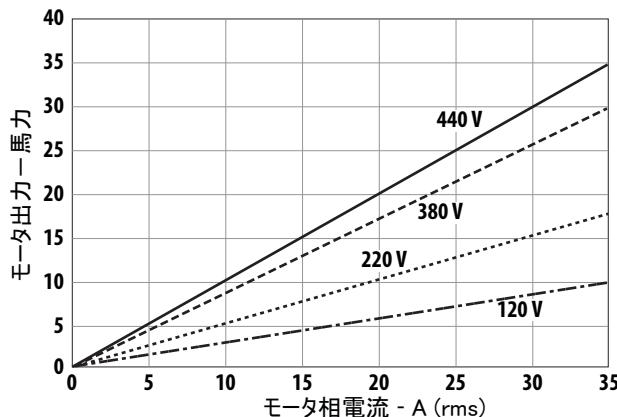

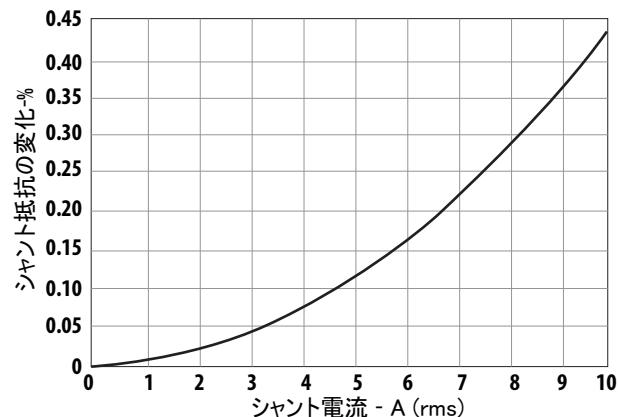

シャントを選択する最初の段階は、シャントで検出する電流の量を決めることがあります。図8のグラフは、三相誘導モータの各相のRMS電流を平均モータ出力電力(馬力hp)とモータ駆動電源電圧の関数として示したもので、シャントの最大値は、測定する電流とアイソレーション・アンプの最大推奨入力電圧によって決定されます。最大シャント抵抗値は、最大推奨入力電圧を求め、通常動作中にシャントで測定されるピーク電流で割ることによって計算することができます。たとえば、モータが、10Aの最大RMS電流を有し、通常動作中に最大50%の過負荷を受ける可能性がある場合、ピーク電流は、 $21.1A (=10 \times 1.414 \times 1.5)$ です。最大許容入力が200mVと仮定すると、シャント抵抗の最大値は、約 $10\text{ m}\Omega$ になります。

また、シャントの最大平均電力損失は、シャント抵抗値に、前の例では約1Wの最大RMS電流の二乗を掛けることによって簡単に計算することができます。

シャントの電力損失が大きすぎる場合は、シャントの抵抗値を最大値より小さくして電力損失を少なくすることができます。シャントの最小値は、設計の精度と確度によって制限されます。シャントの値を小さくすると、シャントの両端の出力電圧も低下し、そのためアイソレーション・アンプの一定のオフセットとノイズが、信号振幅の大きな割合を占めるようになります。

一般的に、シャントの実効値は、特定の設計要件により、最小値と最大値の間にになります。

アバゴ・テクノロジーは、最大35Aと35hpまでのモータ駆動の平均電流を検出するために使用することができるDale製の4種類の二端子シャントを推奨します。表1は、推奨するLVRシリーズのそれぞれの最大電流と馬力範囲を示します。Dale、IRC、Isotek(Isabellenhuette社)などのベンダーから入手可能なもっと低い値の四端子シャントでさらに高い電流を検出することが可能です。また、温度係数の低い金属合金シートから適切なパターンを打ち抜くことによって、独自の四端子シャントを作成することも可能です。

図6. アイソレーション・アンプ入力回路のプリント基板レイアウトの例

図7. オフセット温度係数を最小にする面実装プリント基板レイアウトの例

図8. モータ出力馬力とモータ相電流/電源電圧の関係

図9. LVRシャント抵抗の変化とシャント電流の関係

検出電流が、シャントを著しく発熱させるほど大きいときは、シャントの温度係数(tempco)により、信号によるシャントの温度上昇によって非線形性が生じる可能性があります。たとえば、図9は、LVRシャントの抵抗値が、一般的に、標準的なプリント基板構成でシャントに流れる平均電流の関数としてどのように変化するかを示しています。図9に示された影響は比較的小さいものですが、この影響は、シャントから周囲への熱抵抗が大きくなるほど大きくなります。この影響は、シャントの熱抵抗を小さくするか低い温度係数のシャントを使用することより最小にすることができます。熱抵抗を小さくするには、プリント基板上のシャントの位置を変更して容易に実現できることもあり、またヒートシンクを使用しなければならないこともあります。

シャント抵抗値が小さくなるほど、シャントの配線抵抗が、シャント抵抗全体のうちの大きな割合になります。このことは、シャントの精度に2つの影響を及ぼします。第1に、シャントの実効抵抗が、配線の長さ、配線の曲がり方、配線が基板に挿入された距離、組み立て時の配線のはんだウイックの大きさなどの要因に依存します(これらの問題については、後で詳しく説明します)。

第2に、リードは、一般的に、抵抗素子自体が作成される材料よりも高い温度係数の銅などの材料から作成されるので、シャント全体の温度係数が高くなります。

四端子シャントを使用すると、これらの2つの影響がなくなります。四端子シャントは、抵抗素子自体の両端に直接ケルビン接続された2つの追加端子を有し、これら2つの端子は、抵抗素子両端の電圧を監視するために使用され、他の2つの端子は、負荷電流を流すために使用されます。ケルビン接続により、負荷電流を流す配線の両端の電圧降下は小さく、測定電圧にほとんど影響を及ぼしません。

四端子シャントは、二端子シャントよりも高性能ですが高価なため、その使用がより高精度な用途に限られます。ただし、二端子シャントは、適切に使用することにより高い性能を発揮します。二端子シャントを使用する際の大きな問題の1つは、一般的にプリント基板に取り付けられるシャントの精度を確保しながら、再現可能な接続を行うことです。図10は、抵抗を約5mΩに下げた二端子シャントによって高い性能を達成することができるプリント基板レイアウトの実例を示します。

表1. 電流シャントの一覧

| シャント抵抗<br>の部品番号 | シャント抵抗 | 公差 | 最大電力損 | 最大RMS<br>電流 | 最大馬力<br>範囲   |

|-----------------|--------|----|-------|-------------|--------------|

| LVR-3.05-1%     | 50 mΩ  | 1% | 3 W   | 8 A         | 0.8 - 3.0 hp |

| LVR-3.02-1%     | 20 mΩ  | 1% | 3 W   | 8 A         | 2.2 - 8.0 hp |

| LVR-3.01-1%     | 10 mΩ  | 1% | 3 W   | 15 A        | 4.1 - 15 hp  |

| LVR-5.005-1%    | 5 mΩ   | 1% | 5 W   | 35 A        | 9.6 - 35 hp  |

このレイアウトにはいくつかの注意すべきことがあります。シャント配線がプリント基板と接触する接点のできるだけ近くに2つの「疑似ケルビン」接続が設けます。疑似ケルビン接続は、シャントの下に集められ、AINレジスタ・アンプの入力まで互いに接近して伸びます。そのため、接続ループ面積が最小になり、漂遊磁界(モータ駆動内に多量にある)が測定信号を妨害する可能性が低下します。シャントが、プリント基板のAINレジスタ・アンプ回路と同じ側に配置されない場合は、きつく撲られたツイストワイヤで同様のことを実現することができます。

また、電流伝導能力を高めるためには、プリント基板の両面を使用してください。多数のめっき貫通ビア(図10では中心に十字のある円として示された)が、シャントの各端子を取り囲み、プリント基板の両面に電流が分散しやすくなっています。プリント基板には、10~20Aの電流伝達能力が得られるように、2つの層に2または4オンスの銅を使用してください。プリント基板上の電流伝達トレースをかなり大きくすることにより、ヒートシンクの役割をさせ、シャントの電力損失特性を改善することができます。また、負荷電流がプリント基板を流れる部分にビアを多数使用することは、シャントを使用する際に推奨される理由と同じ理由で推奨されます。

二端子シャントの使用に関して最後に推奨することは、シャントの配線が、どれもばらつきなく同じように曲げられ、プリント基板にどれも同じ距離で挿入されるようにすることです。これは、一般に、自動組立では問題になりませんが、少量の手動組立基板では問題になることがあります。手動組立基板の場合は、リード曲げジグを使用し、シャントがどれも基板に完全に差し込まれ、各シャントの配線長のばらつきが最小になるように注意してください。

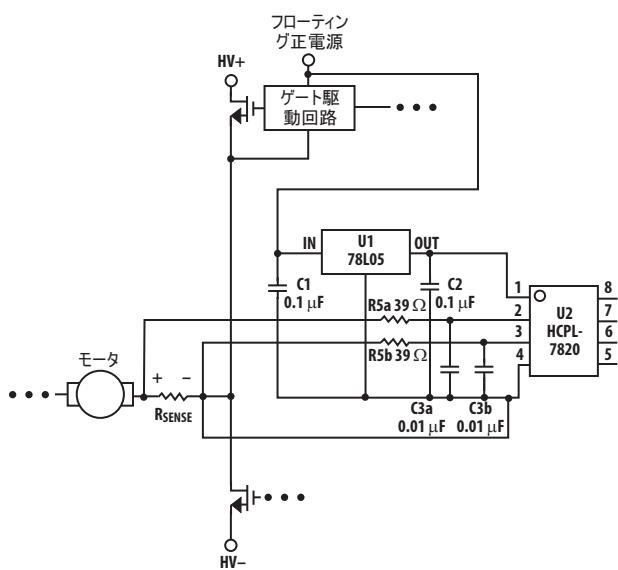

大きな交流電流を測定するためにシャントを使用する代わりに、図11に示したように、AINレジスタ・アンプの入力に接続した安価なカレントトランス(CT)を使用することができます。カレントトランスは、電流シャントほど侵襲的でなく、大電流(50A超)を測定するときの電力損失をきわめて少なくすることができます。AINレジスタ・アンプが主要な分離障壁を提供するため、分離能力がほとんどない低コストのカレントトランスを使用することが可能です。

## シャント接続

シャント抵抗にAINレジスタ・アンプを接続する推奨方法を図5に示します。 $V_{IN+}$ (HPCL-7820の端子2)がシャント抵抗の正端子に接続され、 $V_{IN-}$ (端子3)がGND1(端子4)に短絡され、電源帰還経路は、電流シャントの負端子への検出ラインとして働きます。これにより、1対のワイヤまたはプリント基板トレースでAINレジスタ・アンプ回路をシャント抵抗に接続することができます。入力回路の基準を検出抵抗の負側にすることにより、シャントに負荷電流で生じるノイズ過渡事象が同相信号と見なされ、電流検出信号に干渉しなくなります。このことは、モータ駆動に流れる大きな負荷電流が、回路の配線の寄生インダクタンスと共に、電流シャントの両側で測定される小さな電圧より大きなノイズ・スペクトラムとオフセットを両方生成する可能性があるため重要です。

ゲート駆動回路と電流検出回路の両方に同じ電源を使用する場合は、グランドループ問題を回避するため、AINレジスタ・アンプのGND1から検出抵抗への接続が、ゲート駆動電源に電流を供給する唯一のリターン・パスであることがきわめて重要です。AINレジスタ・アンプ回路とゲート駆動回路は唯一直接フローティング電源ラインで接続されます。

図10. 二端子シャントのプリント基板レイアウトの例

ただし、用途によっては、電源リターン・パスに流れる電流が、オフセットまたはノイズの問題を引き起こす場合があります。この場合、図12に示すように、シャント抵抗の両側のVIN+とVIN-を直接2つの導体と接続し、GND1を電源リターン・パスである第3の導体でシャント抵抗に接続することによって、性能を高めることができます。このように接続したときは、両方の入力端子をバイパスしてください。検出信号の電磁妨害を最小にするため、アイソレーション・アンプを検出抵抗に接続する導体(2本か3本を使用)はすべて、ツイストペア線かプリント基板上の狭い間隔のトレースでなければなりません。

入力配線に直列の $39\Omega$ の抵抗(R5)は、 $0.01\mu F$ 入力バイパス・キャパシタ(C3)と、帯域幅400kHzを有するローパスアンチエイリアシング・フィルタを構成します。この抵抗は、別の重要な機能を有し、シャント、入力バイパス・コンデンサ、および2つを接続するワイヤまたはトレースのインダクタンスによって構成された回路により生じる可能性のあるリングギングを減衰させます。入力サンプリング周波数付近の入力回路のリングギングが減衰されないと、ベースバンドにエイリアシングし、素子の出力にノイズとなって現れる可能性があります。

## プリント基板レイアウト

プリント基板のレイアウトは、オフセットに影響を及ぼす他にも、主に入力回路と出力回路間の漂遊容量結合によりアイソレーション・アンプの同相雑音除去(CMR)性能に影響を及ぼす可能性もあります。最適なCMR性能を得るために、プリント基板のレイアウトは、回路の入力側と出力側間の最大限可能な距離を維持し、プリント基板上の接地平面がアイソレーション・アンプ本体の真下を通らずまたアイソレーション・アンプ本体より幅広くならないようにすることによって、漂遊結合を最小化しなければなりません。面実装部品を使用することにより、前節で述べたプリント基板の目的の多くを達成することができます。さらに重要な推奨レイアウトを示すスルーホールプリント基板レイアウトの例を、図6に示します。アイソレーション・アンプ本体の真下に接地平面が延在しないことに注意してください。

図5に示した完成した応用回路の面実装のレイアウトは、アバゴ・テクノロジーのアプリケーション・エンジニアリング部門から入手可能です。シャント抵抗を含むレイアウトのサイズは、約3cmの正方形です。詳しくはお近くのアバゴ・テクノロジー営業所にお問い合わせください。

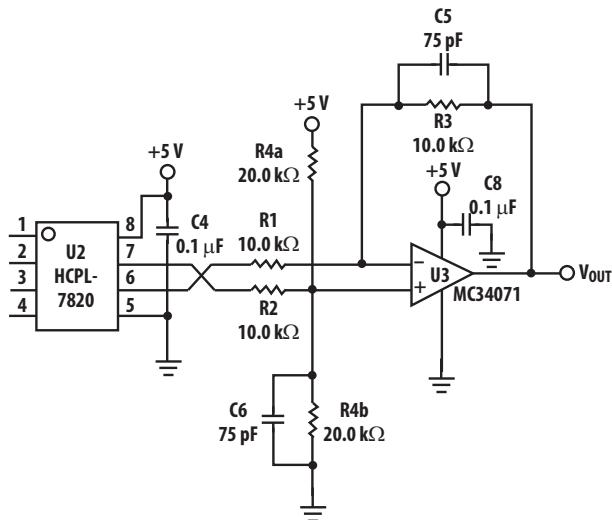

## ポストアンプ回路

図5に示した推奨応用回路には、出力信号の基準を所望のレベル(通常は、グランド)にし、信号を適切なレベルに増幅し、出力ノイズをフィルタリングする3つの機能を持つポストアンプ回路を含まれています。ポストアンプ回路に使用する特定のオペアンプは、必須ではありませんが、回路性能に悪影響を及ぼさないようにオフセットが十分に低く、また帯域幅とスルーレートが十分に高くなればなりません。オペアンプの最大オフセットは、HCPL-7820の出力オフセットより低くなければならず、約5mV未満でなければなりません。ゲインは、抵抗器R1～R4によって決定されます。R1=R2とR3=R4と仮定すると、ポストアンプのゲインはR3/R1となります。

図11. 非絶縁のカレントトランスを使用した大きな交流電流の測定

図12. 3つの導体を使用したシャント接続の回路図

回路全体の帯域幅と速度を最速に維持するために、ポストアンプ回路は、アイソレーション・アンプの最小帯域幅の少なくとも2倍の帯域幅、すなわち約400kHzの帯域幅を備えていなければなりません。ただし、もっと低い帯域幅を使って出力ノイズを減少させることができます。応答時間が遅くなります。ポストアンプ回路にキャパシタC5とC6を使用しない場合、ポストアンプの帯域幅は、オペアンプのゲイン帯域幅積(GBW)によって決定されます。ゲイン5で400kHzの帯域幅を得るには、オペアンプは、2MHzを越えるGBWを備えていなければなりません。オペアンプのGBWを使用して回路全体の帯域幅を設定することは、オペアンプのGBWは通常、標準値のみで全温度保証されていないため、あまりよい考えではありません。

ポストアンプ回路の帯域幅の精度を上げるには、 $R3=R4$ で $C5=C6$ と仮定した場合、キャパシタC5とC6を使用して公称帯域幅 $1/(2 \times \pi \times R3 \times C5)$ の単極ローパスフィルタを構成することによって達成することができます。これらのキャパシタにより、ポストアンプの帯域幅をゲインと無関係に調整することができ、アイソレーション・アンプの出力ノイズを減少させることができます。

C5とC6を使ってローパスフィルタ周波数を正確に設定するには、オペアンプのGBWは、ポストアンプ・ゲインと所望のローパス周波数の積の約10倍より大きが指定されなければなりません。GBWがそれより低いと、ローパス周波数を10~15%以上変化させることになります。ポストアンプのゲインが5でローパス周波数が200kHzの場合、オペアンプのGBWは、少なくとも7~10MHzでなければなりません。図5に示した部品値は、ゲインが5でカットオフ周波数が約200kHzの差動増幅器を構成し、低ノイズと高速応答時間のトレードオフで選択されています。代表的なアイソレーション・アンプを含む総合的な推奨応用回路は、帯域幅約130kHz、立ち上がり時間2.6μs、90%までの遅延が4.2μsのものです。

オペアンプは、十分な帯域幅を有する他に、大きな振幅波形を正確に再現できるだけのスルーレートを備えていなければなりません。必要なスルーレートは、増幅

器回路の出力の最大予想電圧振幅をR3とC5の積であるフィルタ時定数で割ることにより控えめに見積もることができます。この推定値は、回路全体の応答時間がアイソレーション・アンプの応答時間によって支配されるため、フィルタ帯域幅が大きい方が控えめな値になります。たとえば、入力変動を±200 mV、ポストアンプ・ゲインを5、フィルタ帯域幅を200kHzと想定すると、オペアンプに必要なスルーレートは、約20V/μsと推定されますが、実際には10V/μs未満の値が必要です。

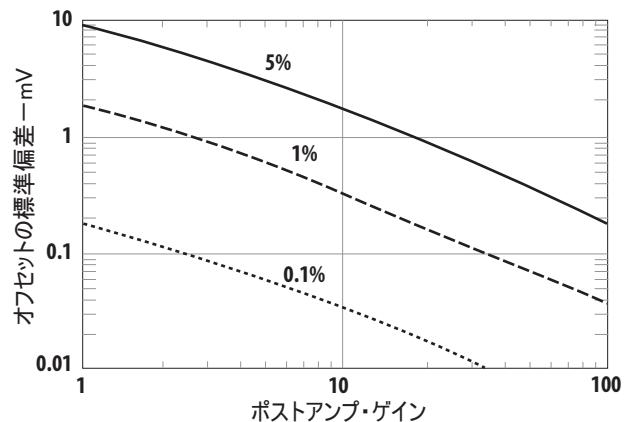

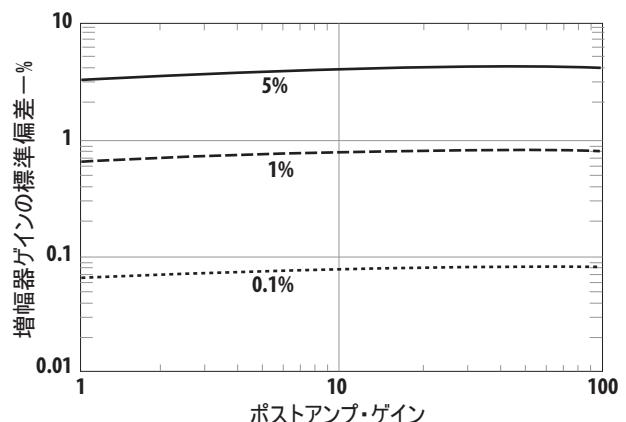

ポストアンプのゲイン設定抵抗は、回路全体の十分なCMRRとゲイン公差を保証するために、公差が1%以下でなければなりません。ゲイン設定抵抗が大幅にずれると、ポストアンプのCMRRを低下させ、回路のオフセットに影響を及ぼす可能性があります。図13は、様々な抵抗公差の場合にポストアンプ・ゲインに対してオフセット精度をどれだけ高めることができるかを示し(アイソレーション・アンプ・ゲインを8と仮定した場合のアイソレーション・アンプの入力を指す)、得られた入力オフセット分布の標準偏差を示しています。差動アンプ回路から予想されるように、分布の平均はゼロです。同様に、図14は、様々な抵抗公差の場合にポストアンプがポストアンプ・ゲインに対して回路全体のゲイン公差の高まりにどれだけ影響を及ぼすかを示しており、得られたポストアンプ回路のゲイン分布の標準偏差を示します。図13と図14のデータは、モンテカルロ・シミュレーションによって生成されており、抵抗値がその公称値のまわりに均一に分散されることを控えめに仮定しています。Daleから供給されている、優れた性能を有し部品数と基板スペースを削減することのできるきわめて厳密な公差を有する抵抗回路網を使用することができます。

ポストアンプ回路は、单一電源で動作できるように容易に修正することができます。図15は、5V単一電源用途で使用されるポストアンプの回路図を示しています。1個の追加抵抗器(R4a)を追加し、十分な入力電圧範囲で回路が動作できるようにゲインが下げられています。抵抗器を追加することにより、出力基準電圧が0から電源電圧の半分になります。

## 出力ノイズ

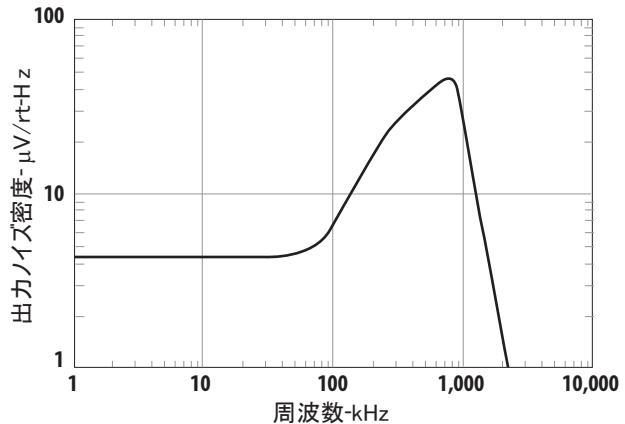

図16にHCPL-7820に関して示したように、シグマーデルタ・モジュレータのノイズ・シェイピング特性により、出力ノイズ・スペクトルは通常とわずかに異なるものになります。ノイズ・スペクトルは、約40kHzまで平坦で、そこで1オクターブ当たり12dBで増大します。内部フィルタが、約200kHzでノイズ・スペクトルを減衰させ始め、1MHzの直前でノイズ・スペクトルが急激に低下します。ノイズ・スペクトルの形は、所定の信号帯域幅の出力ノイズをフィルタリングする最も有効な方法になります。

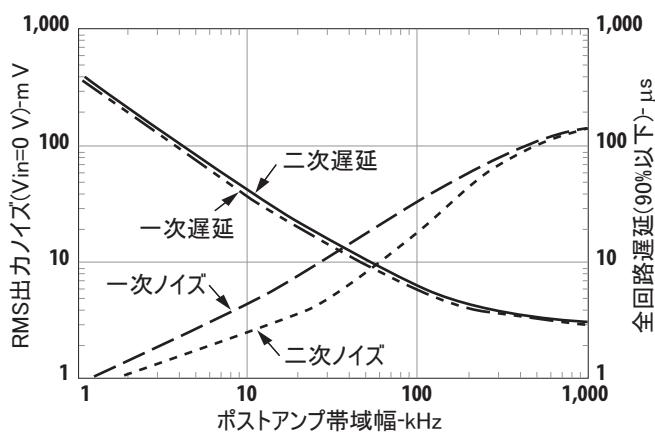

前に述べたように、ポストアンプ回路の帯域幅を縮小すると、出力ノイズの量が減少します(応答時間も長くなります)。ノイズ挙動が40kHzを超えると、特定のフィルタ帯域幅により、二次フィルタ応答が一次フィルタよりフィルタリング・ノイズに効果的になります。図17は、一次フィルタ応答と二次フィルタ応答の両方のポストアンプ帯域幅の関数として出力ノイズが変化するようすを示しています。図5に示した応用回路は、一次ローパスフィルタ特性を示しています。図18に示したように、2つの付加抵抗と1つのキャパシタ(R1a、R2aおよびC9)を追加することによって、二次フィルタ応答を得ることができます。キャパシタC9は、R1aとC9の積がR3とC5の積と等しくなるように選択されなければなりません。

ポストアンプの帯域幅を変更すると、回路の遅延にも影響を及ぼします。また、図17は、応用回路の遅延(90%以下)が、一次フィルタ応答と二次フィルタ応答両方のポストアンプ帯域幅の関数として変化するようすを示しています。このグラフから、出力ノイズと回路遅延と増幅器帯域幅間のトレードオフを簡単に決定することができます。

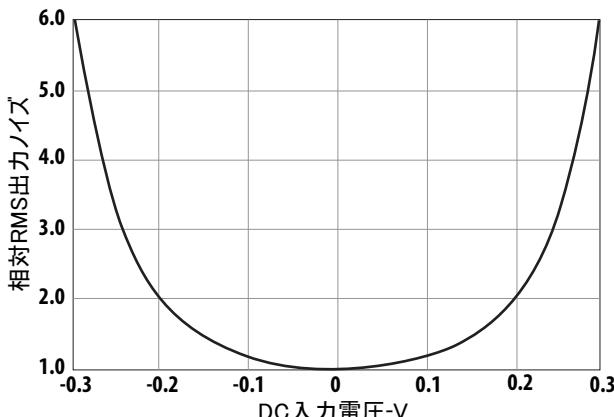

モジュレータの出力ノイズは、入力信号の振幅による影響も受けます。図19は、DC入力電圧に対するRMS出力電圧の相対振幅の関係を示しています。曲線は、約±200 mVまで比較的平坦であり、入力信号がそれより大きくなると急激に増大します。振幅によるノイズ増大は、出力フィルタの帯域幅に依存しません。

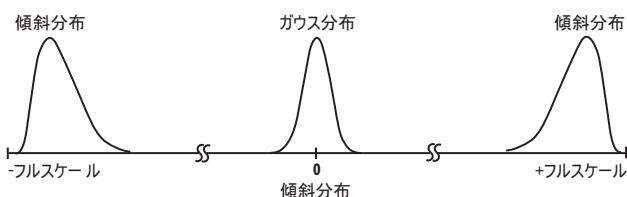

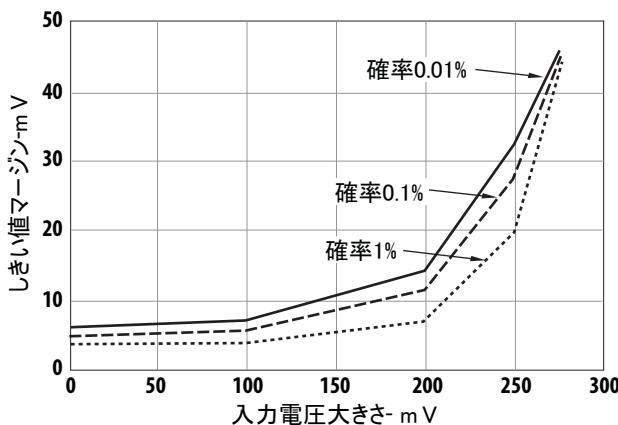

過負荷または故障状態を検出するためにアイソレーション・アンプを使用して、間違った過負荷指示を受け取る前に信号がしきい値にどれだけ近いかを決定しなければならないときは、出力ノイズの統計的特性(確率密度関数)が重要です。アイソレーション・アンプの出力ノイズは、入力電圧がほぼゼロのときは、ほぼガウス分布です。入力電圧がゼロから遠くなるほど、図20に示したように、ノイズはガウス分布でなくなり、確率分布関数のテールが、中間スケール方向に長くなり、フルスケール方向に短くなります。図21は、HCPL-7820に関して、様々なレベルの誤検出確率の場合に、誤検出しきい値(基準入力)が、特定の直流入力をどれだけ超えているかを示しています。たとえば、入力200mVの場合に誤検出確率を0.01%に制限するには、誤検出しきい値は、少なくとも214mV(しきい値マージン14mV)でなければなりません。最大推奨誤検出しきい値は約275mVです。

いくつかの用途でのオフセットを減少させるために、オフセットは、起動時にマイクロプロセッサによって測定され、その後のすべての測定から減算されます。そのようなタイプの自動較正用途では、内部接合部温度が安定した後でアイソレーション・アンプのオフセットを測定することによって精度を改善することができます。たとえば、HCPL-7820は、比較的小さな評価基板に取り付けられたとき、時定数が約15秒の場合に約100 μVの起動時オフセット・ドリフトを有します。自動較正操作の際に測定信号のフィルタリングまたは平均化を追加してノイズを減少させることによって精度を改善することができます。

図13. ポストアンプ基準入力オフセットの標準偏差とポストアンプ・ゲイン/抵抗公差の関係

図14. ポストアンプ・ゲインの標準偏差とポストアンプ・ゲイン/抵抗公差の関係

図15. HCPL-7820の単一電源ポストアンプ回路

図16. HCPL-7820出力ノイズ・スペクトル

図17.HCPL-7820応用回路のRMS出力ノイズ/遅延とポストアンプ帯域幅/フィルタ次数の関係

図18. 二次フィルタ応答を有するポストアンプ回路

図19. DC入力電圧に対する相対出力ノイズ

図20. ノイズ統計的特性と入力電圧の関係

図21. HCPL-7820しきい値検出マージンと入力電圧/誤検出確率の関係

## 電圧検出

アバゴ・テクノロジーのアイソレーション・アンプを使用することにより、入力に抵抗分圧器を使用することで推奨入力範囲より大きな振幅を持つ信号を分離することができます。唯一の制限は、アイソレーション・アンプの入力抵抗( $280\text{k}\Omega$ )と入力バイアス電流( $1\mu\text{A}$ )が測定精度に影響を及ぼさないようにしないように、分圧器のインピーダンスが比較的小さくなければならないことです( $1\text{k}\Omega$ 未満)。入力バイパス・コンデンサはやはり必要ですが、 $39\Omega$ の直列減衰抵抗は不要です(分圧器の抵抗が同じ機能を提供します)。分圧器抵抗と入力バイパス・コンデンサで構成されたローパスフィルタは、帯域幅を制限する場合があります。帯域幅をさらに高めるために入力バイパス・コンデンサ(C3)を省略することができますが、アイソレーション・アンプのゲイン精度を維持するために $1000\text{pF}$ 未満にしないでください。

## SPICEモデル

アバゴ・テクノロジー・アイソレーション・アンプのSPICEモデルは、アバゴ・テクノロジーのアプリケーション・エンジニアリング部門から入手することができます。詳しくはお近くのアバゴ・テクノロジー営業所にお問い合わせください。

For product information and a complete list of distributors, please go to our web site: [www.avagotech.com](http://www.avagotech.com)

Avago, Avago Technologies, and the A logo are trademarks of Avago Technologies in the United States and other countries.

Data subject to change. Copyright © 2005-2010 Avago Technologies. All rights reserved.

AV02-2632JP - September 24, 2010

**AVAGO**

TECHNOLOGIES