# **Application Note**

# AR49-M49M, AR49-M25S Series 25-Bit Optical Single-Turn with 24-Bit **Energy-Harvesting Multi-Turn Absolute Encoder Modules**

### Overview

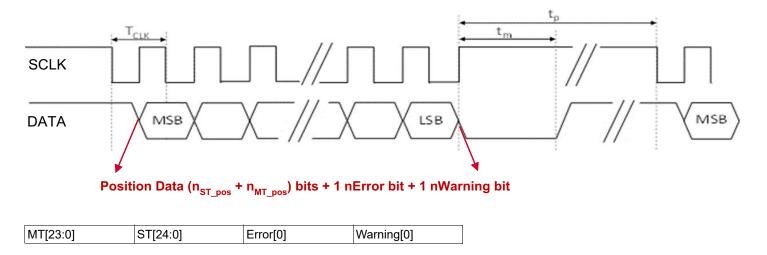

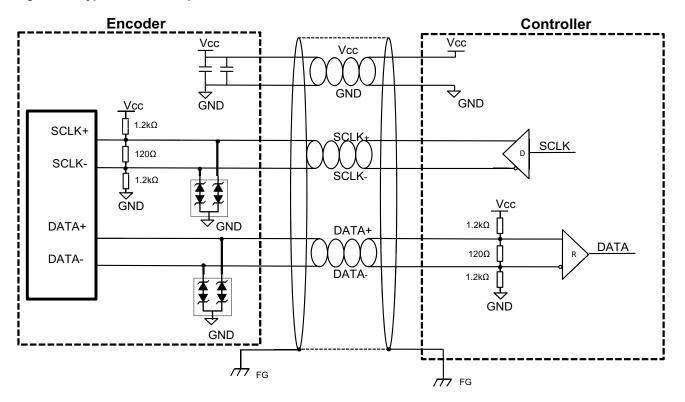

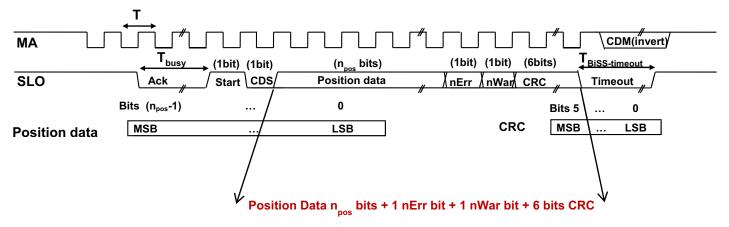

The Broadcom® AR49 series of optical absolute encoder modules offers up to 25-bit single-turn (ST) position information and 24-bit multi-turn (MT) counts, hence a combined 49-bit high resolution output. The ST block of the encoder consists of a patterned disk, a light source, and photosensitive elements to translate the mechanical motion into an electrical signal. It is designed with a selection of serial communication protocols, with a dedicated electronic circuit designed for a robust signal communication.

These encoders offer many intelligent features such as a built-in temperature sensor, user-programmable resolution, zero reset, system alarm, and more. They come with a recommended high-temperature range of -40°C to 115°C. One of the key advantages is the multi-turn tracking that employs a proprietary energy-harvesting (EH) technology by harvesting the magnetic energy while the patterned disk with magnet rotates. The counter ASIC harvests the energy generated by the EH sensor for processing rotational count and generating counting logics to the nonvolatile memory, which updates and stores the counting.

The entire operation of energy generation, counting, and storage processing is completed within limited energy and a short duration; hence, the kit encoder is suited for both lowspeed and high-speed measurements.

## **Applications**

- AC/DC servo motor feedback

- Medical and laboratory equipment

- Robotics

- Factory automation

**CAUTION!** This product is not specifically designed or manufactured for use in any specific devices. Customers are solely responsible for determining the suitability of the product for its intended application and solely liable for all loss, damage, expense, or liability in connection with such use. Contact Broadcom for further inquiry.

# **Mounting Requirement and Guideline**

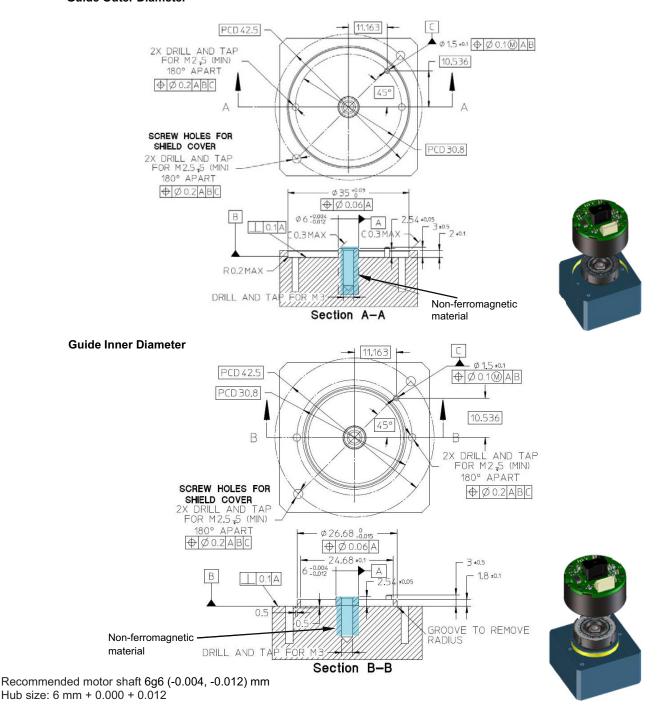

The AR49 encoder module is designed with two options of centering method.

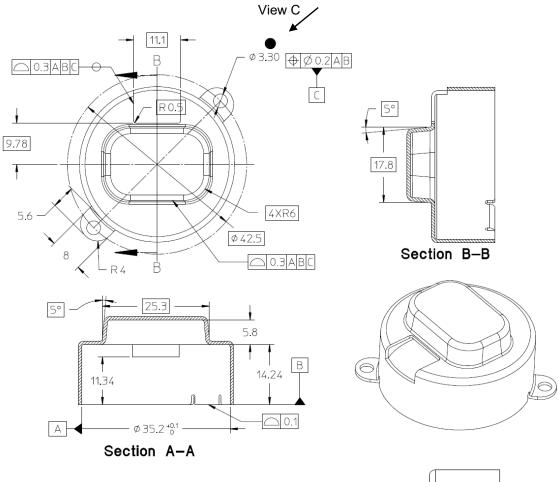

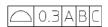

For guiding with the outer diameter (OD) or the inner diameter (ID) of the encoder module, the recommended motor mounting dimensions are shown in Figure 1.

Figure 1: Motor Mounting Dimension with 6-mm Shaft Size

#### **Guide Outer Diameter**

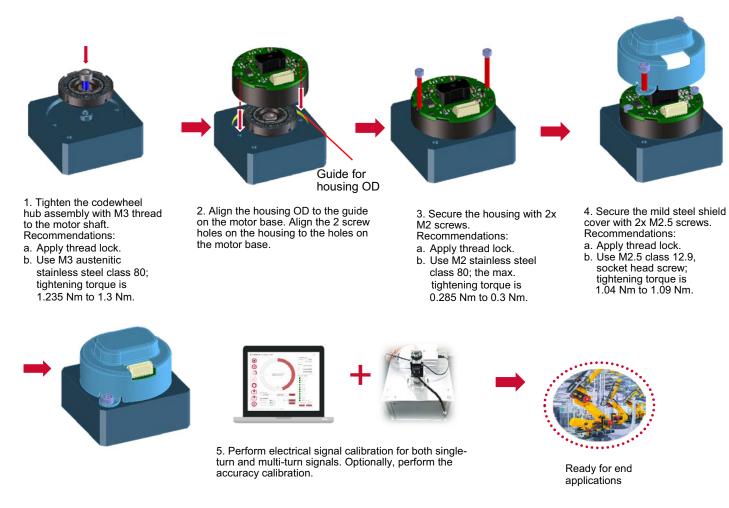

Figure 2: Assembly Guidelines for Mounting Requirement with OD Guiding

NOTE: Applicable for both ST and MT options.

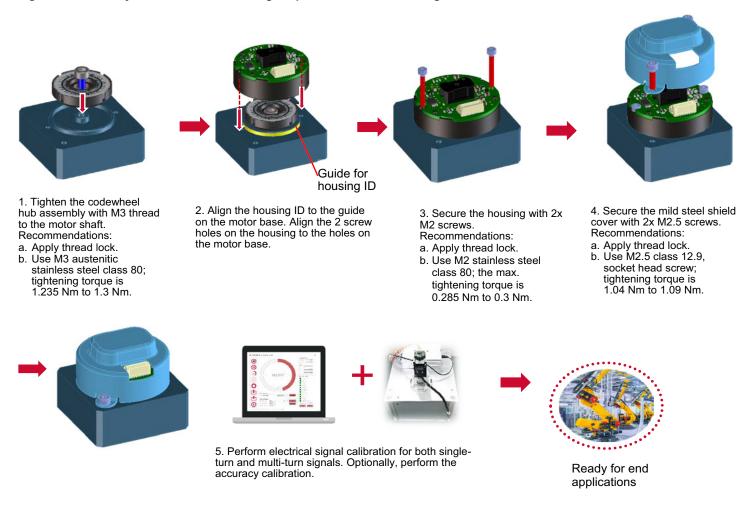

Figure 3: Assembly Guidelines for Mounting Requirement with ID Guiding

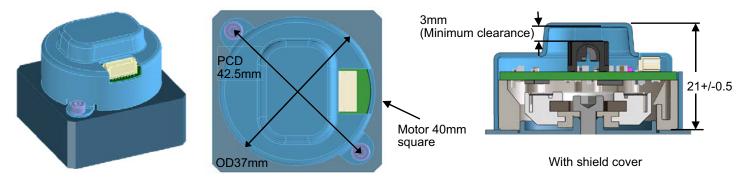

Figure 4: Recommended Shield Cover Dimensions

To eliminate or minimize the influence of the external magnetic field interference on encoder operation, use of shielding is mandatory for the AR49-M49M multi-turn options.

Recommended shield cover material: Mild steel SPCC-SD, thickness 0.8 mm (minimum).

Finishing: Ni plating 8 μm to 12 μm thick, with Cu under coating 2 μm to 4 μm.

Figure 5: Shield Cover Reference Design with Inner Diameter Guided Mounting

**NOTES:** Unless otherwise specified:

- 1. Fold radius = 0.5 mm.

- 2. Parts to be burr free.

- 3. This is a partially dimensioned drawing. For non-tolerance features, the following tolerance applies:

Critical dimensions.

Figure 6: Shield Cover Reference Design with Outer Diameter Guided Mounting

NOTES: Unless otherwise specified:

- 1. Fold radius = 0.5 mm.

- 2. Parts to be burr free.

- 3. This is a partially dimensioned drawing. For non-tolerance features, the following tolerance applies:

Critical dimensions.

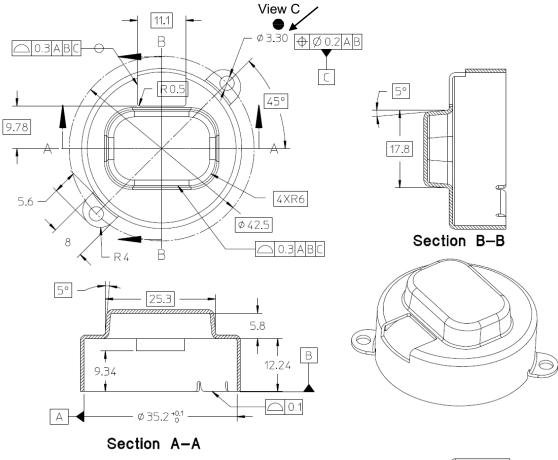

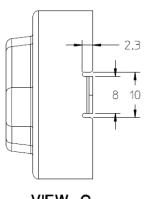

VIEW-C

# **Encoder Memory Area**

The AR49 supports 8 kb of user register area. The memory data is kept in a nonvolatile memory. The available register pages and banks are accessible by the user and unlocked.

There are additional register pages reserved for system areas that are protected against accidental writing during operation. The memory data is kept in nonvolatile memories.

Table 1: AR49 Encoder Memory Overview

| For S    | PI/RS485 | For I    | BiSS-C  |                                                                           |

|----------|----------|----------|---------|---------------------------------------------------------------------------|

| Page     | Address  | Bank     | Address | Content                                                                   |

|          | 0x00     |          | 0x00    |                                                                           |

| 0 to 4   | ::       | 0 to 9   | ::      | Nonvolatile Memory (External EEPROM) – User                               |

|          | 0x7E     |          | 0x3F    |                                                                           |

|          | 0x00     |          | 0x00    |                                                                           |

| 5        | ::       | 10 to 11 | ::      | Nonvolatile Memory (Internal – Accuracy, Sub-grating Correction, IEC LUT) |

|          | 0x7E     |          | 0x3F    |                                                                           |

|          | 0x00     |          | 0x00    |                                                                           |

| 6        | ::       | 12 to 13 | ::      | Nonvolatile Memory (Internal – Accuracy, Once-Around Correction, OAC LUT) |

|          | 0x7E     |          | 0x3F    |                                                                           |

|          | 0x00     |          | 0x00    |                                                                           |

| 7        | ::       | 14 to 15 | ::      | Nonvolatile Memory (Internal) – System-User Area                          |

|          | 0x7E     |          | 0x3F    |                                                                           |

|          | 0x00     |          | 0x00    |                                                                           |

| 8        | ::       | 16 to 17 | ::      | Nonvolatile Memory (Internal) – System-Factory Area                       |

|          | 0x7E     |          | 0x3F    |                                                                           |

|          | 0x00     |          | 0x00    |                                                                           |

| 9 to 10  | ::       | 18 to 21 | ::      | Fixed Volatile Memory (Registers)                                         |

|          | 0x7E     |          | 0x3F    |                                                                           |

|          | 0x00     |          | 0x00    |                                                                           |

| 11 to 13 | ::       | 22 to 27 | ::      | Nonvolatile Memory (External EEPROM) – User                               |

|          | 0x7E     |          | 0x3F    |                                                                           |

### SPI/RS485 Memory

- A total of 8 pages with 127 addresses each are allocated for user access.

- The active page numbers are specified in address 0x7F. Page change is done by writing to address 0x7F. The default page after power-on is Page 0.

- Once the page value is changed, allow a time delay of 18 ms.

- Typical EEPROM read time is 200 µs minimum.

- Typical EEPROM write time is 6 ms minimum.

- Page 9 and 10 are volatile memory addresses reserved for encoder system use.

### **BiSS-C Memory**

- A total of 16 banks with 64 addresses each are allocated for user access.

- The active page numbers are specified in address 0x40.

- Bank change is done by writing to address 0x40.

- Banks 18 to 21 are volatile memory addresses reserved for encoder system use.

AR49-Series-AN101 Broadcom

# **System Memory for Encoder Configuration**

Table 2: Encoder Memory Map for Calibration and Special Commands

|       | BiSS-C |       | Standar | d SSI/SF | PI/RS485 |                     |                  | AR49                 | Registers a         | and Comma             | nds                   |                          |                          |

|-------|--------|-------|---------|----------|----------|---------------------|------------------|----------------------|---------------------|-----------------------|-----------------------|--------------------------|--------------------------|

| Bank  | Add    | ress  | Page    | Add      | ress     |                     |                  |                      | Bi                  | t                     |                       |                          |                          |

| [dec] | [dec]  | [hex] | [dec]   | [dec]    | [hex]    | 7                   | 6                | 5                    | 4                   | 3                     | 2                     | 1                        | 0                        |

|       | 0      | 00    |         | 0        | 00       |                     |                  | Ur                   | nlock Registe       | r Write (ABh          | )                     |                          |                          |

|       | 1      | 01    |         | 1        | 01       |                     |                  |                      | Memory Prog         | gram (C0h)            |                       |                          |                          |

|       | 2      | 02    |         | 2        | 02       |                     |                  |                      |                     |                       | Alarm<br>Clear        | ST Offset                | MT Offset                |

|       | 3      | 03    |         | 3        | 03       |                     |                  | Factory Re           | eserved (USE        | R Prohibited          | d Access)             |                          |                          |

|       | 4      | 04    |         | 4        | 04       |                     |                  |                      |                     |                       |                       | AutoCal_<br>NoAcc_<br>En | AutoCal_<br>Full_En      |

|       | 5      | 05    |         | 5        | 05       |                     | IEC_<br>Cal_En   | Acc_Cal_<br>RST      | Acc_<br>Cal2_En     | Acc_<br>Cal1_En       | MPhase_<br>En         | MLS_<br>Vpp_Cal_<br>En   | Inc_Cal_<br>En           |

|       | 6      | 06    |         | 6        | 06       |                     |                  |                      | MT_Sync_<br>En      | CMA_<br>CCW_En        | CMA_<br>CW_En         | FeRAM_<br>Clear          | CM_Test_<br>En           |

|       | 8      | 08    |         | 8        | 08       |                     |                  |                      |                     |                       | Vwc_<br>Mon_En        | CMA_<br>Clear_ EN        | XC_<br>Comp_<br>Clear_En |

|       | 9      | 09    |         | 9        | 09       |                     | 1                | ŀ                    | EHMT Regist         | ter Byte 0x7          |                       |                          |                          |

|       | 10     | 0A    |         | 10       | 0A       | EHMT_<br>Test_ Mode |                  |                      |                     |                       |                       |                          |                          |

| 18    | 11     | 0B    | 9       | 11       | 0B       |                     |                  | Н                    | ard Reset Re        | egister (A7h)         |                       |                          |                          |

|       | 13     | 0D    |         | 13       | 0D       |                     |                  |                      | EHMT Paran          | neter [15:8]          |                       |                          |                          |

|       | 14     | 0E    |         | 14       | 0E       |                     |                  |                      | EHMT Para           | meter [7:0]           |                       |                          |                          |

|       | 15     | 0F    |         | 15       | 0F       |                     |                  |                      | EHMT CI             | MD[7:0]               |                       |                          |                          |

|       | 34     | 0x22  |         | 34       | 0x22     |                     | Reserved         |                      | TempErr             | Memory<br>Err         | Config<br>Code Err    | STErr                    | MLSErr                   |

|       | 35     | 0x23  |         | 35       | 0x23     |                     | Rese             | erved                |                     | Reserved              | Reserved              | LisErr<br>(IncErr)       | LedErr                   |

|       | 40     | 28    |         | 40       | 28       |                     |                  |                      |                     |                       |                       | AutoCal_<br>Error        | Auto_<br>Cal_<br>Done    |

|       | 41     | 29    |         | 41       | 29       | Acc_Cal_<br>Err     | Acc_Cal_<br>Done | MPhase_<br>Error     | MPhase_<br>Done     | MLS_<br>Vpp_<br>Error | MLS_<br>Vpp_<br>Done  | Inc_Cal_<br>Error        | INC_Cal_<br>Done         |

|       | 42     | 2A    |         | 42       | 2A       | EEPROM_<br>Err      |                  |                      |                     |                       | CM_<br>Test_<br>Done  |                          |                          |

|       | 43     | 2B    |         | 43       | 2B       |                     | CMA_<br>Busy     | CMA_<br>CCW_<br>Done | CMA_<br>CW_<br>Done | EHMT_<br>Error        | EHMT_<br>XC_<br>Alarm | CMA_<br>Error            |                          |

### NOTE:

- The memory program command is needed for the system area memory to be effective upon power cycle; applicable for changes to internal memory pages 5 to 8 (banks 10 to 17).

- Perform the memory program command for changes to any of the affected banks before moving to other nonvolatile memory banks.

- Changes will be lost after a power cycle without a memory program command.

#### **Change Memory Page/Bank**

- 1. Write the required page value in hex into Address 0x7F. For example, Data 09h (Go to Page 9) for RS485/SPI.

- 2. Write the required bank value in hex into Address 0x40. For example, Data 12h (Go to Bank 18) for BiSS-C.

#### **Unlock Register Write**

- 1. Go to Page 9, 0x09 (BiSS-C Bank 18, 0x12).

- 2. Write address 0x00: Data ABh (unlock Level 1).

#### **Memory Programming**

- 1. Go to Page 9, 0x09 (BiSS-C Bank 18, 0x12).

- 2. Write address 0x01: Data C0h (page programming).

- 3. Wait at least 320 ms.

- 4. Power cycle the encoder.

#### **EHMT Counter Soft Reset**

- 1. Unlock Register Write.

- 2. Go to Page 9, 0x09 (BiSS-C Bank 18, 0x12).

- 3. Write address 0x0F: Data 0Fh.

Table 3: Encoder Memory Map for MT Related Data

|       | Standard |       |       | BiSS-C |       |                                 | En | ergy-Ha | arvesting | Multi-T   | urn (EHI  | MT) |   |

|-------|----------|-------|-------|--------|-------|---------------------------------|----|---------|-----------|-----------|-----------|-----|---|

| Page  | Add      | ress  | Bank  | Add    | dress |                                 |    |         | E         | Bit       |           |     |   |

| [dec] | [dec]    | [hex] | [dec] | [dec]  | [hex] | 7                               | 6  | 5       | 4         | 3         | 2         | 1   | 0 |

|       | 57       | 39    |       | 57     | 39    |                                 |    | Е       | HMT Ret   | urned D   | ata       | 1   |   |

|       | 62       | 3E    | 18    | 62     | 3E    | EHMT CMA Offset Value [15:8]    |    |         |           |           |           |     |   |

|       | 63       | 3F    |       | 63     | 3F    | EHMT CMA Offset Value [7:0]     |    |         |           |           |           |     |   |

|       | 64       | 40    |       | 0      | 00    | EHMT_XC_ERR_Compensation [15:8] |    |         |           |           |           |     |   |

|       | 65       | 41    |       | 1      | 01    |                                 | Е  | HMT_X   | C_ERR_    | Compen    | sation [7 | :0] |   |

| 9     | 66       | 42    |       | 2      | 02    |                                 |    |         | 1N4T A1 A | DMAD      | utoo      |     |   |

|       | 67       | 43    | 19    | 3      | 03    |                                 |    | ЕГ      | HMT_ALA   | ARIVI Z D | ytes      |     |   |

|       | 68       | 44    | 19    | 4      | 04    | FUNT OL 4 O D 4                 |    |         |           |           |           |     |   |

|       | 69       | 45    |       | 5      | 05    | EHMT Status 2 Bytes             |    |         |           |           |           |     |   |

|       | 70       | 46    |       | 6      | 06    | EHMT_VWC_DATA 2 Bytes           |    |         |           |           |           |     |   |

|       | 71       | 47    |       | 7      | 07    | ETHINT_VWC_DATA 2 Bytes         |    |         |           |           |           |     |   |

**Table 4: EHMT Status and Alarm Registers**

|       | BiSS-C |       |       | Standard | d     |                  |              | Energ           | y-Harvesti      | ng Multi-Turr       | (EHMT)              |                    |             |

|-------|--------|-------|-------|----------|-------|------------------|--------------|-----------------|-----------------|---------------------|---------------------|--------------------|-------------|

| Bank  | Add    | ress  | Page  | Add      | ress  |                  |              |                 |                 | Bit                 |                     |                    |             |

| [dec] | [dec]  | [hex] | [dec] | [dec]    | [hex] | 7                | 6            | 5               | 4               | 3                   | 2                   | 1                  | 0           |

|       | 02     | 0x02  |       | 66       | 0X42  |                  |              |                 |                 |                     |                     | MemErr             | MagLO       |

|       | 03     | 0x03  |       | 67       | 0x43  | VWC<br>Quality   | XC_<br>Error | CMA_<br>Timeout | VWC_<br>Timeout | Speed_<br>VWC       | Speed_<br>CMA       | Speed_<br>MT       | MT Error    |

| 19    | 04     | 0x04  | 9     | 68       | 0x44  | Alarm<br>Trigger |              |                 | DUT<br>Ready    |                     |                     |                    |             |

|       | 05     | 0x05  |       | 69       | 0x45  |                  |              | Reserved        | Reserved        | VWC Result<br>Ready | CMA<br>CCW<br>Ready | CMA<br>CW<br>Ready | MT<br>Ready |

# **Register Bit for Counting Direction Selection**

**Table 5: Encoder Counting Direction**

| Page      | Address |     | Bit                   |     |   |   |   |   |   |               |  |  |

|-----------|---------|-----|-----------------------|-----|---|---|---|---|---|---------------|--|--|

| [Decimal] | [hex]   | 7   | 6                     | 5   | 4 | 3 | 2 | 1 | 0 | Default Value |  |  |

| 7         | 20      | N/A | Counting<br>Direction | N/A |   |   |   |   |   | 8'h40h        |  |  |

With the default setting (bit 6 = 0), position data is counting up when rotating in a counter-clockwise direction, as viewed from the top of the encoder.

Figure 7: Default Counting Direction

View from the top

### **Position Zero Reset**

The encoder zero reset data can be accessed by reading the addresses in Table 6.

Table 6: User Zero-Reset Registers

| Page  |       | RS485<br>dress | Bank  | BiSS-C | Address |                 | Bit         |  |       |          |  | Default |     |     |

|-------|-------|----------------|-------|--------|---------|-----------------|-------------|--|-------|----------|--|---------|-----|-----|

| [dec] | [dec] | [dec]          | [dec] | [hex]  | [hex]   | 7 6 5 4 3 2 1 0 |             |  |       |          |  |         |     |     |

|       | 16    | 10             |       | 16     | 10      |                 |             |  | MT_ZF | R[23:16] |  |         |     | 00h |

|       | 17    | 11             |       | 17     | 11      |                 | MT_ZR[15:8] |  |       |          |  |         | 00h |     |

| 7     | 18    | 12             | 14    | 18     | 12      |                 |             |  | MT_Z  | :R[7:0]  |  |         |     | 00h |

| /     | 19    | 13             | 14    | 19     | 13      | ST_ZR[24:17]    |             |  |       |          |  |         | 00h |     |

|       | 20    | 14             |       | 20     | 14      | ST_ZR[16:9]     |             |  |       |          |  |         | 00h |     |

|       | 21    | 15             |       | 21     | 15      | ST_ZR[8:1]      |             |  |       |          |  | 00h     |     |     |

### **Auto Zero-Reset (Single-Turn Position)**

When the codewheel/hub is stationary, execute the ST Reset command so that the single-turn position output value will be reset to the zero value.

- 1. Option 1 with memory bit setting:

- a. Unlock Register Write.

- b. Write Page 9/Bank 18, Address 0x02[1] = 1b.

- 2. Option 2 with the dedicated zero reset commands for the RS485, SPI or BiSS-C protocols.

## **Auto Zero-Reset (Multi-Turn Counter Output)**

- 1. Option 1 with memory bit setting:

- a. Unlock Register Write.

- b. Write to Page 9/Bank 18, Address 0x02[0] = 1b.

- 2. Option 2 with the dedicated multi-turn zero reset commands for the RS485, SPI or BiSS-C protocols.

The multi-turn value will be reset to the zero value when this command is completed.

# Multi-Turn and Single-Turn Absolute Resolution Setting

Select the configuration for the absolute position output by updating the Page 7/Bank 14 Address 0x16, see Table 7 and Table 8.

- 1. Unlock Register Write.

- 2. Write in the new settings at Page 7/Bank 14, read back to ensure the setting is written successfully.

- 3. Program memory.

Table 7: Multi-Turn and Single-Turn Bits Setting Description for SPI/SSI/BiSS-C Protocols

| Page (SPI/SSI) | Bank<br>(BiSS-C) | Address | Bits | Name             | Settings | SPI/SSI<br>25-Bit Output |

|----------------|------------------|---------|------|------------------|----------|--------------------------|

|                |                  |         | 7    | Reserved         | Х        | N/A                      |

|                |                  |         |      |                  | 000      | 0                        |

|                |                  |         |      |                  | 001      | 12                       |

|                |                  |         |      |                  | 010      | 14                       |

|                |                  |         | 6.4  | MT. Coloct [O:0] | 011      | 16                       |

|                | 0x0E             | 0x16    | 6:4  | MT_Select [2:0]  | 100      | 18                       |

|                |                  |         |      |                  | 101      | 20                       |

|                |                  |         |      |                  | 110      | 22                       |

|                |                  |         |      |                  | 111      | 24                       |

|                |                  |         |      |                  | 0000     | 15                       |

| 0x07           |                  |         |      |                  | 0001     | 16                       |

|                |                  |         |      |                  | 0010     | 17                       |

|                |                  |         |      |                  | 0011     | 18                       |

|                |                  |         |      |                  | 0100     | 19                       |

|                |                  |         | 2.0  | CT Colort [2:0]  | 0101     | 20                       |

|                |                  |         | 3:0  | ST_Select [3:0]  | 0110     | 21                       |

|                |                  |         |      |                  | 0111     | 22                       |

|                |                  |         |      |                  | 1000     | 23                       |

|                |                  |         |      |                  | 1001     | 24                       |

|                |                  |         |      |                  | 101x     | 25                       |

|                |                  |         |      |                  | 11xx     | 25                       |

NOTE: For ST only option, the MT selection is defaulted to binary 000.

Table 8: Multi-Turn and Single-Turn Bits Setting Description for RS485 Protocols

| Page | Address | Bits | Name            | Settings | RS485 24 Bits ST Output | RS485 25 Bits ST Output |

|------|---------|------|-----------------|----------|-------------------------|-------------------------|

|      |         | 7    | Reserved        | х        | N/A                     | N/A                     |

|      |         |      |                 | 000      | 0                       | 0                       |

|      |         |      |                 | 001      | 12                      | 12                      |

|      |         |      |                 | 010      | 14                      | 14                      |

|      |         | C. 1 | MT Calact [0:0] | 011      | 16                      | 16                      |

|      |         | 6:4  | MT_Select [2:0] | 100      | 18                      |                         |

|      |         |      |                 | 101      | 20                      | NI/A                    |

|      |         |      |                 | 110      | 22                      | N/A                     |

|      |         |      |                 | 111      | 24                      |                         |

| 0x07 | 0x16    |      |                 | 0000     | 17                      | 15                      |

| UXU7 | UXIO    |      |                 | 0001     | 18                      | 16                      |

|      |         |      |                 | 0010     | 19                      | 17                      |

|      |         |      |                 | 0011     | 20                      | 18                      |

|      |         |      |                 | 0100     | 21                      | 19                      |

|      |         | 3:0  | ST_Select [3:0] | 0101     | 22                      | 20                      |

|      |         |      |                 | 0110     | 23                      | 21                      |

|      |         |      |                 | 0111     | 24                      | 22                      |

|      |         |      |                 | 1000     |                         | 23                      |

|      |         |      |                 | 1001     | N/A                     | 24                      |

|      |         |      |                 | 1010     |                         | 25                      |

# **Encoder Error and Warning Setting**

To enable the Error or Warning bits in the ALMC field, set the respective bit to 1, disable 0.

Table 9: Error and Warning Bits Configuration Addresses

| Page | Address [hex]           | 7                        | 6 | 5     | 4       | 3        | 2                | 1 | 0   | Default Value |  |  |

|------|-------------------------|--------------------------|---|-------|---------|----------|------------------|---|-----|---------------|--|--|

|      | 30 Alarm Enable [31:24] |                          |   |       |         |          |                  |   | 1Fh |               |  |  |

|      | 31                      |                          |   | Ala   | FFh     |          |                  |   |     |               |  |  |

|      | 32                      |                          |   | Al    | arm En  | able [15 | :8]              |   |     | 1Bh           |  |  |

| 7    | 33                      |                          |   | Α     | larm Er | able [7: | 0]               |   |     | 0Fh           |  |  |

| ,    | 34                      |                          |   | Alarm | Latch E | nable [  | able [31:24] 1Fh |   |     |               |  |  |

|      | 35                      |                          |   |       |         |          |                  |   |     |               |  |  |

|      | 36                      |                          |   | Alarn | 0Bh     |          |                  |   |     |               |  |  |

|      | 37                      | Alarm Latch Enable [7:0] |   |       |         |          |                  |   |     | 0Eh           |  |  |

Table 10: AR49 Alarm Bits Assignment

|      | Alarm Bits |       |               |              |                 |              |              |  |

|------|------------|-------|---------------|--------------|-----------------|--------------|--------------|--|

| 31   | 30         | 29    | 28            | 27           | 26              | 25           | 24           |  |

|      | Reserved   | •     | MT Sync Error | Reserved     | MT Protocol Err | Rese         | erved        |  |

| 23   | 22         | 21    | 20            | 19           | 18              | 17           | 16           |  |

| Rese | erved      | XCErr | Reserved      | EHMT Counter | EHMT Counter    | EHMT Counter | EHMT Counter |  |

|      |            |       |               | Err[9:3]     | Err[2]          | Err[1]       | Err[0]       |  |

| 15   | 14         | 13    | 12            | 11           | 10              | 9            | 8            |  |

|      | Reserved   |       | TempErr       | Memory       | Reserved        | STErr        | MLSErr       |  |

|      |            |       |               | Err          |                 |              | (McodeErr)   |  |

| 7    | 6          | 5     | 4             | 3            | 2               | 1            | 0            |  |

|      |            | Res   | served        |              |                 | LisErr       | LEDErr       |  |

|      |            |       |               |              |                 | (IncErr)     |              |  |

# **SPI4 Error or Warning Readout and Descriptions**

For SPI4 protocol option, send the operation command (OC) 0x9Ch to perform error or warning bits readout. To perform segregation between Error or Warning bits, see the AR49 alarm bits settings in Table 10. Enable the Error or Warning bits in the operation command (OC) 0x9Ch by setting the respective bit to 1. Conversely, setting a bit to 0 will disable the particular bit.

Table 11: SPI4 Protocol Error and Warning Bits Masking Assignment

| Page | Address [hex]                | 7                        | 6 | 5    | 4         | 3        | 2       | 1 | 0 | Default Value |

|------|------------------------------|--------------------------|---|------|-----------|----------|---------|---|---|---------------|

|      | 28 SPI4 Warning Mask [31:24] |                          |   |      |           |          |         |   |   | 00h           |

|      | 29                           |                          |   | SPI4 | Warning   | Mask     | [23:16] |   |   | 10h           |

|      | 2A                           |                          |   | SPI4 | Warnin    | g Mask   | [15:8]  |   |   | 10h           |

| 7    | 2B                           |                          |   | SPI4 | l Warnir  | g Mask   | [7:0]   |   |   | 03h           |

| ,    | 2C                           |                          |   | SPI  | 4 Error I | Лask [3  | 1:24]   |   |   | 1Fh           |

|      | 2D                           |                          |   | SPI  | 4 Error I | /lask [2 | 3:16]   |   |   | EFh           |

|      | 2E                           |                          |   | SPI  | 0Bh       |          |         |   |   |               |

|      | 2F                           | 2F SPI4 Error Mask [7:0] |   |      |           |          |         |   |   | 0Ch           |

# **Encoder Alarm Definition**

The following table shows the encoder alarm bits and their definition across all protocol options.

Table 12: AR49-M49M and AR49-M25S General Encoder Alarms and Definition Table

| Alarms            | Alarms Definition                                                                                    | Check Frequency          |

|-------------------|------------------------------------------------------------------------------------------------------|--------------------------|

| TempErr           | Temperature Error.                                                                                   | Every 90 ms              |

|                   | To indicate the temperature exceeds the maximum preset limit.                                        |                          |

|                   | 1: Temperature above preset limit.                                                                   |                          |

|                   | 0: Temperature below preset limit.                                                                   |                          |

| Memory            | MEM Error (Memory Error).                                                                            | Upon power-up and memory |

| Err               | To indicate if loading of internal and external EEPROM contents upon encoder power up is successful. | read                     |

|                   | ■ 1: Failure to access EEPROM memory data/or there is a checksum error in the memory.                |                          |

|                   | 0: Normal operation, no EEPROM memory access error                                                   |                          |

| STErr             | Single-turn Counting Error.                                                                          | Per ADC sample           |

|                   | To check the integrity of ST position.                                                               |                          |

|                   | <ul><li>1: Error in Absolute (MLS) code or MLSErr flag has triggered.</li></ul>                      |                          |

|                   | 0: Normal operation, no error in single-turn position.                                               |                          |

| MLSErr (McodeErr) | To detect error in MLS code generation.                                                              | Per ADC sample           |

|                   | ■ 1: MLS code error.                                                                                 |                          |

|                   | O: MLS code good.                                                                                    |                          |

| LisErr            | Lissajous (Incremental) Error.                                                                       | Per ADC sample           |

| (IncErr)          | A measure of integrity of ADC Sin & Cos signals by means of Lissajous specifications.                |                          |

|                   | ■ 1: Lissajous out of specification.                                                                 |                          |

|                   | 0: Lissajous within specification.                                                                   |                          |

| LEDErr            | LED Error.                                                                                           | Continuous detect        |

|                   | To indicate if LED current is out of operating range.                                                |                          |

|                   | <ul><li>1: LED out of operating range.</li></ul>                                                     |                          |

|                   | 0: LED within operating range.                                                                       |                          |

Table 13: AR49-M49M Encoder Multi-Turn Alarms and Definition Table

| Alarms            | Alarms Definition                                                           | Check Frequency         |

|-------------------|-----------------------------------------------------------------------------|-------------------------|

| MT Sync Error     | EHMT Sync Error.                                                            | Upon MT synchronization |

|                   | To detect wrong MT counting during MT counter synchronization.              |                         |

|                   | ■ 1: Error in multi-turn synchronization.                                   |                         |

|                   | 0: No error in multi-turn synchronization.                                  |                         |

| MT Protocol Error | To detect an MT encoder protocol error – energy harvesting (Wiegand).       | Per MT encoder polling  |

|                   | ■ 1: MT encoder protocol error.                                             |                         |

|                   | 0: No MT encoder protocol error.                                            |                         |

| XCErr             | To indicate an MT encoder miscount by comparing the EHMT counter vs. the MT | Each time ST rolls over |

|                   | software counter.                                                           |                         |

|                   | <ul><li>1: EHMT: Miscount or XCERR value overflow.</li></ul>                |                         |

|                   | ■ 0: No MT miscount.                                                        |                         |

Table 13: AR49-M49M Encoder Multi-Turn Alarms and Definition Table (Continued)

| Alarms                | Alarms Definition                                                                                                                             | Check Frequency        |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| EHMT Counter Err[9:3] | MT Counter Error.                                                                                                                             | Per MT encoder polling |

|                       | To detect error receive from EHMT counter.                                                                                                    |                        |

|                       | ■ 1: EHMT Counter Error Bits [9:3] triggers.                                                                                                  |                        |

|                       | 0: No EHMT counter errors.                                                                                                                    |                        |

| EHMT Counter Err[2]   | MT Counter Error.                                                                                                                             | Per MT encoder polling |

|                       | To detect Error receive from EHMT counter.                                                                                                    |                        |

|                       | ■ 1: EHMT Counter Error Bit[2] triggers.                                                                                                      |                        |

|                       | 0: No EHMT Counter Errors                                                                                                                     |                        |

| EHMT Counter Err[1]   | MT Counter Error.                                                                                                                             | Per MT encoder polling |

|                       | To detect error receive from EHMT counter.                                                                                                    |                        |

|                       | ■ 1: EHMT Counter Error Bit[1] triggers.                                                                                                      |                        |

|                       | 0: No EHMT counter errors.                                                                                                                    |                        |

| EHMT Counter Err[0]   | MT Error.                                                                                                                                     | Per MT encoder polling |

|                       | To detect error on reading MT Hardware counter value or I <sup>2</sup> C communication error.                                                 |                        |

|                       | <ul><li>1: Error in MT position reading, the EHMT Counter Error Bit[0] triggers.</li><li>0: No error in MT position reading.</li></ul>        |                        |

| MT Counter Error      | MT Counter Error.                                                                                                                             | Per MT encoder polling |

|                       | To detect Error bit received from the EHMT Counter Error register.                                                                            |                        |

|                       | ■ 1: Any of the EHMT Counter Err[9:1] bit triggers.                                                                                           |                        |

|                       | 0: No EHMT counter error.                                                                                                                     |                        |

| MT Error              | MT Error for BiSS-C and RS485 Protocols.                                                                                                      | Per MT encoder polling |

|                       | To detect error on reading MT hardware counter value or I <sup>2</sup> C communication error. Same as the EHMT Counter Error Bit[0] triggers. |                        |

Table 14: AR49-M49M EHMT Counter Error Register Definition

| EHMT Counter Error Bit | Name             | EHMT Counter Error[9:0] Description                                          |

|------------------------|------------------|------------------------------------------------------------------------------|

| 0                      | MT Error         | Error occurs on reading hardware multi-turn value or I <sup>2</sup> C stuck. |

| 1                      | Speed_MT         | Motor exceeds 15000RPM for MT synchronization.                               |

| 2                      | Speed_CMA        | Motor exceeds 200RPM for CMA calibration.                                    |

| 3                      | Speed_VWC        | Motor exceeds speed limit for VWC monitoring.                                |

| 4                      | VWC_Timeout      | Less than 700 VWC pulses detected within 90 seconds.                         |

| 5                      | CMA_Timeout      | VWC pulses not detected within 10 seconds.                                   |

| 6                      | Counter XC_Error | Continuous miscount for 5 revolutions.                                       |

| 7                      | VWC Quality      | VWC voltage less than 4.0V.                                                  |

| 8                      | MT_MagLO         | MT Counter ASIC detects no or low magnetic field.                            |

| 9                      | MT_MemErr        | FeRAM related error.                                                         |

### **Alarm Clear:**

- 1. Option 1 with memory bit setting

- a. Unlock Register Write.

- b. Write to Page 9/Bank 18, Address 0x02[2] = 1b.

- 2. Option 2 with Alarm Clear Command of the respective RS485, SPI, or BiSS-C protocols.

# **Temperature Sensor**

For the setting of temperature values and alarms, the configuration is as listed in Table 15. The temperature upper limit is defaulted to 0x7D, which is 125°C, referenced to the ambient temperature as measured by the AR49 encoder ASIC. The encoder temperature readout bit, which is an example of the data as 2's complement, is listed in Table 17.

Table 15: SSI/SPI/RS485 Temperature Sensor Setting

| S     | SI/SPI/RS4 | 85    |     |                                              |       |             |               |           |   |  |     |  |  |

|-------|------------|-------|-----|----------------------------------------------|-------|-------------|---------------|-----------|---|--|-----|--|--|

| Page  | Add        | ress  | Bit |                                              |       |             |               |           |   |  |     |  |  |

| [dec] | [dec]      | [hex] | 7   | 7 6 5 4 3 2 1 0                              |       |             |               |           |   |  |     |  |  |

|       | 2          | 02    |     | 1                                            | Tempe | rature Uppe | er Limit Offs | set [7:0] | 1 |  | 00h |  |  |

| 7     | 3          | 03    |     |                                              | 7     | Temperature | e Offset [7:0 | 0]        |   |  | 00h |  |  |

| ,     | 4          | 04    |     | Temperature Upper Limit [7:0]                |       |             |               |           |   |  |     |  |  |

|       | 5          | 05    |     | Temperature Output Data (Read only register) |       |             |               |           |   |  |     |  |  |

Table 16: BiSS-C Temperature Sensor Setting

|       | BiSS-C |             |   |                 |            |             |               |                |   |  |         |  |  |

|-------|--------|-------------|---|-----------------|------------|-------------|---------------|----------------|---|--|---------|--|--|

| Bank  | Addı   | Address Bit |   |                 |            |             |               |                |   |  | Default |  |  |

| [dec] | [dec]  | [hex]       | 7 | 7 6 5 4 3 2 1 0 |            |             |               |                |   |  |         |  |  |

|       | 2      | 02          |   |                 | Tempe      | rature Uppe | er Limit Offs | set [7:0]      |   |  | 00h     |  |  |

| 14    | 3      | 03          |   |                 | T          | emperature  | Offset [7:0   | 0]             |   |  | 00h     |  |  |

| 14    | 4      | 04          |   |                 | Ten        | perature U  | pper Limit    | [7:0]          |   |  | 7Dh     |  |  |

|       | 5      | 05          |   |                 | Temperatur | e Output Da | ata (Read c   | only register) | ) |  | _       |  |  |

|       | 117    | 75          |   |                 | Temperatur | e Output Da | ata (Read c   | only register) | ) |  | _       |  |  |

| _     | 73     | 49          |   |                 |            |             |               | Temp.<br>Alarm |   |  | 0       |  |  |

Table 17 is an example based on an initial alarm (Page 7/Bank 14, Address 0x04) setting of 125°C. The temperature offset can be a positive or negative value.

**Table 17: Temperature Sensor Offset Setting Example**

|      | Temperature<br>Sensor Offset<br>Register | 0x02                                       | 0x03                        | 0x04                             | 0x05                        | Remark                                     | s                |

|------|------------------------------------------|--------------------------------------------|-----------------------------|----------------------------------|-----------------------------|--------------------------------------------|------------------|

| Case | Offset Value<br>(Decimal)                | Temperature<br>Upper Limit<br>Offset (hex) | Temperature<br>Offset (hex) | Temperature<br>Upper Limit (hex) | Temperature<br>Output (Dec) | Raw Temperature<br>without Offset<br>(Dec) | Alarm<br>Trigger |

|      |                                          |                                            |                             |                                  | 124                         | 124                                        | No               |

| 1    | 0                                        | 0                                          | 0                           | 7D                               | 125                         | 125                                        | Yes              |

|      |                                          |                                            |                             |                                  | 126                         | 126                                        | Yes              |

|      |                                          |                                            |                             |                                  | 124                         | 114                                        | No               |

| 2    | 10                                       | 0A                                         | 0A                          | 7D                               | 125                         | 115                                        | Yes              |

|      |                                          |                                            |                             |                                  | 126                         | 116                                        | Yes              |

Table 17: Temperature Sensor Offset Setting Example (Continued)

|      | Temperature<br>Sensor Offset<br>Register | Sensor Offset                              |                             | set                              |                             |     | 0x05             | Remarks |  |  |  |

|------|------------------------------------------|--------------------------------------------|-----------------------------|----------------------------------|-----------------------------|-----|------------------|---------|--|--|--|

| Case | Offset Value<br>(Decimal)                | Temperature<br>Upper Limit<br>Offset (hex) | Temperature<br>Offset (hex) | Temperature<br>Upper Limit (hex) | Temperature<br>Output (Dec) |     | Alarm<br>Trigger |         |  |  |  |

|      |                                          |                                            |                             |                                  | 124                         | 125 | No               |         |  |  |  |

| 3    | -1                                       | 0                                          | FF                          | 7D+01                            | 125                         | 126 | Yes              |         |  |  |  |

|      |                                          |                                            |                             |                                  | 126                         | 127 | Yes              |         |  |  |  |

|      |                                          |                                            |                             |                                  | 124                         | 134 | No               |         |  |  |  |

| 4    | -10                                      | 0                                          | F6                          | 7D+0A                            | 125                         | 135 | Yes              |         |  |  |  |

|      |                                          |                                            |                             |                                  | 126                         | 136 | Yes              |         |  |  |  |

#### NOTE:

- Case 1: No offset scenario.

- Case 2: If the temperature offset (Address 0x03) is a positive value, the temperature upper limit offset (Address 0x02) is also set to the same value.

- Case 3: If the temperature offset (Address 0x03) is a negative value, the absolute value of this value must be added to the default temperature upper limit (Address 0x04).

- Case 4: Another negative offset value example.

- The register addresses are at SPI/RS485 Page 7 or BiSS-C Bank14.

**Table 18: Temperature Sensor Data**

| Temperature | TEMP[7:0] |

|-------------|-----------|

| -64         | 1100 0000 |

| -50         | 1100 1110 |

| -20         | 1110 1100 |

| -1          | 1111 1111 |

| 0           | 0000 0000 |

| 1           | 0000 0001 |

| 10          | 0000 1010 |

| 25          | 0001 1001 |

| 50          | 0011 0010 |

| 85          | 0101 0101 |

| 127         | 0111 1111 |

| 159         | 1001 1111 |

| 191         | 1011 1111 |

#### NOTE:

- The minimum support range for temperature output is -64°C.

- The negative values are from -1°C to -64°C only.

- The maximum positive value is 191°C.

- The temperature readout is found by accessing memory register at Page 7 Address 0x05 (see Table 15).

- For BiSS-C, the temperature readout is found by accessing the memory register at Address 0x75 (see Table 16).

- When reading using RS485-24-Bit format Command ID4 as per Table 39, the temperature data (TEMP) is available as the DF<sub>7</sub>.

# **Encoder Calibration**

The Broadcom encoder employs an intelligent calibration method by performing an auto signal optimization once the encoder is mounted within assembly tolerances. This eliminates the hassle of mechanically adjusting the encoder position to a very tight gap and mechanical center.

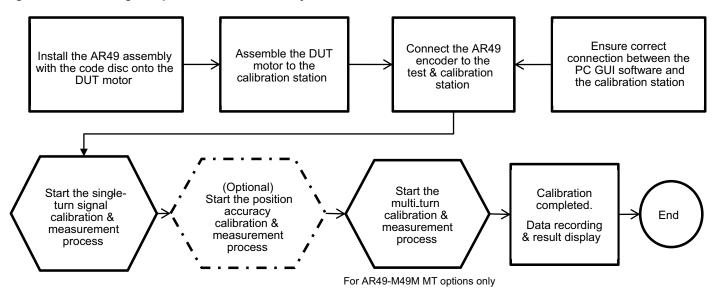

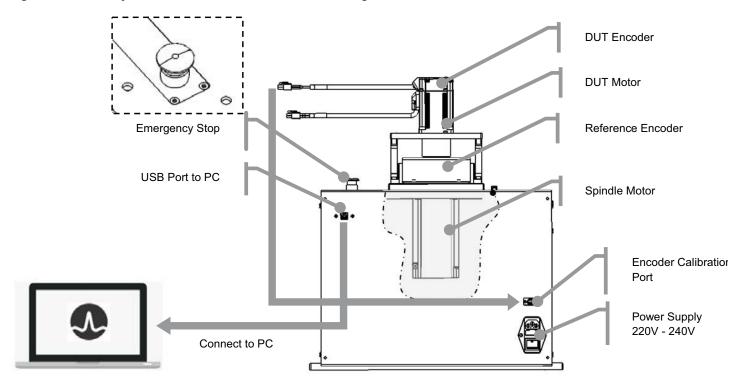

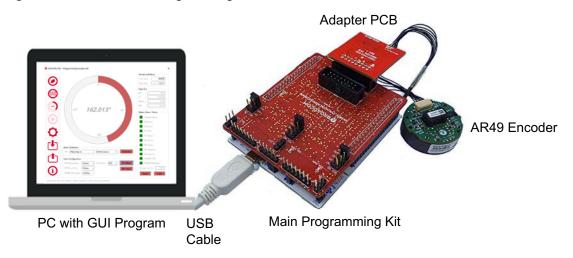

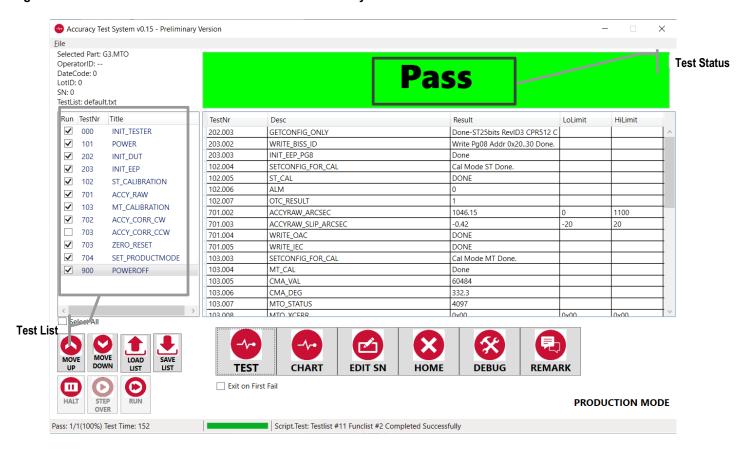

Figure 8: Encoder Signal Optimization and Accuracy Calibration Flow

Upon completion of the encoder assembly to the motor, perform the calibration process as follows:

- 1. Connect the AR49-M49-E01 programming and calibration kit to a computer via USB connection.

- 2. Connect encoder cable-end to encoder.

- 3. Follow the required steps to complete the ST and MT calibrations.

- 4. Update any user-specific configurations after calibration is completed.

- 5. The encoder is ready to use.

### NOTE:

- If the calibration continues to fail after consecutive trials, confirm the encoder codewheel and module installation again by referring to the codewheel and encoder mounting requirements and guidelines.

- Clear the ST and MT offset registers to all zeros before starting the ST and MT calibration process.

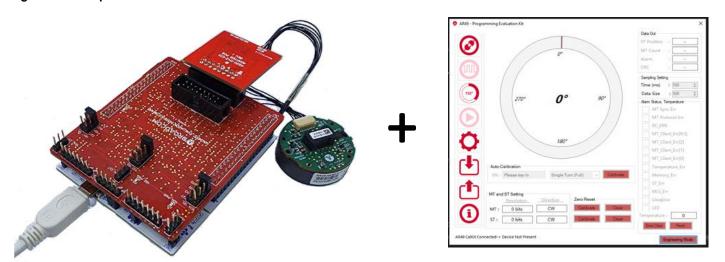

Figure 9: Example of the AR49-M49-E01 Calibration Kit and Its User Interface Software

The Programming/Calibration Kit with a USB PC Interface Cable and an Encoder Connecting Cable

The Programming/Calibration GUI Software

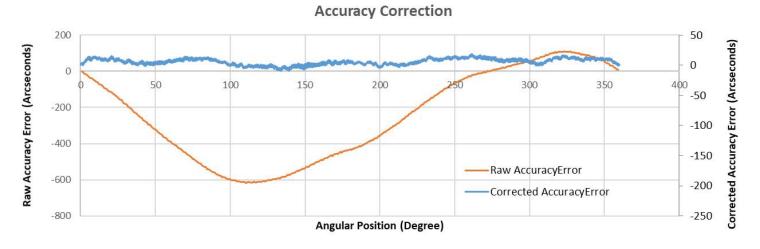

# **ST Angular Position Accuracy Correction**

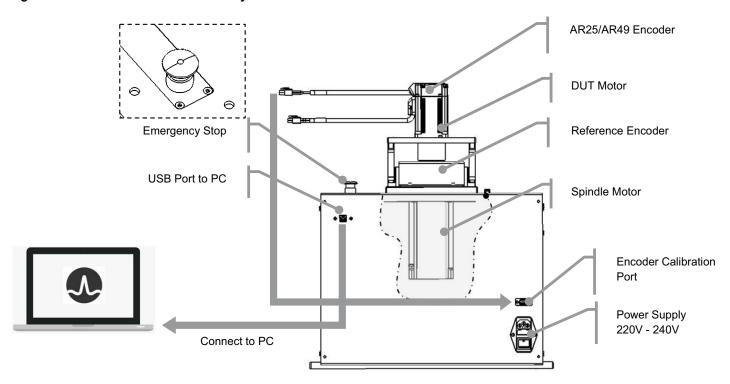

Figure 10: Accuracy Correction with Reference Encoder Using the AR25-AC25 Calibration Station

Figure 11: Example of the Position Accuracy Error Before and After Correction

## ST Calibration of the AR49-M49M/M25S Encoders

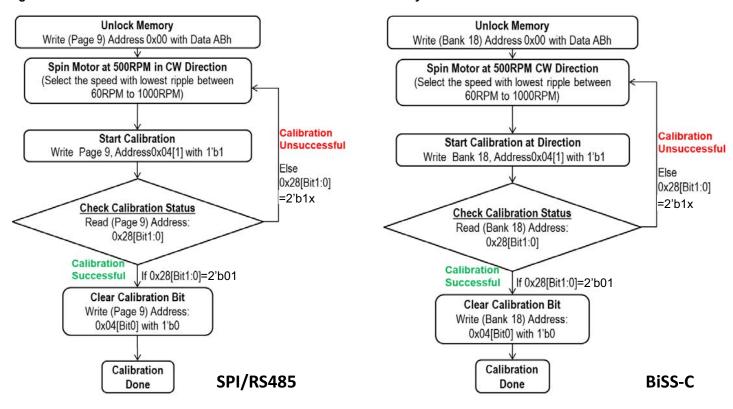

## ST Auto-Calibration without Accuracy Correction

The position accuracy correction table will not be updated. The other signals' calibration after assembly will be performed. It is recommended to perform this calibration option unless the spindle motor (to drive the AR49 + motor assembly) can fulfill the low-speed ripple requirements for accuracy correction.

- 1. Unlock memory (Write Page 9/Bank 18, Address 0x00 = ABh).

- 2. Spin the spindle motor in a clockwise (CW) direction at a fixed constant speed. It is recommended to be within 60 rpm to 1000 rpm. Wait for the motor speed to be stable before starting the next step.

- 3. Write Page 9/Bank 18, Address 0x04[1] = 1b1.

- 4. Loop reading calibration status at Address 0x28.

- 5. If Address 0x28[1:0] = 00b, the calibration is in progress. Otherwise, if the value is 01b, the calibration is done; or if the value is 1xb, there is a calibration error and the calibration is not successful.

- 6. Clear the calibration register, Address 0x04 = 00h. If unsuccessful, repeat Steps 3 to 5 (repeat up to 10 times).

- 7. Check the assembly of the codewheel and encoder for any abnormality if calibration is not successful.

Figure 12: Flowchart for Full Auto-Calibration Process without Accuracy Correction

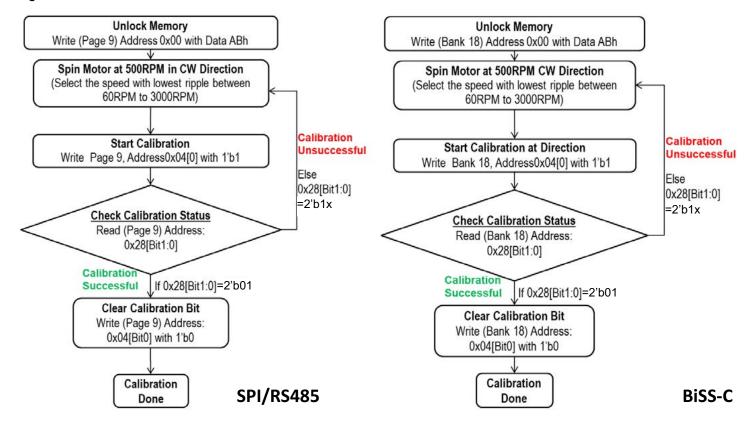

## Full ST Auto-Calibration with Accuracy Correction Enabled

Figure 13: Flowchart for Full Auto-Calibration Process

### Calibrate in Clockwise (CW) Direction

- 1. Unlock memory (Write Page 9/Bank 18, Address 0x00 = ABh).

- 2. Spin the spindle motor in a CW direction at a fixed constant speed within 60 rpm to 3000 rpm (it is recommend to select the least ripple speed, not to exceed 5000 rpm). Wait for the motor speed to be stable before starting the next step.

- 3. Write Page 9/Bank 18, Address 0x04[0] = 1b.

- 4. Loop reading calibration status at Address 0x28.

- 5. If Address 0x28[1:0] = 00b, the calibration is in progress. Otherwise, if the value is 01b, the calibration is done; or if the value is 1xb, there is a calibration error and it is not successful.

- 6. Clear the calibration register, Address 0x04 = 00h. If unsuccessful, repeat Steps 3 to 5 (repeat up to 10 times).

- 7. Check the assembly of the codewheel and encoder for any abnormality if calibration is not successful.

**CAUTION!** Only calibrate the encoder with the full auto-calibration mode with accuracy correction when the assembled AR49 encoder is being driven by a highly stable servo motor; for example, controlled to the speed of 1000 rpm ± 0.2%, or better.

**CAUTION!** The ST offset register has to be cleared to all zeros before this calibration process that involves generating the accuracy correction look-up table (LUT).

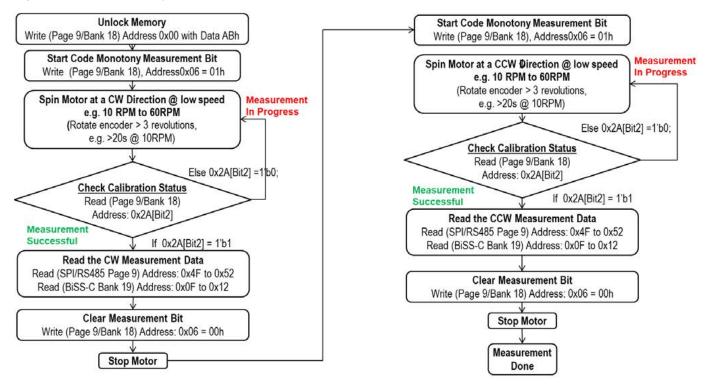

### **ST Position Code Monotony Measurement**

The AR49 encoder has a built-in function to measure and monitor the code monotony of the ST position data. This step is not mandatory but provides a way to verify that the position output after calibration is normal without any sudden shift in position data. The code monotony value is measured as a 23-bit ST step at every 10-ns interval. The readout value is in 2's complement.

- 1. Unlock memory (Write Page 9/Bank 18, Address 0x00 = ABh).

- 2. Enable the code monotony measurement by writing Page 9/Bank 18, Address 0x06 = 01h.

- 3. Spin the spindle motor in a CW direction for >3 revolutions at a low speed, for example, 2 rpm to 60 rpm.

- 4. Read Page 9, Address 0x4F to 0x52 for the measured data. For BiSS-C, read Bank 19, Address 0x0F to 0x12.

- 5. End the code monotony measurement by writing Page 9/Bank 18, Address 0x06 = 00h.

- 6. Stop the motor. Repeat Steps 2 to 5 in a counter-clockwise (CCW) direction.

Figure 14: Code Monotony Self-Test Flowchart

**Table 19: Code Monotony Measurement Registers**

| RS485         | Add   | ress  | BiSS-C        | Add   | ress               | Bit |   |   |   |           |        |   |            |

|---------------|-------|-------|---------------|-------|--------------------|-----|---|---|---|-----------|--------|---|------------|

| Page<br>[dec] | [dec] | [hex] | Bank<br>[dec] | [dec] | [hex]              | 7   | 6 | 5 | 4 | 3         | 2      | 1 | 0          |

|               | 6     | 06    | 18            | 6     | 06                 |     |   |   |   |           |        |   | CM_Test_En |

|               | 79    | 4F    |               | 15    | 15 0F CM_Max[15:0] |     |   |   |   |           |        |   |            |

| 9             | 80    | 50    | 10            | 16    | 10                 |     |   |   | C | ivi_iviax | [13.0] |   |            |

|               | 81    | 51    | 19            | 17    | 11                 |     |   |   | _ | NA Minl   | 15:01  |   |            |

|               | 82    | 52    |               | 18    | 12                 |     |   |   |   |           |        |   |            |

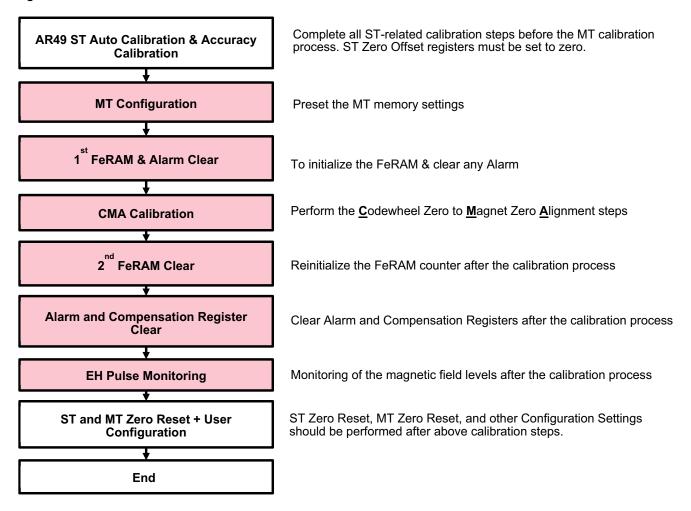

## Multi-Turn Calibration of the AR49-M49M Encoders

### **MT Calibration**

For the MT option of the AR49-M49M encoders, it is compulsory to perform the MT calibration procedures after the encoder has been assembled. For the optimum results, the shield should also be assembled during this process.

Figure 15: AR49-M49M Encoder MT Calibration Flow

### **Pre-Set the MT Memory Settings**

- 1. Motor condition: Static.

- a. Unlock Register Write.

- b. Write Address 0x7F to Data 09h (go to Page 9) or for BiSS-C: Write Address 0x40 to Data 12h (go to Bank 18).

- c. Write Address 0x00 to Data ABh (unlock level 1).

- 2. Trigger MT counter soft reset.

- a. Write Address 0x0F to Data 0Fh (trigger MT counter soft reset command). Wait 20 ms.

- 3. Set default MT configuration.

- a. Write Address 0x0A to Data 80h (MT counter test mode, Bit 7 set to High).

Table 20: MT Calibration Command and Related Registers

| Stan  | dard SS<br>RS485 |       | ı     | BiSS-C |       | Key AR49 Registers/Commands          |                         |                      |                     |                          |                          |                 |                       |  |  |

|-------|------------------|-------|-------|--------|-------|--------------------------------------|-------------------------|----------------------|---------------------|--------------------------|--------------------------|-----------------|-----------------------|--|--|

| Page  | Add              | ress  | Bank  | Add    | ress  |                                      |                         |                      | В                   | it                       |                          |                 |                       |  |  |

| [dec] | [dec]            | [hex] | [dec] | [dec]  | [hex] | 7                                    | 6                       | 5                    | 4                   | 3                        | 2                        | 1               | 0                     |  |  |

|       | 6                | 06    |       | 6      | 06    |                                      |                         |                      |                     | CMA_<br>CCW_En           | CMA_<br>CW_En            | FeRAM_<br>Clear |                       |  |  |

|       | 08               | 08    |       | 08     | 08    |                                      |                         |                      |                     |                          | VWC_<br>Trigger          |                 | XC_<br>Comp_<br>Clear |  |  |

|       | 10               | 0A    |       | 10     | 0A    | MT_Test_<br>Mode                     |                         |                      |                     |                          |                          |                 |                       |  |  |

|       | 15               | 0F    |       | 15     | 0F    |                                      | MT Counter Command[7:0] |                      |                     |                          |                          |                 |                       |  |  |

|       | 43               | 2B    | 18    | 43     | 2B    | MT_<br>Protocol_<br>Error            | CMA_<br>Busy            | CMA_<br>CCW_<br>Done | CMA_<br>CW_<br>Done | MT_<br>Counter_<br>Error | MT_<br>Counter_<br>Alarm | CMA_<br>Error   | MT_<br>Sync_<br>Error |  |  |

|       | 48               | 30    |       | 48     | 30    |                                      |                         |                      | 1                   | MT[38:32]                | 1                        | 1               |                       |  |  |

|       | 49               | 31    |       | 49     | 31    |                                      |                         |                      | MT[3                |                          |                          |                 |                       |  |  |

|       | 50               | 32    |       | 50     | 32    |                                      |                         |                      | MT[2                | 3:16]                    |                          |                 |                       |  |  |

| 9     | 51               | 33    |       | 51     | 33    |                                      |                         |                      | MT[                 | 15:8]                    |                          |                 |                       |  |  |

|       | 52               | 34    |       | 52     | 34    |                                      |                         |                      | MT[                 | 7:0]                     |                          |                 |                       |  |  |

|       | 62               | 3E    |       | 62     | 3E    |                                      |                         |                      | CMA_Of              | fset[15:8]               |                          |                 |                       |  |  |

|       | 63               | 3F    |       | 63     | 3F    |                                      |                         |                      | CMA_O               | ffset[7:0]               |                          |                 |                       |  |  |

|       | 66               | 42    |       | 2      | 02    |                                      |                         |                      |                     |                          |                          | MT_<br>MemErr   | MT_<br>MagLO          |  |  |

|       | 67               | 43    |       | 3      | 03    | VWC<br>Quality                       | XC_<br>Error            | CMA_<br>Timeout      | VWC_<br>Timeout     | Speed_<br>VWC            | Speed_<br>CMA            | Speed_<br>MT    | MT Error              |  |  |

|       | 68               | 44    | 19    | 4      | 04    | Alarm<br>Trigger                     |                         |                      | DUT<br>Ready        |                          |                          |                 |                       |  |  |

|       | 69               | 45    |       | 5      | 05    |                                      |                         | Reserved             | Reserved            | VWC<br>Result<br>Ready   | CMA<br>CCW<br>Ready      | CMA CW<br>Ready | MT<br>Ready           |  |  |

|       | 70               | 46    |       | 6      | 06    | EH Pulse VWC data; Average – 4 Sigma |                         |                      |                     |                          |                          |                 |                       |  |  |

|       | 71               | 47    |       | 7      | 07    |                                      |                         | EH                   | Pulse VW0           | C data – M               | ean                      |                 |                       |  |  |

## First FeRAM and Alarm Clear

- 1. Motor condition: Static.

- 2. Unlock Register Write.

- 3. Trigger MT counter soft reset.

- 4. Set default MT configuration.

- 5. FeRAM clear.

- a. Write Address 0x06 to Data 02h (FeRAM clear command, Bit 1 set to High).

- 6. Read back 39 bits of the FeRAM MT value.

- a. Read back 39 bits value from Page 9/Bank 18 Address 0x30 to 0x34,

- b. Confirm its value is 0 ± 1 revolution.

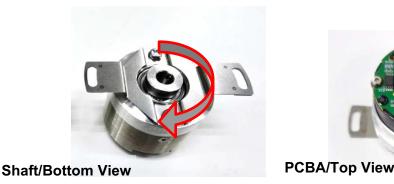

## Codewheel Zero to Magnet Zero Alignment (CMA) Calibration

- 1. Motor condition: Spin 100 rpm in the CW direction.

- 2. Unlock Register Write.

- 3. Trigger MT counter soft reset.

- 4. Set default MT configuration.

- 5. CMA clock wise calibration.

- a. Write Address 0x06 to Data 04h.

- b. Wait for at least 1.2 seconds (2 revolutions at the speed of 100 rpm).

- c. Read Address 0x2B. Expected data return 10h.

- 6. Motor condition: Spin 100 rpm in the CCW direction.

- 7. CMA counter clockwise calibration.

- a. Write Address 0x06 to Data 0Ch.

- b. Wait for at least 1.2 seconds (2 revolutions at the speed of 100 rpm).

- c. Read Address 0x2B. Expected data return 30h.

- 8. CMA completed. AR49 will automatically program the CMA value into the memory.

- 9. Power cycle and read back the AR49 CMA value and confirm it has been set.

- a. Read Address 0x3E and 0x3F. Expected data returned not equal to 00h.

Figure 16: CMA Calibration Direction Definition

Clockwise direction when looking toward the encoder shaft-end

Table 21: CMA Calibration Command and Related Registers

| Stan  | Standard SSI/SPI/<br>RS485 BiSS-0 |       |       |       |       | Key AR49 Registers/Commands |              |                      |                     |                          |                          |               |                       |  |

|-------|-----------------------------------|-------|-------|-------|-------|-----------------------------|--------------|----------------------|---------------------|--------------------------|--------------------------|---------------|-----------------------|--|

| Page  | Add                               | ress  |       | Bank  |       |                             | Bit          |                      |                     |                          |                          |               |                       |  |

| [dec] | [dec]                             | [hex] | [dec] | [dec] | [hex] | 7                           | 6            | 5                    | 4                   | 3                        | 2                        | 1             | 0                     |  |

|       | 6                                 | 06    | 18    | 6     | 06    |                             |              |                      |                     | CMA_<br>CCW_En           | CMA_<br>CW_En            |               |                       |  |

|       | 10                                | 0A    |       | 10    | 0A    | MT_ Test_<br>Mode           |              |                      |                     |                          |                          |               |                       |  |

| 9     | 43                                | 2B    |       | 43    | 2B    | MT_<br>Protocol_<br>Error   | CMA_<br>Busy | CMA_<br>CCW_<br>Done | CMA_<br>CW_<br>Done | MT_<br>Counter_<br>Error | MT_<br>Counter_<br>Alarm | CMA_<br>Error | MT_<br>Sync_<br>Error |  |

|       | 62                                | 3E    |       | 62    | 3E    | CMA_Offset [15:8]           |              |                      |                     |                          |                          |               |                       |  |

|       | 63                                | 3F    |       | 63    | 3F    | CMA_Offset [7:0]            |              |                      |                     |                          |                          |               |                       |  |

### **Second FeRAM Clear**

- 1. Motor condition: Move 1 revolution, and then stop at AR49 ST position ~90 degrees.

- 2. Unlock Register Write.

- 3. Trigger MT counter soft reset.

- 4. Set default MT configuration.

- 5. FeRAM clear.

- a. Write Address 0x06 to Data 02h (FeRAM clear command, Bit-1 set to High).

- 6. Read back 39 bits of FeRAM MT value.

- a. Read back 39 bits value from Page 9/Bank 18 Address 0x30 to 0x34.

- b. Confirm that its value is  $0 \pm 1$  revolution.

Table 22: EHMT Cross-Check Error Compensation and Related Registers

| Stan  | dard SS<br>RS485 | I/SPI/ |       | BiSS-C | :     |                             |              | Key A           | R49 Regis       | ters/Com            | mands              |               |                       |

|-------|------------------|--------|-------|--------|-------|-----------------------------|--------------|-----------------|-----------------|---------------------|--------------------|---------------|-----------------------|

| Page  | Add              | ress   | Bank  | Add    | Iress |                             |              |                 | В               | it                  |                    |               |                       |

| [dec] | [dec]            | [hex]  | [dec] | [dec]  | [hex] | 7                           | 7 6 5 4      |                 |                 | 3                   | 2                  | 1             | 0                     |

|       | 08               | 08     |       | 08     | 08    |                             |              |                 |                 |                     |                    |               | XC_<br>Comp_<br>Clear |

|       | 34               | 22     | 18    | 34     | 22    | Reserved Temp_ N            |              |                 |                 | Mem_<br>Err         | Config<br>Code Err | STErr         | MLS_<br>Err           |

|       | 35               | 23     |       | 35     | 23    | Reserved                    |              |                 |                 |                     |                    | Lis_Err       | LED_<br>Err           |

|       | 64               | 40     |       | 0      | 00    |                             |              | EHMT_X          | C_ERR_C         | ompensat            | tion [15:8]        |               |                       |

| 9     | 65               | 41     |       | 1      | 01    |                             |              | EHMT_           | XC_ERR_0        | Compensa            | tion [7:0]         |               |                       |

|       | 66               | 42     |       | 2      | 02    |                             |              | Rese            | erved           |                     |                    | MT_<br>MemErr | MT_<br>MagLO          |

|       | 67               | 43     | 19    | 3      | 03    | VWC<br>Quality              | XC_<br>Error | CMA_<br>Timeout | VWC_<br>Timeout | Speed_<br>VWC       | Speed_<br>CMA      | Speed_<br>MT  | MT Error              |

|       | 68               | 44     |       | 4      | 04    | Alarm Reserved DUT Ready Re |              |                 |                 |                     | Rese               | erved         |                       |

|       | 69               | 45     |       | 5      | 05    | Reserved VWC Result         |              |                 |                 | CMA<br>CCW<br>Ready | CMACW<br>Ready     | MT<br>Ready   |                       |

## **Alarm and Compensation Register Clear**

- 1. Motor condition: Static.

- 2. Unlock Register Write.

- 3. Execute XC ERR compensation clear command as follows:

- a. Write Address 0x08 to Data 01h (XC compensation clear command)

- 4. Alarm clear.

- a. Write Address 0x02 to Data 04h (alarm clear command).

- b. Delay 100 ms.

- 5. Read back AR49 XC\_ERR compensation value and confirm it has been cleared.

- a. Read Address 0x40 and 0x 41. Expected data return 00h.

- 6. Read Back AR49 and MT counter alarm status.

- a. Read Address 0x42 and 0x43. Expected data return 0000h.

- b. Read Address 0x44 and 0x45. Expected data return 1001h.

- c. Read Address 0x22 and 0x23. Expected data return 0000.

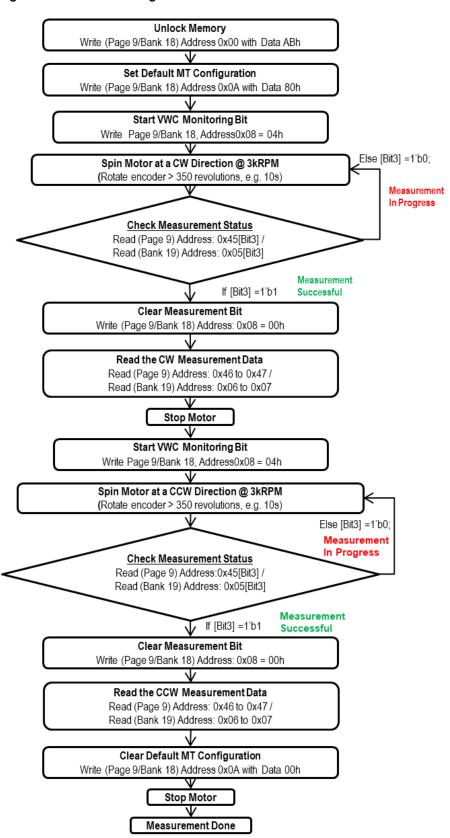

## **EH Pulse Voltage Monitoring**

The AR49 has a built-in function to measure and monitor the EH pulse voltage level (VWC). Measurement must be conducted with the final encoder assembly inclusive of the external shield cover.

- 1. Unlock Register Write.

- 2. Set the default MT configuration.

- 3. Enable VWC monitoring self-check by writing Page 9/Bank 18 Address 0x08 = 04h.

- 4. Spin the spindle motor in the clockwise (CW) direction for >350 rotations at 3000 rpm.

- 5. Loop reading calibration status Page 9, Address 0x45 (BiSS-C Bank19, Address 0x05).

- a. If Bit[3] = 1b, the measurement is done.

- 6. End VWC monitoring self-check by writing Page 9/Bank 18, Address 0x08 = 00h.

- 7. Read Page 9, Address 0x46 to 0x47 (BiSS-C Bank19, Address 0x06 and 0x07) for the measured data.

- 8. Stop the motor. Repeat Steps 2 to 6 in the counter-clockwise (CCW) direction.

- 9. Clear the default MT configuration.

**Table 23: EH Pulse Monitoring Measurement Registers**

| S     | PI/RS48 | 5     |       | BiSS-C |       | Description       |                        |                                                                           |   | В            | Bit                    |                      |   |             |

|-------|---------|-------|-------|--------|-------|-------------------|------------------------|---------------------------------------------------------------------------|---|--------------|------------------------|----------------------|---|-------------|