## **Data Sheet**

## AFBR-57H5MZ

# 64GFC SFP56 for Multi-Mode Optical Fiber Digital Diagnostic SFP, 850 nm, 64G/32G/16G

## **Description**

The Broadcom<sup>®</sup> AFBR-57H5MZ optical transceiver supports high-speed serial links over multi-mode optical fiber at signaling rates up to 57.8 Gb/s PAM4 (the serial line rate of 64GFC). The product is compliant with Small Form Pluggable SFP+ industry agreements for mechanical and low speed electrical specifications. High-speed electrical and optical specifications are compliant with ANSI Fibre Channel FC-PI-7.

The AFBR-57H5MZ is a multi-rate 850-nm transceiver that ensures compliance with FC-PI-7 64GFC, 32GFC, and 16GFC specifications. Per the requirements of 64GFC, internal clock and data recovery circuits (CDRs) are present on both electrical input and electrical output of this transceiver. These CDRs lock at 57.8-Gb/s PAM4, 28.05-Gb/s NRZ and 14.025-Gb/s NRZ (64GFC, 32GFC, and 16GFC) accomplished by using two Rate Select inputs and I<sup>2</sup>C to configure transmit and receive sides.

Digital diagnostic monitoring information (DMI) is present in the AFBR-57H5MZ per the requirements of SFF-8472, providing real time monitoring information of transceiver laser, receiver and environment conditions over an SFF-8431 I<sup>2</sup>C interface.

#### **Features**

- Compliant to RoHS directives with 7c-I exemption

- Broadcom high-performance 850-nm Vertical Cavity Surface Emitting Laser (VCSEL) and PiN diode

- Class 1 eye safe per IEC60825-1 and CDRH

- Wide temperature range (0°C to 75°C)

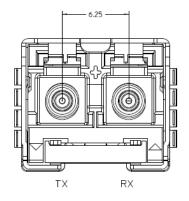

- LC duplex connector optical interface conforming to ANSI TIA/EIA604-10 (FOCIS 10A)

- Diagnostic features per SFF-8472, "Diagnostic Monitoring Interface for Optical Transceivers"

- Enhanced operational features including EWRAP,

OWRAP, and adaptive electrical EQ/emphasis settings

- Integrated PRBS generator and bit error rate checker

- Real time monitoring of the following:

- Transmitter average optical power

- Received average optical power

- Laser bias current

- Temperature

- Supply voltage

- Power-on hours

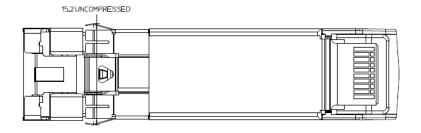

- SFP+ mechanical specifications per SFF-8432

- SFP+ compliant low-speed interface per SFF-8419

- Fibre Channel FC-PI-7 compliant high-speed optical and electrical interface

## **Applications**

- Fibre Channel switches

- Fibre Channel host bus adapters

- Fibre Channel RAID controllers

- Port-side connections

- Inter-switch or inter-chassis aggregated links

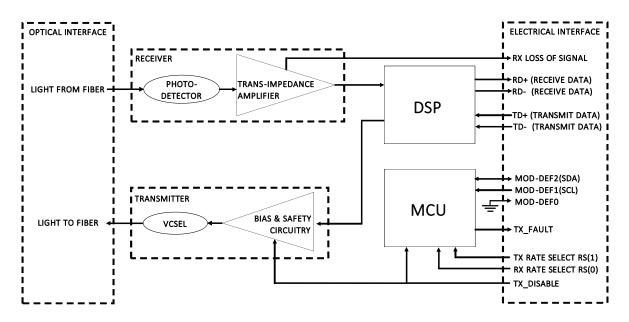

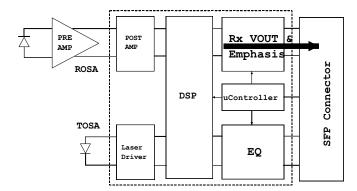

## **Transceiver Block Diagram**

Figure 1: Block Diagram

#### **Transmitter Section**

The transmitter section includes a transmitter optical sub-assembly (TOSA), a laser driver circuit, and a digital signal processor (DSP) with input variable equalization. The TOSA contains a Broadcom 850-nm Vertical Cavity Surface Emitting Laser (VCSEL) light source with an integral light monitoring function and imaging optics to ensure efficient optical coupling to the LC connector interface. The TOSA is driven by a laser driver circuit, which uses the differential output from the DSP to modulate and regulate VCSEL optical power. As mandated by FC-PI-7, the integral Tx DSP cleans up any incoming jitter accumulated from the host ASIC, PCB traces, and SFP electrical connector. Between the SFP electrical connector and Tx DSP is an adaptive equalization circuit to optimize SFP performance with nonideal incoming electrical waveforms at all rates.

#### **Receiver Section**

The receiver section includes a receiver optical sub-assembly (ROSA), a pre-amplification and post-amplification circuit, a DSP circuit with variable emphasis controls, and an integral PRBS generator. The ROSA, containing a high-speed PIN detector, pre-amplifier, and imaging optics efficiently couple light from the LC connector interface and perform an optical-to-electrical conversion. The resulting differential electrical signal passes through a post-amplification circuit and into the DSP for cleaning up accumulated jitter. The resulting signal is passed to a high-speed output line driver stage with variable, I<sup>2</sup>C controlled, emphasis settings that allow the host to optimize signal characteristics between the SFP and the host ASIC.

## **Digital Diagnostics**

The AFBR-57H5MZ is compliant to the Diagnostic Monitoring Interface (DMI) defined in document SFF-8472. These features allow the host to access, using I<sup>2</sup>C, real-time diagnostic monitors of transmit optical power, received optical power, temperature, supply voltage, and laser operating current.

## **Low-Speed Interfaces**

Conventional low-speed interface I/Os are available as defined in SFF-8431 to manage coarse and fine functions of the optical transceiver. On the transmit side, a Tx\_DISABLE input is provided for the host to turn on and off the outgoing optical signal. A transmitter rate select control input pin, Tx\_RATE, and I<sup>2</sup>C controls are provided to configure the transmitter stages for 64GFC, 32GFC, or 16GFC operation (logic HIGH reserved for 64GFC and 32GFC, logic LOW reserved for 16GFC). A transmitter fault indicator output, Tx\_FAULT, is available for the SFP to signal the host of a transmitter operational problem. A receiver rate select control input, Rx\_RATE, configures receiver stages for 64GFC, 32GFC, or 16GFC operation (logic HIGH reserved for 64GFC and 32GFC, logic LOW reserved for 16GFC). In 64G mode, the Rate\_Sel pins are ignored. A received optical power loss of signal indicator, RX\_LOS, is available to advise the host of a receiver operational problem.

## **Special Operation Functions**

See Table 29 for the I<sup>2</sup>C control registers.

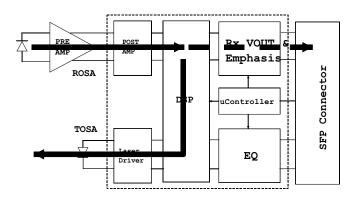

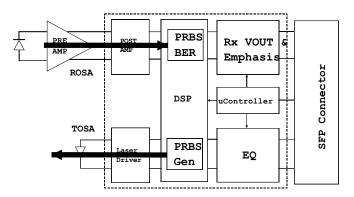

Figure 2: OWRAP Functionality (I<sup>2</sup>C Controlled)

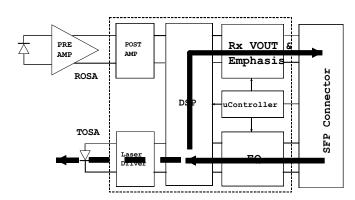

Figure 3: EWRAP Functionality (I<sup>2</sup>C Controlled)

Electrical and optical high-speed data "wrap" functions are enabled to assist with local host or remote diagnostic and optimization sequences. Optical data wrap (OWRAP) takes a received optical signal through a CDR and retransmits it optically out. Electrical data wrap (EWRAP) takes an incoming electrical signal through a CDR and retransmits it electrically out. In OWRAP/EWRAP mode the traffic pass-through can be turned on or off, controlled through I<sup>2</sup>C commands.

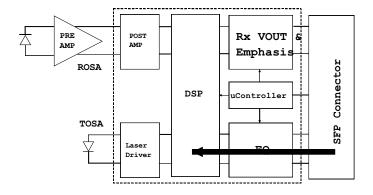

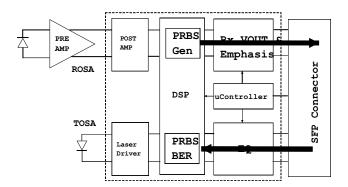

Figure 4: SFP Tx Input Electrical EQ Is Always Adaptive (No I<sup>2</sup>C Control Needed)

Figure 5: SFP Rx Variable Output Electrical Emphasis (I<sup>2</sup>C Controlled)

The electrical SFP input stage (TD +/–) has been enhanced with adaptive EQ, which optimizes the transceiver's input equalization settings without host control. The SFP electrical output stage (RD+/–) has been enhanced with variable output emphasis features to allow host control and optimization of the receiver's output settings. The host can then select, in situ, the most appropriate SFP setting for a given interconnect scenario.

Figure 6: Programmable PRBS Pattern Generator and Bit Error Rate Checker, Line Side (I<sup>2</sup>C Controlled)

Figure 7: Programmable PRBS Pattern Generator and Bit Error Rate Checker, System Side (I<sup>2</sup>C Controlled)

The SFP is equipped with an integrated PRBS generator that self-generates programmable PRBS patterns to either system side (TP4) or line side (TP1) at the speed (16G, 32G, or 64G) and operating mode (NRZ or PAM4) to which the SFP is set. The integrated bit error rate checker can also be enabled to measure bit error ratio for every 5 seconds (fixed). It enables users to know the optical link BER performance between TP2 and TP3 of the two separate SFPs or between the host ASIC transmitter (TP0) and the SFP Tx input (TP1).

**Table 1: Regulatory Compliance**

| Feature                                                                                                | Test Method                                                                                                                                                                                                                         | Performance                                                                                                                                                         |

|--------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Electrostatic Discharge (ESD) to the Electrical Contacts                                               | JEDEC Human Body Model (HBM)<br>(JESD22-A114-B)                                                                                                                                                                                     | High-speed contacts withstand 1000V. All other contacts withstand 2000 V.                                                                                           |

| ESD to the Optical Connector<br>Receptacle                                                             | EN61000-4-2, Criterion B                                                                                                                                                                                                            | When installed in a properly grounded housing and chassis, the units are subjected to 15-kV air discharges during operation and 8-kV direct discharges to the case. |

| Electromagnetic Interference (EMI)                                                                     | FCC Part 15 CENELEC EN55022<br>(CISPR 22A) VCCI Class 1                                                                                                                                                                             | System margins are dependent on customer board and chassis design.                                                                                                  |

| Immunity                                                                                               | EN 55024:2010                                                                                                                                                                                                                       | Typically shows no measurable effect from a 3 V/m field step from 80 MHz to 1 GHz applied to the module without a chassis enclosure                                 |

| Laser Eye Safety and Equipment Type Testing  BAUART GEPRUFT TUV Rheinland Product Safety TYPE APPROVED | CLASS 1 LASER PRODUCT Complies with 21 CFR 1040.10 except for conformance with IEC 60825-1 Ed.3., as described in Laser Notice No. 56, dated May 8, 2019  (IEC) EN62368-1: 2014  (IEC) EN60825-1: 2014  (IEC) EN60825-2: 2004+A1+A2 | CDRH Certification 9720151-204                                                                                                                                      |

| Component Recognition                                                                                  | Underwriters Laboratories (UL) and Canadian Standards Association (CSA) Joint Component Recognition for Information Technology Equipment including Electrical Business Equipment                                                    | UL File: E484615                                                                                                                                                    |

| RoHS                                                                                                   | _                                                                                                                                                                                                                                   | RoHS compliant with 7c-I exemptions.                                                                                                                                |

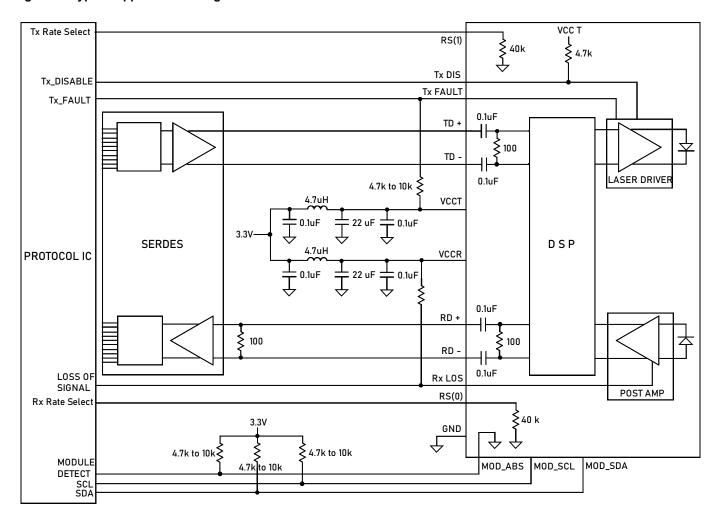

Figure 8: Typical Application Configuration

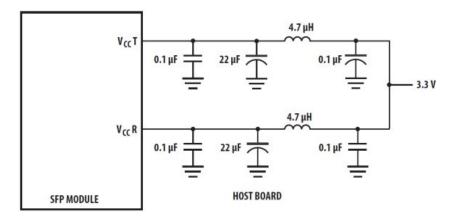

Figure 9: Recommended Power Supply Filter

**NOTE:** Inductors must have less than  $0.5\Omega$  series resistance to limit the voltage drop to the SFP module.

AFBR-57H5MZ-DS102 Broadcom

#### Table 2: Pin Description

| Pin | Name                  | Function/Description                                                 | Notes |

|-----|-----------------------|----------------------------------------------------------------------|-------|

| 1   | VeeT                  | Transmitter Ground                                                   | _     |

| 2   | TX_FAULT              | Transmitter Fault Indication - High indicates a fault condition      | а     |

| 3   | TX_DISABLE            | Transmitter Disable - Module optical output disables on high or open | b     |

| 4   | MOD_SDA               | Module Definition 2 - Two wire serial ID interface data line (SDA)   | С     |

| 5   | MOD_SCL               | Module Definition 1 - Two wire serial ID interface clock line (SCL)  | С     |

| 6   | MOD_ABS               | Module Definition 0 - Grounded in module (module present indicator)  | С     |

| 7   | Rx Rate Select, RS(0) | Receiver Rate Select                                                 | d     |

| 8   | RX_LOS                | Loss of Signal - High indicates loss of received optical signal      | е     |

| 9   | Tx Rate Select, RS(1) | Transmitter Rate Select                                              | d     |

| 10  | VeeR                  | Receiver Ground                                                      | _     |

| 11  | VeeR                  | Receiver Ground                                                      | _     |

| 12  | RD-                   | Inverse Received Data Out                                            | f     |

| 13  | RD+                   | Received Data Out                                                    | f     |

| 14  | VeeR                  | Receiver Ground                                                      | _     |

| 15  | VccR                  | Receiver Power + 3.3 V                                               | g     |

| 16  | VccT                  | Transmitter Power + 3.3 V                                            | g     |

| 17  | VeeT                  | Transmitter Ground                                                   | _     |

| 18  | TD+                   | Transmitter Data In                                                  | h     |

| 19  | TD-                   | Inverse Transmitter Data In                                          | h     |

| 20  | VeeT                  | Transmitter Ground                                                   |       |

- a.  $TX_FAULT$  is an open collector/drain output, which must be pulled up with a  $4.7 \text{ k}\Omega$  to  $10 \text{ k}\Omega$  resistor on the host board. When high, this output indicates a laser fault of some kind. Low indicates normal operation. In the low state, the output is pulled to < 0.4V.

- b. TX\_DISABLE is an input that shuts down the transmitter optical output. It is internally pulled up (within the transceiver) with a 4.7-kΩ resistor.

Low (-0.3V to 0.8V): Transmitter on

Between (0.8V and 2.0V): Undefined

High (2.0V to Vcc + 0.3) or OPEN: Transmitter Disabled

- c. The signals Mod\_ABS, SCL, SDA designate the two-wire serial interface pins. They must be pulled up with a 4.7 kΩ to 10 kΩ resistor on the host board. Mod\_ABS is grounded by the module to indicate the module is present. Mod\_SCL is serial clock line (SCL) of two-wire seiral interface. Mod\_SDA is serial data line (SDA) o two wire serial interface.

- d. The rate select input pin selects the signal rates along with the software rate select bits as shown in Table 16 and Table 17. It is internally pulled down with a 40-kΩ resistor.

- e. RX\_LOS (Rx Loss of Signal) is an open collector/drain output that must be pulled up with a 4.7-kΩ to 10- kΩ resistor on the host board. When high, this output indicates the received optical power is below the worst case receiver sensitivity (as defined by the standard in use). Low indicates normal operation. In the low state, the output will be pulled to < 0.4V.

- f. RD-/+ designate the differential receiver outputs. They are AC coupled 100  $\Omega$  differential lines that should be terminated with 100 $\Omega$  differential at the host SerDes input. AC coupling is done inside the transceiver and is not required on the host board.

- g. VccR and VccT are the receiver and transmitter power supplies. Refer to SFF-8419 for details.

- h. TD-/+ designate the differential transmitter inputs. They are AC coupled differential lines with 100Ω differential termination inside the module. The AC coupling is done inside the module and is not required on the host board.

Stress in excess of any of the individual absolute maximum ratings can cause immediate catastrophic damage to the module even if all other parameters are within Recommended Operating Conditions. It should not be assumed that limiting values of more than one parameter can be applied to the module concurrently. Exposure to any of the absolute maximum ratings for extended periods can adversely affect reliability.

**Table 3: Absolute Maximum Ratings**

| Parameter                | Symbol | Min. | Max.            | Units | Reference |

|--------------------------|--------|------|-----------------|-------|-----------|

| Storage Temperature      | Ts     | -40  | 85              | °C    | а         |

| Relative Humidity        | RH     | 5    | 95              | %     | _         |

| Supply Voltage           | Vcc    | -0.3 | 3.63            | V     | _         |

| Low Speed Input Voltage  | Vi     | -0.3 | Vcc + 0.5, 3.63 | V     | _         |

| Low Speed Output Current | _      | -20  | 20              | mA    | _         |

a. Absolute maximum ratings are those values beyond which damage to the device may occur if these limits are exceeded for other than a short period of time. Refer to the reliability data sheet for specific reliability performance. Between the absolute maximum ratings and the Recommended Operating Conditions, functional performance is not intended, device reliability is not implied, and damage to the device may occur over an extended period of time.

Recommended Operating Conditions specify parameters for which the optical and electrical characteristics hold unless otherwise noted. Optical and electrical characteristics are not defined for operation outside the recommended operating conditions, reliability is not implied, and damage to the module may occur for such operation over an extended period of time.

**Table 4: Recommended Operating Conditions**

| Parameter                                     | Symbol | Min.   | Тур. | Max.  | Units | Reference |

|-----------------------------------------------|--------|--------|------|-------|-------|-----------|

| Case Operating Temperature                    | Тс     | 0      | _    | 75    | °C    | а         |

| Supply Voltage                                | Vcc    | 3.135  | 3.3  | 3.465 | V     | _         |

| Data Rate                                     | _      | 14.025 | _    | 28.9  | GBd   | b         |

|                                               |        | 14.025 | _    | 57.8  | Gb/s  |           |

| Two-Wire Serial (TWS) Interface<br>Clock Rate | _      | _      | _    | 400   | kHz   | С         |

- a. The position of case temperature measurement is shown in Figure 13. Continuous operation at the maximum recommended operating case temperature should be avoided to not degrade reliability.

- 64GFC PAM4 requires FEC RS(544,514) encoding per FC-PI-7. 32GFC NRZ requires FEC RS(528,514) per FC-PI-6 and 16GFC NRZ does not require FEC per FC-PI-5.

- c. With 500-µs maximum clock stretch per SFF-8419.

**Table 5: Transceiver Electrical Characteristics**

| Parameter                                                | Symbol | Min. | Тур. | Max.  | Units | Reference      |

|----------------------------------------------------------|--------|------|------|-------|-------|----------------|

| Transceiver Power Consumption                            | _      | _    | 1.4  | 1.65  | W     | At 3.3V max.   |

|                                                          |        |      |      | 2.0   | W     | At 3.465V max. |

| Power Supply Noise Rejection (peak-peak)                 | PSNR   | _    | _    | 66    | mV    | а              |

| Low Speed Outputs: TX_FAULT, RX_LOS, MOD_SDA             | VOL    | -0.3 | _    | 0.4   | V     | b              |

|                                                          | IOH    | -50  |      | 37.5  | μA    | _              |

| Low Speed Inputs: TX_DIS, MOD_SCL, MOD_SDA, RS(0), RS(1) | VIL    | -0.3 | _    | 0.8   | V     | С              |

|                                                          | VIH    | 2.0  | _    | VccT+ | V     | С              |

|                                                          |        |      |      | 0.3   |       |                |

- a. Filter per the SFP specification is required on the host board to remove 10-Hz to 2-MHz content.

- b. Pulled up externally with a 4.7-k $\Omega$  to 10-k $\Omega$  resistor on the host board to 3.3V.

- c. Mod\_SCL and Mod\_SDA must be pulled up externally with a4.7-k $\Omega$  to 10-k $\Omega$  resistor on the host board to 3.3V.

The following high speed electrical module input characteristics are defined over the Recommended Operating Conditions unless otherwise noted.

Table 6: High Speed Electrical Module Input Characteristics<sup>a</sup>

| Parameter                                         | Test Point | Min. | Тур.           | Max. | Units | Notes/Conditions                                  |

|---------------------------------------------------|------------|------|----------------|------|-------|---------------------------------------------------|

| 64GFC Signaling Rate, Per Lane                    | B'         | _    | 28.9           | _    | GBd   | ± 100 ppm, PAM4 and<br>RS(544,514) FEC<br>encoded |

| 32GFC Signaling Rate, Per Lane                    | B'         | _    | 28.05          | _    | GBd   | ± 100 ppm, NRZ and<br>RS(528, 514) FEC<br>encoded |

| 16GFC Signaling Rate, Per Lane                    | B'         | _    | 14.025         | _    | GBd   | ± 100 ppm, NRZ                                    |

| Differential pk-pk Input Voltage<br>Tolerance     | B'         | 900  | _              | _    | mV    | _                                                 |

| Differential Termination Resistance<br>Mismatch   | В'         | _    | _              | 10   | %     | _                                                 |

| Differential Return Loss, SDD11 min.              | B'         | _    | Eq. 1, Fig. 9  | _    | dB    | IEEE 802.3 Annex 83E                              |

| Differential Mode to Common Mode Conversion, min. | B'         | _    | Eq. 2, Fig. 10 | _    | dB    | IEEE 802.3 Annex 83E                              |

| Common-Mode Output Voltage                        | B'         | _    | _              | _    | V     | b                                                 |

a. From FC-PI-7, Table 11.

**Table 7: Stressed Input Test Conditions**

| Parameter                                      | Value | Units | Notes/Conditions |

|------------------------------------------------|-------|-------|------------------|

| Module stressed input test                     |       |       | а                |

| Eye width at 10 <sup>-5</sup> probability EW5  | 0.23  | UI    | _                |

| Eye height at 10 <sup>-5</sup> probability EH5 | 34    | mV    | _                |

b. DC common mode voltage is generated by the host. The specification includes the effects of ground offset voltage.

Table 7: Stressed Input Test Conditions (Continued)

| Parameter                       | Value | Units | Notes/Conditions |

|---------------------------------|-------|-------|------------------|

| Vertical Eye Closure VEC (max.) | 12    | dB    | _                |

a. Module stressed input tolerance is measured using the procedure defined in 83E.3.4.1.1.

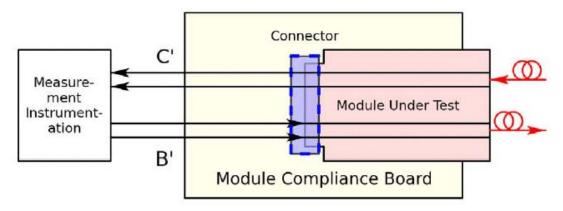

**Table 8: Reference Points**

| Test Point | Description                                                                                                                                       |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| B'         | Module electrical input at the input of the module compliance moard. Module return loss specifications are met at this point.                     |

| C,         | Module electrical output at the output of the module compliance board. Module output and module return loss specifications are met at this point. |

Figure 10: FC-PI-7 Module Compliance Points

Table 9: High Speed Electrical Module Output Characteristics<sup>a</sup>

| Parameter                                          | Test Point | Min.  | Тур.          | Max. | Units | Notes/Conditions      |

|----------------------------------------------------|------------|-------|---------------|------|-------|-----------------------|

| Differential Output Voltage (Enabled)              | C,         | _     | _             | 900  | mV    | Measured with PRBS13Q |

| Differential Output Voltage (Disabled)             | C'         | _     | _             | 35   | mV    | Measured with PRBS13Q |

| Common Mode Noise, RMS                             | C,         | _     | _             | 17.5 | mV    | _                     |

| Differential Termination Mismatch                  | C,         | _     | _             | 10   | %     | _                     |

| Differential Output Return Loss SDD22 (min.)       | C,         | _     | Eq. 1, Fig. 9 | _    | dB    | FC-PI-7               |

| Common to Differential Mode Conversion SDC22, min. | C,         | _     | Eq 2, Fig. 10 | _    | dB    | FC-PI-7               |

| Source Transition Time (20% to 80%)                | C,         | 9.5   | _             |      | ps    | _                     |

| Common Mode Voltage                                | C,         | _     | _             |      | V     | b                     |

| Eye width at 10 <sup>-5</sup> Probability EW5      | C,         | 0.265 | _             |      | UI    | _                     |

| Eye height at 10 <sup>-5</sup> Probability EH5     | C,         | 70    | _             |      | mV    | _                     |

| Vertical Eye Closure VEC                           | C,         | _     | _             | 12   | dB    | <del>_</del>          |

| Near-End Eye Symmetry Mask Width (ESMW)            | C'         | _     | 0.265         | -    | UI    | _                     |

| Near-end Eye Height, Differential                  | C,         | 70    | _             | _    | mV    | _                     |

| Far-end ESMW                                       | C,         | _     | 0.2           | _    | UI    | _                     |

| Far-end Eye Height, Differential                   | C,         | 30    | _             | _    | mV    | _                     |

| Far-end Pre-cursor ISI Ratio                       | C,         | -4.5  | _             | 2.5  | %     | _                     |

a. From FC-PI-7, Table 10.

b. DC common mode voltage is generated by the host. The specification includes the effects of ground offset voltage.

**Table 10: 64GFC Mode Optical Transmitter Characteristics**

| Parameter                                                | Test Point | Min.              | Тур.                              | Max. | Units | Notes/Conditions                               |

|----------------------------------------------------------|------------|-------------------|-----------------------------------|------|-------|------------------------------------------------|

| 64GFC Signaling Rate                                     | gamma-T    | _                 | 28.9                              | _    | GBd   | ± 100 ppm, PAM4 and<br>RS(544,514) FEC encoded |

| Center Wavelength Range                                  | gamma-T    | 840               | _                                 | 860  | nm    | _                                              |

| RMS Spectral Width                                       | gamma-T    | _                 | _                                 | 0.60 | nm    | _                                              |

| Transmitter and Dispersion Eye Closure for PAM4 (TDECQ), | gamma-T    | _                 | _                                 | 5.5  | dB    | _                                              |

| TDECQ- 10log <sub>10</sub> (C <sub>eq</sub> )            | gamma-T    | _                 | _                                 | 5.5  | dB    | _                                              |

| Optical Modulation Amplitude (OMA <sub>outer</sub> )     | gamma-T    | -4.5 <sup>a</sup> | _                                 | +3.0 | dBm   | _                                              |

| OMA <sub>outer</sub> Extinction Ratio                    | gamma-T    | 3                 | _                                 | _    | dB    | _                                              |

| Launch Power in OMAouter minus TDECQ                     | gamma-T    | -5.9              | _                                 | _    | dBm   | _                                              |

| Average Launch Power                                     | gamma-T    | -7.5              | _                                 | +4.0 | dBm   | _                                              |

| RIN <sub>12</sub> OMA                                    | gamma-T    | _                 | _                                 | -128 | dB/Hz | _                                              |

| Transmitter Transition Time, 20%-80%                     | gamma-T    | _                 | _                                 | 34   | ps    | _                                              |

| Average Launch Power of OFF transmitter,                 | gamma-T    | _                 | _                                 | -30  | dBm   | _                                              |

| Encircled Flux                                           | gamma-T    | _                 | ≥ 86% at 19 µm<br>≤ 30% at 4.5 µm | _    | _     | Type A1a.2 50-µm Fiber per IEC 61280-1-4       |

a. Even if the TDEC < 1.4 dB, the OMA (min.) must exceed this value.

The following characteristics are defined over the Recommended Operating Conditions unless otherwise noted.

Table 11: 64GFC Mode Optical Receiver Characteristics (per PC-PI-7)

| Parameter                                          | Test Point | Min. | Тур. | Max. | Units   | Notes/<br>Conditions |

|----------------------------------------------------|------------|------|------|------|---------|----------------------|

| Center Wavelength Range                            | gamma-R    | 840  | _    | 860  | nm      | _                    |

| Damage Threshold                                   | gamma-R    | +5.0 | _    | _    | dBm     | BER 1.09E-4          |

| Average Receive Power                              | gamma-R    | -9.4 | _    | +4.0 | dBm     | BER 1.09E-4          |

| Receive Power (OMA <sub>outer</sub> )              | gamma-R    |      | _    | +3.0 | dBm     | BER 1.09E-4          |

| Receiver Return Loss                               | gamma-R    | 12   | _    | _    | dB      | _                    |

| Receiver Sensitivity (OMA <sub>outer</sub> )       | gamma-R    |      | _    | -7.0 | dBm     | BER 1.09E-4          |

| Stressed Receiver Sensitivity OMA <sub>outer</sub> | gamma-R    |      | _    | -2.4 | dBm     | BER 1.09E-4          |

| Conditions of Stressed Receiver Sensitivity Test   | gamma-R    | _    | _    | _    | _       | _                    |

| Stressed Eye Closure for PAM4 (SECQ)               | gamma-R    |      | _    | 5.5  | dB      | BER 1.09E-4          |

| SECQ-10log <sub>10</sub> (C <sub>eq</sub> )        | gamma-R    |      | _    | 5.5  | dB      | BER 1.09E-4          |

| LOS Assert                                         | gamma-R    | -30  | _    | _    | dBm avg | _                    |

| LOS Deassert                                       | gamma-R    | _    | _    | -7   | dBm avg | _                    |

| LOS Hysteresis                                     | gamma-R    | 0.5  | _    | _    | dB      |                      |

Table 12: 32GFC Mode Optical Transmitter Characteristics<sup>a</sup>

| Parameter                                | Symbol | Min. | Тур.  | Max. | Units | Notes                                     |

|------------------------------------------|--------|------|-------|------|-------|-------------------------------------------|

| 32GFC Signaling Rate, Per Lane           | _      | 1    | 28.05 | _    | GBd   | ± 100 ppm NRZ, RS(528,514)<br>FEC encoded |

| Modulated Optical Output Power (OMA)     | Tx,OMA | 479  | _     | _    | μW    | _                                         |

| (Peak-to-Peak) 28.05 Gb/s                |        | -3.2 | _     | _    | dBm   | _                                         |

| Average Optical Output Power 28.05 Gb/s  | Pout   | -6.2 | _     | 2    | dBm   | b                                         |

| Vertical Eye Closure Penalty, 28.05 Gb/s | VECP   |      |       | 3.13 | dB    | _                                         |

a. Tc =  $0^{\circ}$ C to  $75^{\circ}$ C, VccT, VccR = 3.3V  $\pm 5\%$ .

**Table 13: 32GFC Mode Optical Receiver Characteristic**

| Parameter                                      | Symbol          | Min. | Тур. | Max.  | Units   | Notes |

|------------------------------------------------|-----------------|------|------|-------|---------|-------|

| Optical Input Power, 28.05 Gb/s                | P <sub>IN</sub> | _    |      | +2    | dBm,avg | _     |

| Input Optical Modulation Amplitude, 28.05 Gb/s | OMA             | _    | _    | 95    | μW      | a, b  |

| (Peak to Peak) (Unstressed Sensitivity)        |                 | _    | _    | -10.2 | dBm     |       |

| Stressed Receiver Sensitivity (OMA) 28.05 Gb/s | _               | _    | _    | 263   | μW      | b, c  |

|                                                |                 | _    | _    | -5.7  | dBm     |       |

a. Input Optical Modulation Amplitude (commonly known as sensitivity] requires a valid Fibre Channel encoded input.

The following characteristics are defined over the Recommended Operating Conditions unless otherwise noted.

**Table 14: 16GFC Mode Optical Transmitter Characteristics**

| Parameter                                           | Symbol | Min. | Тур.   | Max. | Units | Notes                    |

|-----------------------------------------------------|--------|------|--------|------|-------|--------------------------|

| 16GFC Signaling Rate, Per Lane                      | _      | _    | 14.025 | _    | GBd   | ± 100 ppm NRZ,<br>No FEC |

| Modulated Optical Output Power (OMA) (Peak to Peak) | Tx,OMA | 331  | _      | _    | μW    | _                        |

| 14.025 Gb/s                                         |        | -4.8 | _      | _    | dBm   | _                        |

| Average Optical Output Power                        | Pout   | -7.8 |        | _    | dBm   | а                        |

| Vertical Eye Closure Penalty, 14.025 Gb/s           | VECP   | _    |        | 2.56 | dB    | _                        |

| Transmitter Uncorrelated Jitter, 14.025 Gb/s        | UJ     |      |        | 0.03 | UI    | _                        |

a. Max Pout is the lesser of Class 1 safety limits (CDRH and EN 60825) or received power, max.

The following characteristics are defined over the Recommended Operating Conditions unless otherwise noted.

**Table 15: 16GFC Mode Optical Receiver Characteristics**

| Parameter                                       | Symbol          | Min. | Тур. | Max.  | Unit.   | Notes       |

|-------------------------------------------------|-----------------|------|------|-------|---------|-------------|

| Optical Input Power                             | P <sub>IN</sub> | _    |      | 0     | dBm,avg | per FC-PI-5 |

| Input Optical Modulation Amplitude, 14.025 Gb/s | OMA             | _    |      | 89    | μW      | а           |

| (Peak to Peak) (Unstressed Sensitivity)         |                 |      | _    | -10.5 | dBm     |             |

b. Max. Pout is the lesser of Class 1 safety limits (CDRH and EN 60825) or received power, max.

b. 32GFC (28.05 Gb/s) assumes an FEC encoded RS(528, 514) signal and allows a BER of 1E-6 for receiver and transmitter measurements.

c. 28.05 Gb/s stressed received vertical eye closure penalty (ISI) min. is 3.1 dB.

#### Table 15: 16GFC Mode Optical Receiver Characteristics (Continued)

| Parameter                                       | Symbol | Min. | Тур. | Max. | Unit. | Notes |

|-------------------------------------------------|--------|------|------|------|-------|-------|

| Stressed Receiver Sensitivity (OMA) 14.025 Gb/s | _      | _    | _    | 170  | μW    | b     |

|                                                 |        | _    | _    | -7.7 | dBm   |       |

- a. Input Optical Modulation Amplitude (commonly known as sensitivity) requires a valid Fibre Channel encoded input and allows a BER of 1E–12.

- b. 14.025-Gb/s stressed received vertical eye closure penalty (ISI) min is 2.5 dB for all fiber types.

## **Rate Select Control**

TX and RX rates and operating modes can be controlled by the hardware input pins and the register control bits as shown in Table 16 and Table 17. All five rate select control inputs must be set to 0 for 16GFC operation. Either A, B, C, or D must be set to 1 while A2.119.2 = 0 to switch to 32GFC operation. TX and RX operate at the same speed and operating mode and cannot be independently controlled.

Table 16: TX and RX Rate Select Control

|                                | Rate                           | TX and RX Rate and Operating Mode |                       |                       |       |                |

|--------------------------------|--------------------------------|-----------------------------------|-----------------------|-----------------------|-------|----------------|

| Software A2h<br>Byte 110 Bit 3 | Software A2h<br>Byte 118 Bit 3 | Software A2h<br>Byte 119 Bit 2    | Hardware Pin 7<br>RS0 | Hardware Pin 9<br>RS1 | Rate  | Operating Mode |

| 0                              | 0                              | 0                                 | 0                     | 0                     | 16GFC | TX RX CDR NRZ  |

| Α                              | В                              | 0                                 | С                     | D                     | 32GFC | TX RX CDR NRZ  |

| X                              | Х                              | 1                                 | X                     | Х                     | 64GFC | TX RX CDR PAM4 |

## 64GFC Rate Select Control/Status Register

The host can assert the 64GFC mode of operation by using I<sup>2</sup>C controls located in Address A2h Byte 119. When asserted, bit 2 of byte 119 enables the module 64GFC Mode of operation, ignoring the RS(0) and RS(1) hard pin and register settings. Byte 119 status bits 0–1 and 3–4 verify internal settings are properly configured for PAM operation at 28.9 GBd.

Table 17: EEPROM Serial ID Memory Contents - Soft Commands (Address A2h, Byte 119)

| Address<br>A2h Byte | Bit | Definition               | Status/Control | Behavior                                                                                                                                                                                                                                                             |

|---------------------|-----|--------------------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 119                 | 5–7 | Unallocated              | _              | _                                                                                                                                                                                                                                                                    |

| _                   | 4   | 64GFC Mode Tx Configured | Status         | This status bit is a response to the 64GFC mode control bit. The bit indicates the module Tx logic has finished configuring itself to 64GFC mode at 28.9 GBd.                                                                                                        |

| _                   | 3   | 64GFC Mode Rx Configured | Status         | This status bit is a response to the 64GFC mode control bit. The bit indicates the module Rx logic has finished configuring itself to 64GFC mode at 28.9 GBd.                                                                                                        |

| _                   | 2   | 64GFC Mode               | Control        | Writing a 1 to this bit selects 64GFC speed of operation at 28.9 GBd. When this bit is set to 1, the rate select settings on the pins or in the registers are ignored. Default at power up for this bit is 0.                                                        |

| _                   | 1   | Tx CDR Not Locked        | Status         | A value of 0 indicates that the CDR is locked, whereas a value of 1 indicates loss of lock of the CDR. In 64GFC mode, if bit 4 of this byte is set to 1, a value of 0 indicates that the equalizer has finished adaptation and the CDR is locked to the PAM4 signal. |

| _                   | 0   | Rx CDR Not Locked        | Status         | A value of 0 indicates that the CDR is locked, whereas a value of 1 indicates loss of lock of the CDR. In 64GFC mode, if bit 3 of this byte is set to 1, a value of 0 indicates that the equalizer has finished adaptation and the CDR is locked to the PAM4 signal. |

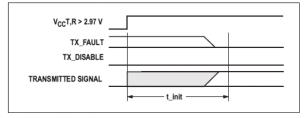

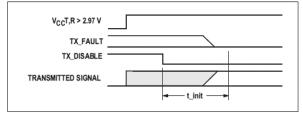

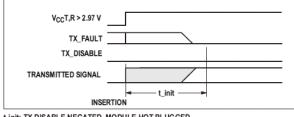

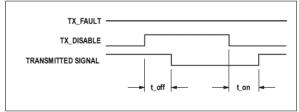

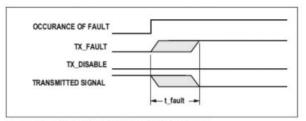

**Table 18: Transceiver Timing Characteristics**

| Parameter                                         | Symbol            | Min. | Max. | Unit. | Notes |

|---------------------------------------------------|-------------------|------|------|-------|-------|

| Hardware TX_DISABLE Assert Time (Gamma-t/TP2)     | t_off             | _    | 100  | μs    | а     |

| Hardware TX_DISABLE Negate Time (Gamma-t/TP2)     | t_on              | _    | 2    | ms    | b     |

| Time to initialize, including reset of TX_FAULT   | t_init            | _    | 10   | s     | С     |

| Hardware TX_FAULT Assert Time (Gamma-t/TP2)       | t_fault           | _    | 1    | ms    | d     |

| Hardware TX_DISABLE to Reset                      | t_reset           | 10   | _    | μs    | е     |

| Hardware RX_LOS Deassert Time (Gamma-r/TP3)       | t_loss_on         | _    | 100  | μs    | f     |

| Hardware RX_LOS Assert Time (Gamma-r/TP3)         | t_loss_off        | _    | 100  | μs    | g     |

| Hardware RATE_SELECT Assert Time RS(0), RS(1)     | t_rate_high       | _    | 4    | ms    | h     |

| Hardware RATE_SELECT Deassert Time RS(0), RS(1)   | t_rate_low        | _    | 4    | ms    | h     |

| Software TX_DISABLE Assert Time (Gamma-t/TP2)     | t_off_soft        | _    | 100  | ms    | i     |

| Software TX_DISABLE Negate Time (Gamma-t/TP2)     | t_on_soft         | _    | 100  | ms    | j     |

| Software Tx_FAULT Assert Time (Gamma-t/TP2)       | t_fault_soft      | _    | 100  | ms    | k     |

| Software Rx_LOS Assert Time (Gamma-r/TP3)         | t_loss_on_soft    | _    | 100  | ms    | I     |

| Software Rx_LOS Deassert Time (Gamma-r/TP3)       | t_loss_off_soft   | _    | 100  | ms    | m     |

| Software RATE_SELECT Assert Time RS(0), RS(1)     | t_rate_soft_high  | _    | 500  | ms    | n     |

| Software RATE_SELECT Deassert Time RS(0), RS(1)   | t_rate_soft_low   | _    | 500  | ms    | 0     |

| Software NRZ Tx_LOL Assert Time (Delta-t/TP1)     | tx_lol_on_nrz     | _    | 100  | ms    | р     |

| Software NRZ Tx_LOL Deassert Time (Delta-t/TP1)   | tx_lol_off_nrz    | _    | 100  | ms    | q     |

| Software PAM Tx_LOL Assert Time (Delta-t/TP1)     | tx_lol_on_pam     | _    | 100  | ms    | r     |

| Software PAM Tx_LOL DeAssert Time (Delta-t/TP1)   | tx_lol_off_pam    | _    | 100  | ms    | S     |

| Software NRZ Rx_LOL Assert Time (Gamma-r/TP3)     | rx_lol_on_nrz     | _    | 40   | ms    | t     |

| Software NRZ Rx_LOL Deassert Time (Gamma-r/TP3)   | rx_lol_off_nrz    | _    | 40   | ms    | u     |

| Software PAM Rx_LOL Assert Time (Gamma-r/TP3)     | rx_lol_on_pam     | _    | 40   | ms    | ٧     |

| Software PAM Rx_LOL Deassert Time (Gamma-r/TP3)   | rx_lol_off_pam    | _    | 40   | ms    | W     |

| Software 64GFC MODE Assert Time                   | t_rate_64gfc_high | _    | 2    | S     | Х     |

| Software 64GFC MODE Deassert Time                 | t_rate_64gfc_low  | _    | 2    | S     | у     |

| Diagnostic Data Ready                             | t_data            | _    | 5    | S     | Z     |

| Serial Bus Hardware Ready                         | t_serial          | _    | 300  | ms    | aa    |

| Serial Bus Buffer Time                            | t_buf             | 20   | _    | μs    | ab    |

| Write Cycle Time                                  | t_write           | _    | 80   | ms    | ac    |

| Serial Interface Clock Holdoff "Clock Stretching" | T_clock_hold      | _    | 500  | μs    | ad    |

| Serial ID Clock Rate                              | f_serial_clock    | _    | 400  | kHz   | ae    |

- a. Time from rising edge of TX\_DISABLE to when the optical output falls below 10% of nominal.

- b. Time from falling edge of TX\_DISABLE to when the modulated optical output rises above 90% of nominal.

- c. Time from power on or falling edge of Tx\_Disable to when the modulated optical output rises above 90% of nominal.

- d. From occurrence of fault to assertion of Tx\_Fault.

- e. Time TX\_DISABLE must be held high to reset the laser fault shutdown circuitry.

- f. Time from loss of optical signal to Rx LOS Assertion.

- g. Time from valid optical signal to Rx\_LOS Deassertion.

- h. Time from rising or falling edge of Rate\_Select input until transceiver is successfully passing traffic as designated by RS(0) and RS(1). For Rate\_Select going high, the internal CDR locks on valid 32GFC encoded data within the specified time. For Rate\_Select going low, the internal CDR locks on valid 16GFC encoded data within the specified time.

- i. Time from I<sup>2</sup>C interface assertion of TX\_DISABLE (A2h, byte 110, bit 6) to when the optical output falls below 10% of nominal. Measured from falling clock edge after stop bit of write transaction.

- j. Time from I<sup>2</sup>C interface deassertion of TX DISABLE (A2h, byte 110, bit 6) to when the optical output rises above 90% of nominal.

- k. Time from fault to I<sup>2</sup>C interface TX FAULT (A2h, byte 110, bit 2) asserted.

- I. Time for I<sup>2</sup>C interface assertion of Rx LOS (A2h, byte 110, bit 1) from loss of optical signal.

- m. Time for I<sup>2</sup>C interface deassertion of Rx LOS (A2h, byte 110, bit 1) from presence of valid optical signal.

- n. Time from I<sup>2</sup>C interface Assertion of Rate\_Select (either RS(0) in A2h, byte 110, bit 3 or RS(1) in A2h, byte 118, bit 3) to when the respective CDR is engaged at 32GCFC data rate.

- o. Time from I<sup>2</sup>C interface Deassertion of Rate\_Select (either RS(0) in A2h, byte 110, bit 3 or RS(1) in A2h, byte 118, bit 3) to when the respective CDR is either engaged at 16GCFC data rate or bypassed for 8GFC operation.

- p. Time from loss of TX electrical input CDR data lock to Tx LOL Assertion for data at 16GFC or 32GFC. Address A2h, Byte 119, bit 1.

- q. Time from valid TX electrical input CDR data lock to Tx LOL Deassertion for data at 16GFC or 32GFC. Address A2h, Byte 119, bit 1.

- r. Time from loss of TX electrical input CDR data lock to Tx\_LOL Assertion for data at 64GFC. Address A2h, Byte 119, bit 1.

- s. Time from valid TX electrical input CDR data lock to Tx LOL Deassertion for data at 64GFC. Address A2h, Byte 119, bit 1.

- t. Time from loss of RX optical input CDR data lock to Rx\_LOL Assertion for data at 16GFC or 32GFC. Address A2h, Byte 119, bit 0.

- u. Time from valid RX optical input CDR data lock to Rx LOL Deassertion for data at 16GFC or 32GFC. Address A2h, Byte 119, bit 0.

- v. Time from loss of RX optical input CDR data lock to Rx LOL Assertion for data at 64GFC. Address A2h, Byte 119, bit 0.

- w. Time from valid RX optical input CDR data lock to Rx LOL Deassertion for data at 64GFC. Address A2h, Byte 119, bit 0.

- x. Time from I<sup>2</sup>C interface Assertion of 64GFC MODE input until transceiver has finished configuring itself to 64GFC mode. See address A2h, Byte 119, bits 3 and 4 for the status indicators.

- y. Time from I<sup>2</sup>C interface Deassertion of 64G MODE input until transceiver has finished configuring itself out of 64GFC mode. See address A2h, Byte 119, bits 3 and 4 for the status indicators.

- z. From power on to data ready bit asserted (address A2h, byte 110, bit 0). Data ready indicates analog monitoring circuitry is functional.

- aa. Time from power on until module is ready for data transmission over the serial bus (reads or writes over A0h and A2h).

- ab. Time between START and STOP commands.

- ac. Time from stop bit to completion of a write command. Write cycle time is 40 ms for 1-4 bytes and 80 ms for 5-8 bytes.

- ad. Maximum time the SFP+ module may hold the SCL line low before continuing with a read or write operation.

- ae. With a maximum clock stretch of 500 µs. A maximum of 100-kHz operation can be supported without a clock stretch.

Table 19: Transceiver Digital Diagnostic Monitor (Real Time Sense) Characteristics<sup>a</sup>

| Parameter                                         | Symbol           | Min.  | Units | Notes                                                                                                                                                        |

|---------------------------------------------------|------------------|-------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Transceiver Internal Temperature Accuracy         | T <sub>INT</sub> | ± 5.0 | °C    | Temperature is measured internal to the transceiver. Valid from 0°C to 75°C case temperature.                                                                |

| Transceiver Internal Supply Voltage<br>Accuracy   | V <sub>INT</sub> | ± 0.1 | V     | Supply voltage is measured internal to the transceiver and can, with less accuracy, be correlated to voltage at the SFP Vcc pin. Valid over $3.3V \pm 5\%$ . |

| Transmitter Laser DC Bias Current Accuracy        | I <sub>INT</sub> | ± 10  | %     | I <sub>INT</sub> is better than ± 10% of the nominal value.                                                                                                  |

| Transmitted Average Optical Output Power Accuracy | P <sub>T</sub>   | ± 3.0 | dB    | Coupled into 50- $\mu$ m multi-mode fiber. Valid from 100 $\mu$ W to 500 $\mu$ W, average.                                                                   |

| Received Optical Input Power Accuracy             | $P_{R}$          | ± 3.0 | dB    | Coupled from 50-μm multi-mode fiber. Valid from 70 μW to 500 μW average.                                                                                     |

a.  $T_C = 0$ °C to 75°C, VccT, VccR = 3.3V ± 5%.

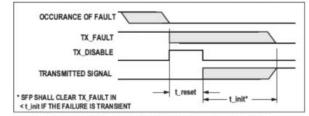

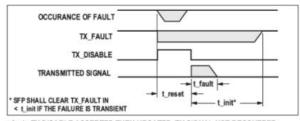

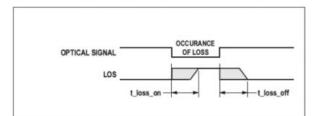

Figure 11: Transceiver Timing Diagrams (Module Installed Except Where Noted)

t-init: TX DISABLE NEGATED

t-init: TX DISABLE NEGATED, MODULE HOT PLUGGED

t-off & t-on: TX DISABLE ASSERTED THEN NEGATED

t-fault: TX FAULT ASSERTED, TX SIGNAL NOT RECOVERED

t-reset: TX DISABLE ASSERTED THEN NEGATED, TX SIGNAL RECOVERED

t-fault: TX DISABLE ASSERTED THEN NEGATED, TX SIGNAL NOT RECOVERED

t-loss-on & t-loss-off

AFBR-57H5MZ-DS102 Broadcom

Table 20: EEPROM Serial ID Memory Contents - Base SFP Memory (Address A0h)

| Byte<br>Number<br>Decimal | Data<br>Hex | Notes                                               | Byte<br>Number<br>Decimal | Data<br>Hex | Notes                                                      |

|---------------------------|-------------|-----------------------------------------------------|---------------------------|-------------|------------------------------------------------------------|

| 0                         | 03          | SFP physical device                                 | 37                        | 00          | Hex Byte of Vendor OUI <sup>a</sup>                        |

| 1                         | 04          | SFP function defined by serial ID only              | 38                        | 17          | Hex Byte of Vendor OUI <sup>a</sup>                        |

| 2                         | 07          | LC optical connector                                | 39                        | 6A          | Hex Byte of Vendor OUI <sup>a</sup>                        |

| 3                         | 00          | _                                                   | 40                        | 41          | "A" – Vendor Part Number ASCII character                   |

| 4                         | 00          | _                                                   | 41                        | 46          | "F" – Vendor Part Number ASCII character                   |

| 5                         | 00          | _                                                   | 42                        | 42          | "B" – Vendor Part Number ASCII character                   |

| 6                         | 00          | _                                                   | 43                        | 52          | "R" – Vendor Part Number ASCII character                   |

| 7                         | 60          | Short and Intermediate distance (per FC-PI)         | 44                        | 2D          | "-" – Vendor Part Number ASCII character                   |

| 8                         | 40          | Shortwave laser without OFC (open fiber control)    | 45                        | 35          | "5" – Vendor Part Number ASCII character                   |

| 9                         | 04          | Multi-mode 50-µm optical media                      | 46                        | 37          | "7" – Vendor Part Number ASCII character                   |

| 10                        | 2A          | 32/16G. Refer to Byte 36 for Extended Specification | 47                        | 48          | "H" – Vendor Part Number ASCII character                   |

| 11                        | 08          | PAM4 per SFF-8024, Table 4-2                        | 48                        | 35          | "5" – Vendor Part Number ASCII character                   |

| 12                        | FF          | Bit rate is greater than 25Gb/s. See address 66/67. | 49                        | 4D          | "M" – Vendor Part Number ASCII character                   |

| 13                        | 10          | 64/32/16G Independent Tx and Rx Rate Selects        | 50                        | 5A          | "Z" – Vendor Part Number ASCII character                   |

| 14                        | 00          | _                                                   | 51                        | 30          | " " – Vendor Part Number ASCII character                   |

| 15                        | 00          | _                                                   | 52                        | 31          | " " – Vendor Part Number ASCII character                   |

| 16                        | 00          | Unspecified 50/125 µm OM2 at 64GFC                  | 53                        | 20          | " " – Vendor Part Number ASCII character                   |

| 17                        | 00          | Unspecified 62.5/125 µm OM1 at 64GFC                | 54                        | 20          | " " - Vendor Part Number ASCII character                   |

| 18                        | 0A          | 100m of 50/125 μm OM4 at 64GFC                      | 55                        | 20          | " " - Vendor Part Number ASCII character                   |

| 19                        | 07          | 70m of 50/125 µm OM3 at 64GFC                       | 56                        | 20          | " " – Vendor Revision ASCII character                      |

| 20                        | 41          | "A" – Vendor Name ASCII character                   | 57                        | 20          | " " – Vendor Revision ASCII character                      |

| 21                        | 56          | "V" - Vendor Name ASCII character                   | 58                        | 20          | " " – Vendor Revision ASCII character                      |

| 22                        | 41          | "A" – Vendor Name ASCII character                   | 59                        | 20          | " " – Vendor Revision ASCII character                      |

| 23                        | 47          | "G" – Vendor Name ASCII character                   | 60                        | 03          | Hex Byte of Laser Wavelength <sup>b</sup>                  |

| 24                        | 4F          | "O" – Vendor Name ASCII character                   | 61                        | 52          | Hex Byte of Laser Wavelength <sup>b</sup>                  |

| 25                        | 20          | " " – Vendor Name ASCII character                   | 62                        | 00          | Unallocated                                                |

| 26                        | 20          | " " - Vendor Name ASCII character                   | 63                        | _           | Checksum for Bytes 0–62 <sup>c</sup>                       |

| 27                        | 20          | " " – Vendor Name ASCII character                   | 64                        | 28          | CDRs present. 2.0W power class.                            |

| 28                        | 20          | " " – Vendor Name ASCII character                   | 65                        | 3A          | Hardware SFP TX_DISABLE, TX_FAULT, and RX_LOS, RATE_SELECT |

| 29                        | 20          | " " – Vendor Name ASCII character                   | 66                        | E7          | Upper bit rate. 57.8 Gb/s in units of 250 Mb/s             |

| 30                        | 20          | " " – Vendor Name ASCII character                   | 67                        | 00          | _                                                          |

| 31                        | 20          | " " – Vendor Name ASCII character                   | 68–83                     | _           | Vendor Serial Number ASCII characters <sup>d</sup>         |

| 32                        | 20          | " " – Vendor Name ASCII character                   | 84–91                     | _           | Vendor Date Code ASCII characters <sup>e</sup>             |

| 33                        | 20          | " " – Vendor Name ASCII character                   | 92                        | 68          | Digital Diagnostics, Internal Cal, Rx Pwr Avg              |

Table 20: EEPROM Serial ID Memory Contents - Base SFP Memory (Address A0h) (Continued)

| Byte<br>Number<br>Decimal | Data<br>Hex | Notes                                 | Byte<br>Number<br>Decimal | Data<br>Hex | Notes                                                       |

|---------------------------|-------------|---------------------------------------|---------------------------|-------------|-------------------------------------------------------------|

| 34                        | 20          | " " – Vendor Name ASCII character     | 93                        | FA          | A/W, Soft SFP TX_DISABLE, TX_FAULT, and RX_LOS, RATE_SELECT |

| 35                        | 20          | " " - Vendor Name ASCII character     | 94                        | 08          | SFF-8472 Compliance to revision 12                          |

| 36                        | 80          | 64GFC FC-PI-7 per SFF-8024, Table 4-4 | 95                        | _           | Checksum for Bytes 64–94 <sup>f</sup>                       |

|                           |             |                                       | 96–255                    | 00          | Reserved for Broadcom use <sup>f</sup>                      |

- a. The IEEE Organizationally Unique Identifier (OUI) assigned to Broadcom is 00-17-6A (3 bytes of hex).

- b. Laser wavelength is represented in 16 unsigned bits. The hex representation of 850 (nm) is 0352.

- c. Addresses 63 and 95 are checksums calculated (per SFF-8472 and SFF-8074) and stored prior to product shipment.

- d. Addresses 68-83 specify the AFBR-57H5MZ ASCII serial number and will vary on a per-unit basis.

- e. Addresses 84–91 specify the AFBR-57H5MZ ASCII date code and will vary on a per-date-code basis.

- f. Bytes 128-255 are undefined and filled with 00h.

Table 21: EEPROM Serial ID Memory Contents - Enhanced SFP Memory (Address A2h)

| Byte<br>Number<br>Decimal | Data<br>Hex | Notes                            | Values | Byte<br>Number<br>Decimal | Data<br>Hex | Notes                                       | Values    |

|---------------------------|-------------|----------------------------------|--------|---------------------------|-------------|---------------------------------------------|-----------|

| 0                         | 50          | Temp H Alarm MSB <sup>a</sup>    | 80°C   | 36                        | 62          | Rx Power H Warning MSB <sup>g</sup>         | 4 dBm     |

| 1                         | 0           | Temp H Alarm LSB <sup>a</sup>    |        | 37                        | 1E          | Rx Power H Warning LSB <sup>g</sup>         |           |

| 2                         | FB          | Temp L Alarm MSB <sup>a</sup>    | −5°C   | 38                        | 3           | Rx Power L Warning MSB <sup>g</sup>         | –10.5 dBm |

| 3                         | 0           | Temp L Alarm LSB <sup>a</sup>    |        | 39                        | 7B          | Rx Power L Warning LSB <sup>g</sup>         |           |

| 4                         | 4B          | Temp H Warning MSB <sup>a</sup>  | 75°C   | 40–55                     | _           | Reserved                                    | _         |

| 5                         | 0           | Temp H Warning LSB <sup>a</sup>  |        | 56–94                     | _           | External Calibration Constants <sup>b</sup> | _         |

| 6                         | 0           | Temp L Warning MSB <sup>a</sup>  | 0°C    | 95                        | _           | Checksum for Bytes 0–94 <sup>c</sup>        | _         |

| 7                         | 0           | Temp L Warning LSB <sup>a</sup>  |        | 96                        | _           | Real Time Temperature MSB <sup>a</sup>      | _         |

| 8                         | 8D          | Vcc H Alarm MSB <sup>d</sup>     | 3.63V  | 97                        | _           | Real Time Temperature LSB <sup>a</sup>      | _         |

| 9                         | CC          | Vcc H Alarm LSB <sup>d</sup>     |        | 98                        | _           | Real Time Vcc MSB <sup>d</sup>              | _         |

| 10                        | 74          | Vcc L Alarm MSB <sup>d</sup>     | 2.97V  | 99                        | _           | Real Time Vcc LSB <sup>d</sup>              | _         |

| 11                        | 04          | Vcc L Alarm LSB <sup>d</sup>     |        | 100                       | _           | Real Time Tx Bias MSB <sup>e</sup>          | _         |

| 12                        | 87          | Vcc H Warning MSB <sup>d</sup>   | 3.465V | 101                       | _           | Real Time Tx Bias LSB <sup>e</sup>          | _         |

| 13                        | 5A          | Vcc H Warning LSB <sup>d</sup>   |        | 102                       | _           | Real Time Tx Power MSB <sup>f</sup>         | _         |

| 14                        | 7A          | Vcc L Warning MSB <sup>d</sup>   | 3.135V | 103                       | _           | Real Time Tx Power LSB <sup>f</sup>         | _         |

| 15                        | 75          | Vcc L Warning LSB <sup>d</sup>   |        | 104                       | _           | Real Time Rx Power MSB <sup>g</sup>         | _         |

| 16                        | 13          | Tx Bias H Alarm MSB <sup>e</sup> | 10 mA  | 105                       | _           | Real Time Rx Power LSB <sup>g</sup>         | _         |

| 17                        | 88          | Tx Bias H Alarm LSB <sup>e</sup> |        | 106                       | _           | Reserved                                    | _         |

| 18                        | 3           | Tx Bias L Alarm MSB <sup>e</sup> | 2 mA   | 107                       | _           | Reserved                                    |           |

| 19                        | E8          | Tx Bias L Alarm LSB <sup>e</sup> |        | 108                       | _           | Reserved                                    | _         |

Table 21: EEPROM Serial ID Memory Contents – Enhanced SFP Memory (Address A2h) (Continued)

| Byte<br>Number<br>Decimal | Data<br>Hex | Notes                               | Values    | Byte<br>Number<br>Decimal | Data<br>Hex | Notes                                             | Values |

|---------------------------|-------------|-------------------------------------|-----------|---------------------------|-------------|---------------------------------------------------|--------|

| 20                        | 10          | Tx Bias H Warning MSB <sup>e</sup>  | 8.5 mA    | 109                       | _           | Reserved                                          | _      |

| 21                        | 9A          | Tx Bias H Warning LSB <sup>e</sup>  |           | 110                       | _           | Status/Control – See Table 22                     | _      |

| 22                        | 5           | Tx Bias L Warning MSB <sup>e</sup>  | 3 mA      | 111                       | _           | Reserved                                          | _      |

| 23                        | DC          | Tx Bias L Warning LSB <sup>e</sup>  |           | 112                       | _           | Flag Bits – See Table 23                          | _      |

| 24                        | C3          | Tx Power H Alarm MSB <sup>f</sup>   | 7 dBm     | 113                       | _           | Flag Bits – See Table 23                          | _      |

| 25                        | C6          | Tx Power H Alarm LSB <sup>f</sup>   |           | 114                       | _           | TX Input EQ – See Table 25 and Table 26           | _      |

| 26                        | 3           | Tx Power L Alarm MSB <sup>f</sup>   | -10.8 dBm | 115                       | _           | RX Output Emphasis – See<br>Table 27 and Table 28 | _      |

| 27                        | 3F          | Tx Power L Alarm LSB <sup>f</sup>   |           | 116                       | _           | Flag Bits – See Table 23                          | _      |

| 28                        | 62          | Tx Power H Warning MSB <sup>f</sup> | 4 dBm     | 117                       | _           | Flag Bits – See Table 23                          | _      |

| 29                        | 1E          | Tx Power H Warning LSB <sup>f</sup> |           | 118                       | _           | Status/Control – See Table 24                     | _      |

| 30                        | 6           | Tx Power L Warning MSB <sup>f</sup> | –7.8 dBm  | 119                       | _           | Status/Control – See Table 17                     | _      |

| 31                        | 7B          | Tx Power L Warning LSB <sup>f</sup> |           | 120–126                   | _           | Reserved                                          | _      |

| 32                        | C3          | Rx Power H Alarm MSB <sup>g</sup>   | 7 dBm     | 127                       | _           | Page Select                                       | _      |

| 33                        | C6          | Rx Power H Alarm LSB <sup>g</sup>   |           | 128–247                   | _           | Custom Configuration Bytes –<br>See Table 29      | _      |

| 34                        | 1           | Rx Power L Alarm MSB <sup>g</sup>   | –13.5 dBm | 248–255                   | _           | Vendor Specific                                   | _      |

| 35                        | BE          | Rx Power L Alarm LSB <sup>g</sup>   |           |                           |             |                                                   |        |

- a. Temperature (Temp) is decoded as a 16-bit signed two's complement integer in increments of 1/256°C.

- b. Bytes 56–94 are not intended for use, but they have been set to default values per SFF-8472.

- c. Byte 95 is a checksum calculated (per SFF-8472) and is stored prior to product shipment.

- d. Supply Voltage (Vcc) is decoded as a 16-bit unsigned integer in increments of 100  $\mu$ V.

- e. Tx bias current (Tx Bias) is decoded as a 16-bit unsigned integer in increments of 2  $\mu$ A.

- f. Transmitted average optical power (Tx Pwr) is decoded as a 16-bit unsigned integer in increments of 0.1  $\mu$ W.

- g. Received average optical power (Rx Pwr) is decoded as a 16-bit unsigned integer in increments of 0.1  $\mu$ W.

Table 22: EEPROM Serial ID Memory Contents - Soft Commands (Address A2h, Byte 110)

| Bit<br>Number | Status/Control Name     | Description                                                                         | Notes |

|---------------|-------------------------|-------------------------------------------------------------------------------------|-------|

| 7             | TX_DISABLE State        | Digital state of TX_DISABLE Input Pin (1 = TX_DISABLE asserted)                     | а     |

| 6             | Soft TX_DISABLE Control | Read/write bit for changing digital state of TX_DISABLE function                    | a, b  |

| 5             | RS(1) State             | Digital state of TX Rate_Select Input Pin RS(1) (1 = Rate High asserted)            | _     |

| 4             | RS(0) State             | Digital state of RX Rate_Select Input Pin RS(0) (1 = Rate High asserted)            | _     |

| 3             | Soft RS(0) Control      | Read/write bit for changing digital state of Rx Rate_Select RS(0) function          | С     |

| 2             | TX_FAULT State          | Digital state of TX_FAULT Output Pin (1 = TX_FAULT asserted)                        | а     |

| 1             | RX_LOS State            | Digital state of SFP RX_LOS Output Pin (1 = RX_LOS asserted)                        | а     |

| 0             | Data Ready (Bar)        | Indicates transceiver is powered and real time sense data is ready (0 = Data Ready) | _     |

- a. The response time for soft commands of the AFBR-57H5MZ is 100 msec as specified by MSA SFF-8472.

- b. Bit 6 is logic ORed with the SFP TX\_DISABLE input pin 3 .... either asserted will disable the SFP transmitter.

- c. Bit 3 is logic ORed with the SFP RS(0) RX Rate\_Select input pin 7 .... either asserted will set receiver to Rate = High.

Table 23: EEPROM Serial ID Memory Contents - Alarms and Warnings (Address A2h, Bytes 112, 113, 116, 117)

| Byte | Bit | Flag Bit Name         | Description                                                                  |

|------|-----|-----------------------|------------------------------------------------------------------------------|

| 112  | 7   | Temp High Alarm       | Set when transceiver internal temperature exceeds high alarm threshold.      |

|      | 6   | Temp Low Alarm        | Set when transceiver internal temperature exceeds low alarm threshold.       |

|      | 5   | Vcc High Alarm        | Set when transceiver internal supply voltage exceeds high alarm threshold.   |

|      | 4   | Vcc Low Alarm         | Set when transceiver internal supply voltage exceeds low alarm threshold.    |

|      | 3   | Tx Bias High Alarm    | Set when transceiver laser bias current exceeds high alarm threshold.        |

|      | 2   | Tx Bias Low Alarm     | Set when transceiver laser bias current exceeds low alarm threshold.         |

|      | 1   | Tx Power High Alarm   | Set when transmitted average optical power exceeds high alarm threshold.     |

|      | 0   | Tx Power Low Alarm    | Set when transmitted average optical power exceeds low alarm threshold.      |

| 113  | 7   | Rx Power High Alarm   | Set when received average optical power exceeds high alarm threshold.        |

|      | 6   | Rx Power Low Alarm    | Set when received average optical power exceeds low alarm threshold.         |

|      | 0–5 | reserved              | _                                                                            |

| 116  | 7   | Temp High Warning     | Set when transceiver internal temperature exceeds high warning threshold.    |

|      | 6   | Temp Low Warning      | Set when transceiver internal temperature exceeds low warning threshold.     |

|      | 5   | Vcc High Warning      | Set when transceiver internal supply voltage exceeds high warning threshold. |

|      | 4   | Vcc Low Warning       | Set when transceiver internal supply voltage exceeds low warning threshold.  |

|      | 3   | Tx Bias High Warning  | Set when transceiver laser bias current exceeds high warning threshold.      |

|      | 2   | Tx Bias Low Warning   | Set when transceiver laser bias current exceeds low warning threshold.       |

|      | 1   | Tx Power High Warning | Set when transmitted average optical power exceeds high warning threshold.   |

|      | 0   | Tx Power Low Warning  | Set when transmitted average optical power exceeds low warning threshold.    |

| 117  | 7   | Rx Power High Warning | Set when received average optical power exceeds high warning threshold.      |

|      | 6   | Rx Power Low Warning  | Set when received average optical power exceeds low warning threshold.       |

|      | 0–5 | reserved              | _                                                                            |

Table 24: EEPROM Serial ID Memory Contents - Soft Commands (Address A2h, Byte 118)

| Bit<br>Number | Status/Control Name                  | Description                                                                | Notes |

|---------------|--------------------------------------|----------------------------------------------------------------------------|-------|

| 4–7           | Reserved                             | _                                                                          | _     |

| 3             | Soft RS(1) Control                   | Read/write bit for changing digital state of Tx Rate_Select RS(1) function | а     |

| 2             | Reserved                             | _                                                                          | _     |

| 1             | Optional Power Level Operation State | Unused.                                                                    | _     |

| 0             | Optional Power Level Select          | Unused.                                                                    | _     |

a. Bit 3 is logic ORed with the SFP RS(1) TX Rate\_Select input pin 9 .... either asserted will set transmitter to Rate = High.

Table 25: EEPROM Serial ID Memory Contents - Transmitter Input Electrical Equalization Control (Address A2h, Byte 114)

| Bit<br>Number | Status/Control Name | Description   | Notes |

|---------------|---------------------|---------------|-------|

| 7–4           | TX EQ, RS(1)=HIGH   | Not supported | _     |

| 3–0           | TX EQ, RS(1)=LOW    | Not supported |       |

Transmitter input equalization control is adaptive. The value written to the register has no effect.

Table 26: Transmitter Input Equalization Control Values (Address A2h, Byte 114)<sup>a</sup>

|      | Transmitter Inp | ut Equalization |

|------|-----------------|-----------------|

| Code | Nominal         | Units           |

| xxxx | Reserved        | _               |

a. From SFF-8472, Table 9-13.

Table 27: EEPROM Serial ID Memory Contents - Receiver Output Electrical Emphasis Control (Address A2h, Byte 115)