## **Data Sheet**

## **AEAT-9955**

# Magnetic Encoder IC: 10-Bit to 18-Bit Programmable Angular Magnetic Encoder with Safety

## **Description**

The Broadcom<sup>®</sup> AEAT-9955 is an angular magnetic rotary sensor that provides accurate angular measurement over a full 360 degrees of rotation.

This sophisticated system uses integrated Hall sensor elements with complex analog and digital signal processing within a single device.

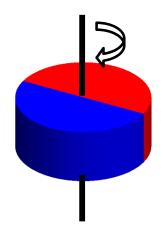

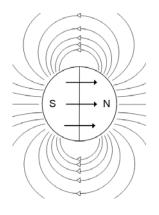

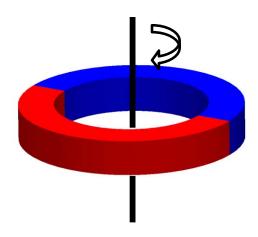

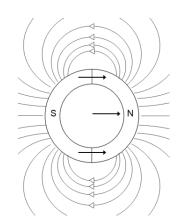

A simple two-pole magnet generates the necessary magnetic field by rotating it in perpendicular. Wide magnetic field sensor configurations allow On Axis (end of shaft) or Off Axis (side of shaft, axial and radial) modes in application.

The AEAT-9955 is a versatile solution capable of supporting a broad range of applications with its robust architecture to measure and deliver both absolute and incremental signals.

The absolute angle measurement provides an instant indication of the magnet's angular position with a selectable and reprogrammable resolution from 10 to 18 bits. When selected, its positioning data is then represented in its digital form to be assessed through a standard SSI (parity) and SPI (with CRC and Parity option) communication protocol.

Where desired, users may also choose to receive its absolute angle position in PWM-encoded output signals. The incremental positions are indicated on ABI and UVW signals with a wide user-configurable resolution from 1 CPR to 20,000 CPR of ABI signals and pole pairs from 1 to 32 pole pairs (2 to 64 poles) for UVW commutation signals.

#### **Features**

- 5V and 3.3V operating voltage

- Operating temperature from –40°C to 125°C

- 300-µA current consumption in Sleep Mode

- Programmable 10 bits up to 18 bits of absolute resolution

- The incremental positions are indicated on ABI and UVW signals with a user-configurable CPR from 1 CPR to 20,000 CPR

- Commutation angle output UVW 1 pp to 32 pp

- Absolute output over 2-wire SSI, 3-wire SSI, 4-wire SPI, and PWM.

- Dedicated output pin for ABI, UVW, and serial interface

- Dedicated zero reset and error pin

- EEPROM architecture for multi-time user configuration

- Optional 56-bit memory lock function

- Automatic integral non-linearity angle correction for high accuracy

- Designed conformance to ISO26262 ASIL-D and SIL3 with secondary chip for redundancy

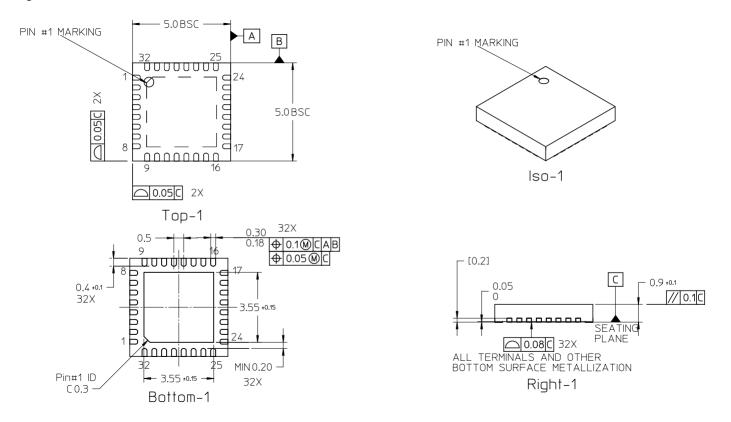

- Compact QFN-32 leads (5 mm × 5 mm) package

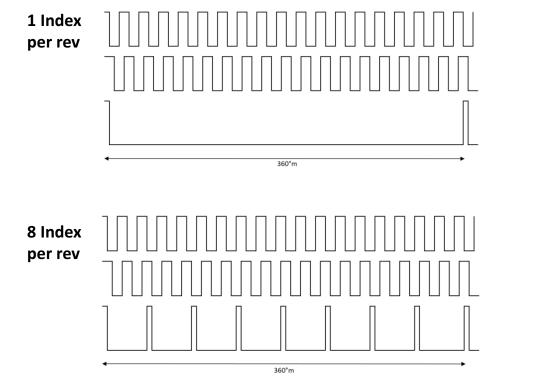

- Multi-index with one revolution

- High-impedance output for multi-slave network

- Qualified automotive standard AEC-Q100 Grade 0

# **Applications**

- Brushless DC motor and stepper motor

- Resolver and potentiometer replacement

- Industrial automation and robotics

- Industrial sewing machine and textile equipment

- Light Detection and Range (LiDAR)

**Disclaimer:** Except as expressly indicated in writing, the component is not designed or guaranteed to be suitable for use in safety-related applications where its failure or malfunction can reasonably be expected to result in injury, death, or severe equipment damage. Customers are solely responsible for determining the suitability of this product for its intended application and solely liable for all loss, damage, expense or liability in connection with such use.

# **Functional Description**

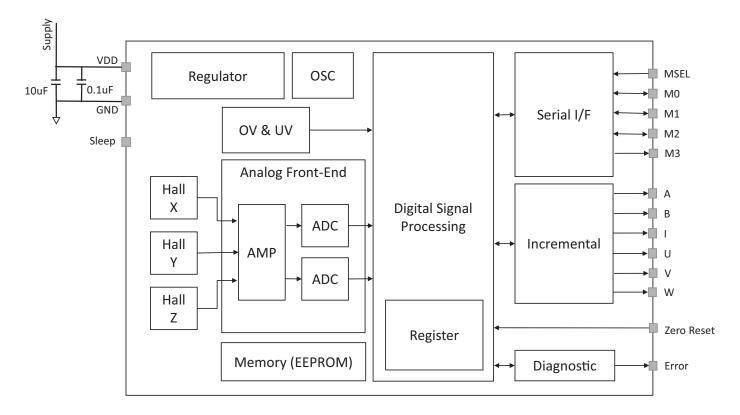

Figure 1: AEAT-9955 Block Diagram

The AEAT-9955 is manufactured with a CMOS standard process. It is capable of accurately measuring a magnet's rotational angle when it is placed in alignment and in perpendicular to the device by using its integrated Hall sensors to detect its magnetic field. The detected magnetic signals are then taken as input signals to be properly conditioned to negate its non-idealities before inputting them into the analog amplifiers for strength amplification and filtering. The amplified analog signals are then fed into the internal analog-to-digital converter (ADC) to be converted into digital signals for the final stage of digital processing. The digital processing provides a digitized output of the absolute and incremental signals.

The magnet used should have sufficient magnetic field strength (mT) to generate the magnetic field for the signal generation as highlighted in Recommended Magnetic Input Specifications. The device provides digital information of magnetic field strength high (MHI) and magnetic field strength low (MLO) from output protocols to indicate whether the magnets are too close or too far away from our device's surface.

Users can assess the device's digitized absolute data using standard Synchronous Serial Interface (SSI) or Serial Peripheral Interface (SPI) protocols. In addition, an absolute angular representation can also be selected using a pulse-width modulated (PWM) signal.

The incremental outputs are available from the digital outputs of their dedicated A, B, and I pins and the commutation output U, V, and W.

# **Pin Assignment**

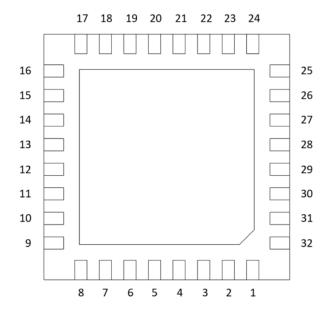

Figure 2: Pin Configurations (Bottom View)

Figure 3: Label Information

AEAT-0000 = Product Part Number

YYWW = Package Assembly Date

XXXXXX= Assembly Lot Number

# **Pinout Description**

| Pin QFN32 | Pin Name | Pin Type | Description            | Pin QFN32 | Pin Name | Pin Type | Description             |

|-----------|----------|----------|------------------------|-----------|----------|----------|-------------------------|

| 1         | n.c      | _        | _                      | 17        | Zero     | I        | Zero Reset, Active High |

| 2         | MO       | I/O      | Serial Interface M0    | 18        | n.c      | _        | _                       |

| 3         | n.c      | _        | _                      | 19        | ERR      | 0        | Error, Active High      |

| 4         | M1       | I/O      | Serial Interface M1    | 20        | n.c      | _        | _                       |

| 5         | n.c      | _        | _                      | 21        | MSEL     | I        | Interface Select        |

| 6         | M2       | I/O      | Serial Interface M2    | 22        | n.c      | _        | _                       |

| 7         | M3       | 0        | Serial Interface M3    | 23        | n.c      | _        | _                       |

| 8         | Α        | 0        | Incremental A          | 24        | n.c      | _        | _                       |

| 9         | В        | 0        | Incremental B          | 25        | n.c      | _        | _                       |

| 10        | I        | 0        | Incremental I          | 26        | n.c      | _        | _                       |

| 11        | U        | 0        | Commutation U          | 27        | n.c      | _        | _                       |

| 12        | n.c      |          | _                      | 28        | VSS      | Supply   | Ground Supply           |

| 13        | V        | 0        | Commutation V          | 29        | n.c      | _        | _                       |

| 14        | n.c      | _        | _                      | 30        | VDD      | Supply   | Power Supply            |

| 15        | W        | 0        | Commutation W          | 31        | n.c      | _        | _                       |

| 16        | Sleep    | I        | Sleep Mode, Active Low | 32        | n.c      | _        | _                       |

NOTE: Backside pad connects to VSSA.

# **Absolute Maximum Ratings**

| Parameter                     | Symbol          | Min. | Max. | Units |

|-------------------------------|-----------------|------|------|-------|

| Storage Temperature           | T <sub>S</sub>  | -40  | 125  | °C    |

| Junction Temperature          | T <sub>J</sub>  | -40  | 150  | °C    |

| DC Supply Voltage             |                 |      |      |       |

| VDDA Pin                      | VDD             | -0.3 | 6.06 | V     |

| Input Voltage Range           | V <sub>in</sub> | -0.3 | 6    | V     |

| Electrostatic Discharge (HBM) | _               | -4.0 | +4.0 | kV    |

| Moisture Sensitivity Level    | _               | _    | 1    | _     |

**CAUTION!** Subjecting the product to stresses beyond those listed in this section may cause permanent damage to the devices. These are stress ratings only and do not imply that the devices will function beyond these ratings. Exposure to the extremes of these conditions for extended periods may affect product reliability.

## **Electrical Characteristics**

# **Recommended Operating Conditions**

| Parameter                     | Symbol           | Min.            | Тур. | Max. | Units | Notes                              |

|-------------------------------|------------------|-----------------|------|------|-------|------------------------------------|

| Operating Ambient Temperature | T <sub>A</sub>   | <del>-4</del> 0 | _    | 125  | °C    |                                    |

| DC Supply Voltage to VDD Pin  |                  |                 |      |      |       |                                    |

| 5V Operation                  | VDD              | 4.5             | 5.0  | 5.5  | V     |                                    |

| 3.3V Operation                |                  | 3.0             | 3.3  | 3.6  | V     |                                    |

| Incremental Output Frequency  | f <sub>MAX</sub> | _               | _    | 1.0  | MHz   | Frequency = Velocity(rpm) × CPR/60 |

| Load Capacitance              | C <sub>L</sub>   |                 | _    | 15   | pF    |                                    |

# **Systems Parameters**

Condition: Electrical characteristics over the recommended operating conditions. Typical values specified at VDD = 5.0V and 25°C, optimum placement of magnet.

| Parameter                                  | Symbol              | Min.      | Тур. | Max.      | Units | Notes            |

|--------------------------------------------|---------------------|-----------|------|-----------|-------|------------------|

| Current Consumption                        |                     |           |      |           |       |                  |

| Contrado Comercia National Contradio Maria | IDD <sub>NOM</sub>  | _         | 24   | _         | mA    | 5V               |

| Supply Current Normal Operation Mode       | IDD <sub>NOM</sub>  | _         | 22   | _         | mA    | 3.3V             |

| Supply Current Sleep Mode                  | IDD <sub>IDLE</sub> | _         | 300  | _         | μΑ    | 5V and 3.3V      |

| Digital Outputs (DO)                       |                     |           |      |           |       |                  |

| High Level Output Voltage                  | V <sub>OH</sub>     | VDD - 0.5 | _    | _         | V     | Normal operation |

| Low Level Output Voltage                   | V <sub>OL</sub>     | _         | _    | GND + 0.4 | V     |                  |

| Power-up time                              | t <sub>PwrUp</sub>  | _         | 10   | _         | ms    |                  |

| Absolute Output                            |                     |           |      |           |       |                  |

| Incremental Output                         |                     |           |      |           |       |                  |

| PWM Output                                 |                     |           |      |           |       |                  |

| Digital Inputs (DI)                        | <u>'</u>            | ,         |      | •         |       |                  |

| Input High Level                           | V <sub>IH</sub>     | 0.7 × VDD | _    | _         | V     |                  |

| Input Low Level                            | V <sub>IL</sub>     | _         | _    | 0.3 × VDD | V     |                  |

| Pull-Up Low Level Input Current            | I <sub>IL</sub>     | _         | _    | 120       | μΑ    |                  |

| Pull-Down High Level Input Current         | I <sub>IH</sub>     | _         | _    | 120       | μΑ    |                  |

# **Encoding Characteristics**

| Parameter                          | Symbol               | Min. | Тур.  | Max.  | Units | Notes                                                                         |

|------------------------------------|----------------------|------|-------|-------|-------|-------------------------------------------------------------------------------|

| System Input                       |                      |      |       |       |       |                                                                               |

| Maximum Speed                      | S <sub>MAX</sub>     | _    | _     | 30000 | RPM   | _                                                                             |

| Absolute Output                    |                      |      | 1     |       |       |                                                                               |

| Resolution                         | RES                  | 10   | _     | 18    | Bit   | Programmable 10 to 18 bits.                                                   |

| Integral Non-Linearity ON-Axis     | - INL <sub>nom</sub> | _    | ±0.05 | _     | Deg   | Best fit line, centered magnet.  T <sub>A</sub> = 25°C, Voltage = 5V,         |

| Integral Non-Linearity<br>OFF-Axis | IIV_nom              | _    | ±0.15 | _     | Deg   | INL angle correction.                                                         |

| Integral Non-Linearity<br>ON-Axis  | INII                 | _    | ±0.15 | _     | Dog   | Best fit line, over displacement of magnet $T_A = 25$ °C, Voltage = 5V        |

| Integral Non-Linearity OFF-Axis    | INL <sub>dis</sub>   | _    | ±0.25 | _     | Deg   |                                                                               |

| Integral Non-Linearity ON-Axis     | INII                 | _    | ±0.10 | _     | D     | Best fit line, over temperature range.<br>$T_A = -40$ to +125°C, Voltage = 5V |

| Integral Non-Linearity OFF-Axis    | INL <sub>temp</sub>  | _    | ±0.40 | _     | Deg   |                                                                               |

| Differential Non-Linearity         | DNL <sub>nom</sub>   | _    | ±0.02 | _     | Deg   | T <sub>A</sub> = 25°C, Voltage = 5V                                           |

| Output Sampling Rate               | f <sub>S</sub>       | _    | 10    | _     | MHz   | Based on the SSI protocol.                                                    |

| Latency                            | _                    | _    | 80    | _     | ns    | At constant speed.                                                            |

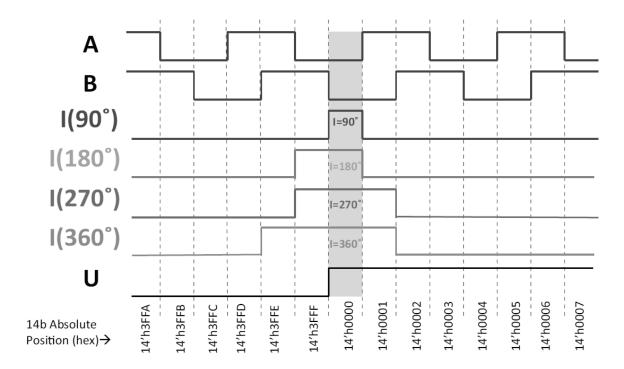

| Incremental Output (Cha            | nnel ABI)            |      | *     | 1     |       |                                                                               |

| Resolution                         | R <sub>INC</sub>     | 1    | _     | 20000 | CPR   | Programmable.                                                                 |

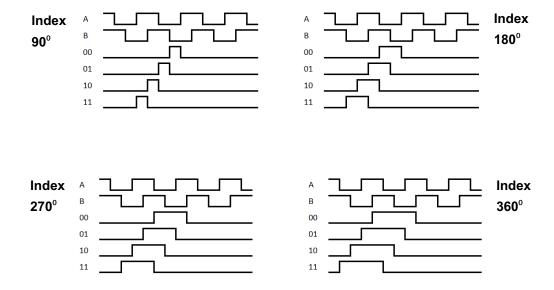

| Index Pulse Width                  | P <sub>O</sub>       | 90   | _     | 360   | °e    | Programmable options: 90, 180, 270, or 360°e. See Figure 4.                   |

| Index Pulse State                  | P <sub>S</sub>       | 90   | _     | 360   | °e    | Relation between Index output to Incremental AB state.                        |

|                                    |                      |      |       |       |       | Programmable options: 0, 90, 180, or 270°e. See Figure 4.                     |

| Index State                        | _                    | 90   | _     | 360   | °e    | Programmable options: 90, 180, 270, or 360°e. See Figure 4.                   |

| PWM Output                         |                      |      |       |       |       |                                                                               |

| PWM Frequency                      | $f_{PWM}$            | 122  | _     | 976   | Hz    | Adjustable based on our PWM settings.                                         |

| Minimum Pulse Width                | PW <sub>MIN</sub>    | _    | 1     | _     | μs    | _                                                                             |

| Maximum Pulse Width                | PW <sub>MAX</sub>    | _    | 16384 | _     | μs    | _                                                                             |

**NOTE:** Encoding characteristics over recommended operating range unless otherwise specified.

# **Recommended Magnetic Input Specifications**

| Parameter                                         | Symbol | Min. | Тур.  | Max. | Units | Notes                                                       |

|---------------------------------------------------|--------|------|-------|------|-------|-------------------------------------------------------------|

| Diameter                                          |        |      |       |      |       | Recommended magnet: Cylindrical magnet or                   |

| Disc magnet                                       | d      | 4    | 6     |      | mm    | ring magnet diametrically magnetized and one                |

| Ring magnet ID                                    | u      | _    | ID,15 | _    | mm    | pole pair.                                                  |

| /OD                                               |        |      | OD,25 | _    | mm    |                                                             |

| Thickness                                         |        |      |       |      |       |                                                             |

| Disc magnet                                       | t      | _    | 2.5   | _    | mm    |                                                             |

| Ring magnet                                       |        | 4    | 6     | _    | mm    |                                                             |

| Magnetic input field magnitude                    |        |      |       |      |       | Required vertical/horizontal component of the               |

| On-axis (disc magnet)                             | Bpk    | 45   | _     | 100  | mT    | magnetic field strength on the die's surface,               |

| Off-axis (ring magnet)                            |        | 30   | _     | 150  | mT    | measured along concentric circle.                           |

| Magnet displacement radius                        | R_m    | _    | _     | 0.25 | mm    | Displacement between the magnet axis and the device center. |

| Recommended magnet material and temperature drift | _      | _    | -0.12 | _    | %/K   | NdFeB (Neodymium Iron Boron), grade N35SH.                  |

# **Diametrically Magnetized Magnet**

# **Magnet and IC Package Placement**

AEAT-9955 multi-axis capability comes from multiple integrated Hall devices that allow flexibility on the sensor mounting with respect to the magnet. Generally, the shaft end configuration senses the vertical field (Z component perpendicular to the chip surface), and the rest of the configuration senses the horizontal field (X and Y components parallel to the chip surface).

The nominal mounting tolerance is indicated the following table.

| Configuration | Gap Tolerance | X-Y Tolerance                              |

|---------------|---------------|--------------------------------------------|

| Shaft End     | 1.00 ± 0.25mm | ± 0.25mm<br>magnet axis<br>center          |

| Side Shaft    | 11.00 ±0.25mm | X Center to magnet X thickness             |

| Axial         | 1.00 ± 0.25mm | ± 0.25mm<br>from center of<br>magnet width |

| Radial        | 1.50 ±0.25mm  | X Center to magnet X thickness             |

## **Serial Interface Format**

The AEAT-9955 serial interface hosts up to 10 different protocols for position output and memory access. The protocol is configurable with the combination of the physical I/O MSEL and M0 and memory settings PSEL, SPI4[0], and SPI4[1]. The default factory setting is all zeros, which is either SPI3 or SPI4-16a depending on the MSEL state. The output pin can be configured to high impedance mode for multi slave connection or bus connection.

All protocol selection can be switched during operation.

#### MATS Table

| Mode<br>Pin | SPI3 | SSI3a | SSI3b | SSI2a | SSI2b | SPI4-16a | SPI4-16b | SPI4-16c | SPI4-8 | PWM |

|-------------|------|-------|-------|-------|-------|----------|----------|----------|--------|-----|

| MSEL        | 0    | 0     | 0     | 0     | 0     | 1        | 1        | 1        | 1      | 1   |

| PSEL        | Х    | 0     | 1     | 0     | 1     | 0        | 0        | 0        | 0      | 1   |

| SPI4[1]     | Х    | Х     | Х     | Х     | Х     | 0        | 0        | 1        | 1      | Х   |

| SPI4[0]     | Х    | Х     | Х     | Х     | Х     | 0        | 1        | 0        | 1      | Х   |

| M0          | 0    | 1     | 1     | 1     | 1     | NCS      | NCS      | NCS      | NCS    | -   |

| M1          | DIN  | NSL   | NSL   | 0     | 0     | MOSI     | MOSI     | MOSI     | MOSI   | -   |

| M2          | SCK  | SCL   | SCL   | SCL   | SCL   | SCK      | SCK      | SCK      | SCK    | -   |

| M3          | DO   | DO    | DO    | DO    | DO    | MISO     | MISO     | MISO     | MISO   | PWM |

NOTE: PSEL, SPI4[1], and SPI4[0] are configured through memory. MSEL and M0 are configured through I/O pads.

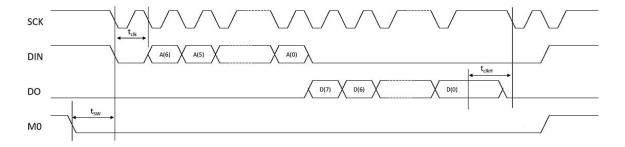

## **Serial Peripheral Interface (SPI3)**

SPI3 protocols allow access to memory read write only. Assert 0 on the MSEL and M0 pin to configure it. The SPI is implemented with CPOL=0 and CPHA=0; data is propagated on the clock falling edge.

- M1 → SPI\_Data Input (DIN) signal for the SPI protocol, input to the AEAT-9955.

- M2 → SPI Clock Input (SCK) signal for the SPI protocol, input to the AEAT-9955.

- M3 → SPI\_Data Output (DO) signal for the SPI protocol, output from the AEAT-9955.

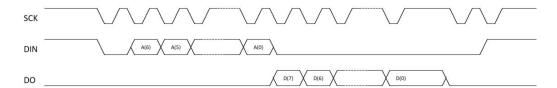

#### **SPI3 Timing Diagram**

| Symbol            | Description                                               | Min. | Тур. | Max. | Unit |

|-------------------|-----------------------------------------------------------|------|------|------|------|

| t <sub>SW</sub>   | Time between the SCn falling edge and the CLK rising edge | 1    | _    | _    | μs   |

| t <sub>clk</sub>  | Serial clock period                                       | _    | _    | 100  | ns   |

| t <sub>clkH</sub> | CLK high time after the end of the last clock period      | 300  | _    | _    | ns   |

NOTE: The user should read back data to confirm that it has been written successfully.

#### SPI3 Read

#### SPI3 Write

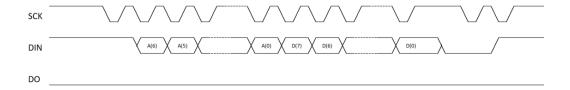

## **Serial Peripheral Interface (SPI4)**

The SPI protocol uses four pins from the AEAT-9955. These four pins are shared between the UVW, SSI, and SPI protocols. To select the SPI4 protocol, assert 1 on the MSEL pin.

SPI4 protocols allow the user to access memory read or write and position data. It uses CPOL=0, CPHA=1 for triggering.

- M0 → SPI Chip Select (NCS) signal for the SPI protocol, input to the AEAT-9955.

- M1 → SPI\_Data Input (MOSI) signal for the SPI protocol, input to the AEAT-9955.

- M2 → SPI Clock Input (SCK) signal for the SPI protocol, input to the AEAT-9955.

- M3 → SPI\_Data Output (MISO) signal for the SPI protocol, output from the AEAT-9955.

#### **SPI4 Timing Diagram**

| Symbol            | Description                                               | Min. | Тур. | Max. | Unit |

|-------------------|-----------------------------------------------------------|------|------|------|------|

| t <sub>L</sub>    | Time between the SCn falling edge and the CLK rising edge | 350  | _    | _    | ns   |

| t <sub>clk</sub>  | Serial clock period                                       | 100  | _    | _    | ns   |

| t <sub>clkL</sub> | Low period of the serial clock                            | 50   | _    | _    | ns   |

| t <sub>clkH</sub> | High period of the serial clock                           | 50   | _    | _    | ns   |

| Symbol            | Description                                                          | Min.                | Тур. | Max. | Unit |

|-------------------|----------------------------------------------------------------------|---------------------|------|------|------|

| t <sub>H</sub>    | Time between the last falling edge of CLK and the rising edge of CSn | t <sub>clk</sub> /2 | _    | _    | ns   |

| t <sub>CSn</sub>  | High time of CS between two transmissions                            | 350                 | _    | _    | ns   |

| t <sub>MOSI</sub> | Data input valid to clock edge                                       | 20                  | _    | _    | ns   |

| t <sub>MISO</sub> | CLK edge to data output valid                                        | _                   | _    | 51   | ns   |

| t <sub>OZ</sub>   | Time between the CSn rising edge and the MISO HiZ                    | _                   | _    | 10   | ns   |

NOTE: The user should read back data to confirm that it has been written successfully.

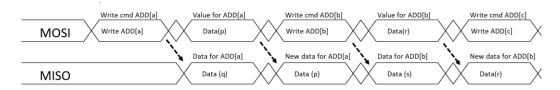

#### **SPI4 Command and Data Frame**

#### SPI4 Read Sequence

### SPI4 Write Sequence

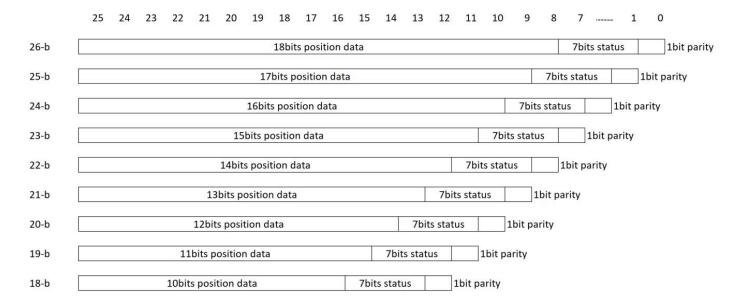

## SPI-4(A) 16-Bit (Parity)

By default, the chip is configured to SPI4 16-bit selection; PSEL = 0, SPI4[1] = 0, SPI4[0] = 0 in the register setting.

Controller to Peripheral

Peripheral to Controller (memory)

Peripheral to Controller (pos 10b)

Peripheral to Controller (pos 11b)

Peripheral to Controller (pos 12b)

Peripheral to Controller (pos 13b)

Peripheral to Controller (pos 14b)

Peripheral to Controller (pos 15b)

Peripheral to Controller (pos 16b)

Peripheral to Controller (pos 17b)

Peripheral to Controller (pos 17b)

Peripheral to Controller (pos 18b)

P: Parity EF: Error Flag

RW: Read = 1, Write = 0

|    |    |    |    | Data Format |                   |                       |                            |    |    |       |       |   |   |   |   |   |   |   |   |  |

|----|----|----|----|-------------|-------------------|-----------------------|----------------------------|----|----|-------|-------|---|---|---|---|---|---|---|---|--|

| 19 | 18 | 17 | 16 | 15          | 14                | 13                    | 12                         | 11 | 10 | 9     | 8     | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|    |    |    |    | Р           | RW                | 0                     | 0 0 0 0 0 0 Addr/Data[7:0] |    |    |       |       |   |   |   |   |   |   |   |   |  |

|    |    |    |    | Р           | EF                | 0 0 0 0 0 0 Data[7:0] |                            |    |    |       |       |   |   |   |   |   |   |   |   |  |

|    |    |    |    | Р           | P EF Pos[9:0] 0 0 |                       |                            |    |    |       |       |   |   |   |   | 0 | 0 |   |   |  |

|    |    |    |    | Р           | EF Pos[10:0] 0    |                       |                            |    |    |       |       |   |   |   |   | 0 | 0 |   |   |  |

|    |    |    |    | Р           | P EF Pos[11:0]    |                       |                            |    |    |       |       |   |   |   | 0 | 0 |   |   |   |  |

|    |    |    |    | Р           | EF                |                       |                            |    |    | Pos[2 | 12:0] |   |   |   |   |   |   |   | 0 |  |

|    |    | _  |    | Р           | EF                |                       |                            |    |    | Pos[1 | L3:0] |   |   |   |   |   |   |   |   |  |

|    | _  |    | Р  | EF          |                   |                       |                            |    |    | Pos[2 | L4:0] |   |   |   |   |   |   |   |   |  |

| _  |    | Р  | EF |             | Pos[15:0]         |                       |                            |    |    |       |       |   |   |   |   |   |   |   |   |  |

|    | Р  | EF |    |             |                   | Pos[16:0]             |                            |    |    |       |       |   |   |   |   |   |   |   |   |  |

| Р  | EF |    |    | Pos[17:0]   |                   |                       |                            |    |    |       |       |   |   |   |   |   |   |   |   |  |

### **SPI4-(B) 24-Bit (CRC)**

To configure the chip to SPI4 24-bit selection, set PSEL = 0, SPI4[1] = 0, SPI4[0] = 1 in the register setting.

| Controller to Peripheral           |

|------------------------------------|

| Peripheral to Controller (memory)  |

| Peripheral to Controller (pos 10b) |

| Peripheral to Controller (pos 11b) |

| Peripheral to Controller (pos 12b) |

| Peripheral to Controller (pos 13b) |

| Peripheral to Controller (pos 14b) |

| Peripheral to Controller (pos 15b) |

| Peripheral to Controller (pos 16b) |

| Peripheral to Controller (pos 17b) |

| Peripheral to Controller (pos 18b) |

|    |    |    |                        |    |    |                        |                      |    |    |      |       | Da | ata F | orma | t     |       |     |   |   |   |   |   |       |      |   |   |   |

|----|----|----|------------------------|----|----|------------------------|----------------------|----|----|------|-------|----|-------|------|-------|-------|-----|---|---|---|---|---|-------|------|---|---|---|

| 27 | 26 | 25 | 24                     | 23 | 22 | 21                     | 20                   | 19 | 18 | 17   | 16    | 15 | 14    | 13   | 12    | 11    | 10  | 9 | 8 | 7 | 6 | 5 | 4     | 3    | 2 | 1 | 0 |

|    |    |    |                        | 0  | RW | 0                      | 0                    | 0  | 0  | 0    | 0     |    |       | Add  | dr/Da | ta[7: | :0] |   |   |   |   | ( | CRC[7 | 7:0] |   |   |   |

|    |    |    |                        | W  | Е  | 0                      | 0                    | 0  | 0  | 0    | 0     |    |       |      | Data[ | 7:0]  |     |   |   |   |   | ( | CRC[7 | 7:0] |   |   |   |

|    |    |    |                        | W  | Е  |                        |                      |    |    | Pos[ | 9:0]  |    |       |      |       | 0     | 0   | 0 | 0 |   |   | ( | CRC[7 | 7:0] |   |   |   |

|    |    |    |                        | W  | Ε  |                        |                      |    |    | Pos[ | 10:0] |    |       |      |       |       | 0   | 0 | 0 |   |   | ( | CRC[7 | 7:0] |   |   |   |

|    |    |    |                        | W  | Е  | Pos[11:0] 0 0 CRC[7:0] |                      |    |    |      |       |    |       |      |       |       |     |   |   |   |   |   |       |      |   |   |   |

|    |    |    |                        | W  | Е  |                        | Pos[12:0] 0 CRC[7:0] |    |    |      |       |    |       |      |       |       |     |   |   |   |   |   |       |      |   |   |   |

|    |    |    |                        | W  | Ε  | E Pos[13:0] CRC[7:0]   |                      |    |    |      |       |    |       |      |       |       |     |   |   |   |   |   |       |      |   |   |   |

|    |    |    | W E Pos[14:0] CRC[7:0] |    |    |                        |                      |    |    |      |       |    |       |      |       |       |     |   |   |   |   |   |       |      |   |   |   |

|    |    | W  | E Pos[15:0] CRC[7:0]   |    |    |                        |                      |    |    |      |       |    |       |      |       |       |     |   |   |   |   |   |       |      |   |   |   |

|    | W  | Ε  | Pos[16:0] CRC[7:0]     |    |    |                        |                      |    |    |      |       |    |       |      |       |       |     |   |   |   |   |   |       |      |   |   |   |

| W  | Ε  |    | Pos[17:0] CRC[7:0]     |    |    |                        |                      |    |    |      |       |    |       |      |       |       |     |   |   |   |   |   |       |      |   |   |   |

W: Warning E: Error

RW: Read = 1, Write = 0

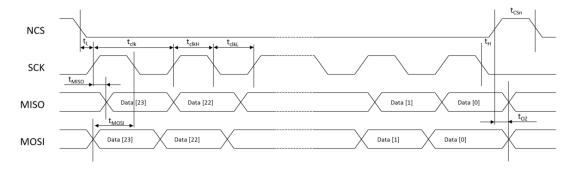

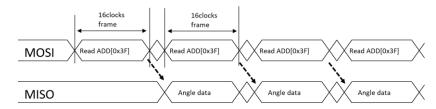

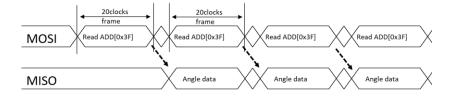

#### **Position Read**

Absolute position data can be obtained by sending a read command to address 0x3F.

In the event of higher single-turn resolution (15-bit and above), the command and data frame size is adjusted accordingly.

Example: 18bit + 2bit (parity and error)

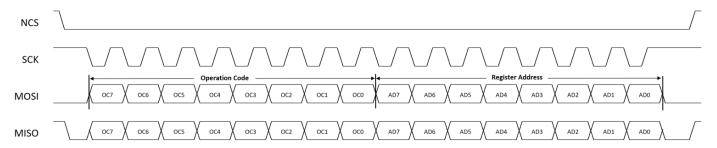

### **SPI4-8**

To configure the chip to SPI4 24-bit selection, set PSEL = 0, SPI4[1] = 1, SPI4[0] = 1 in the register setting.

When NCS is low, the communication line is activated and the data is sampled on the rising edge of SCK.

The MISO state turns to high impedance mode (hi-Z) when NCS is high. The transmission works over specific operation code (OC).

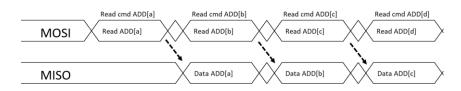

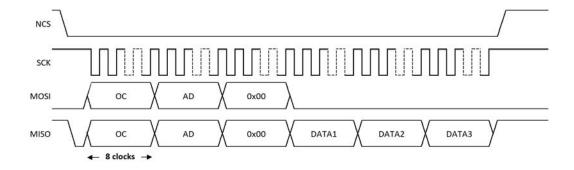

#### Register Read (OC=0x81'h)

This operation is used to read data from the internal register of the chip. It can be performed consecutively starting from any register address. The data continues to be transmitted as long the clock (SCK) is sent and the chip select (NCS) remains active.

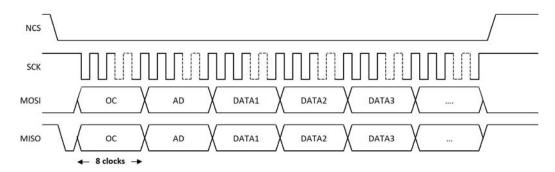

#### Register Write (OC=0xCF'h)

This operation is used to write data into the internal register of the chip. It can be performed consecutively starting from any register address. The subsequent data byte is written into the next register address (AD+1), while the NCS signal stays active. Complete written data is transmitted back via MISO.

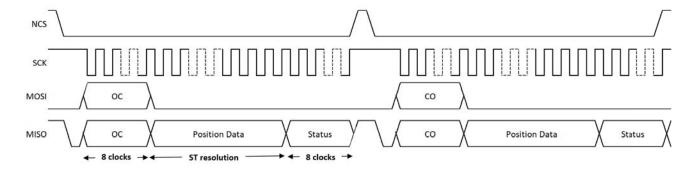

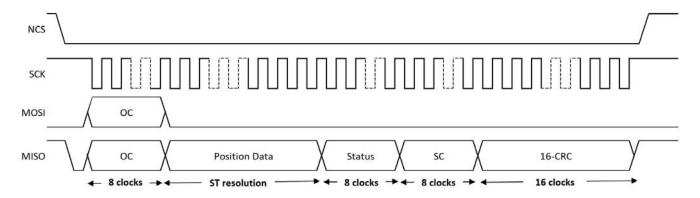

#### Position Read (OC=0xA6'h)

Read the absolute position by sending the operation code, and the data will be transmitted on the MISO line. The position data consists of the single-turn position data length and status byte. The position data length follows the single-turn resolution setting.

For safety format, there are additional bytes: sequence counter (SC) and CRC.

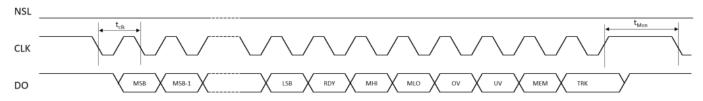

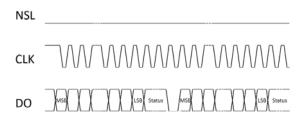

# Serial Synchronous Interface 3-Wire (SSI3)

The SSI3 protocol uses three pins from the AEAT-9955. These three pins are shared between the UVW, SSI, and SPI protocols. To activate the SSI3 protocol, assert 0 on the MSEL pin and assert 1 on the M0 pin.

- M1 → SSI NSL Input (NSL) signal for the SSI protocol, input to the AEAT-9955.

- M2 → SSI\_Clock Input (CLK) signal for the SSI protocol, input to the AEAT-9955.

- M3 → SSI\_Data Output (DO) signal for the SSI protocol, output from the AEAT-9955.

It is available in two options per PSEL register setting.

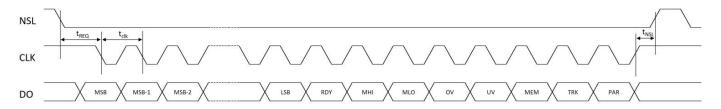

#### SSI Protocol Timing Diagram. Default: Data Output with 3-Wire SSI to 10-MHz Clock Rates

| Symbol           | Description                                                               | Min. | Тур. | Max. | Unit |

|------------------|---------------------------------------------------------------------------|------|------|------|------|

| t <sub>clk</sub> | SSI_SPI_SEL switch time                                                   | 1    | _    | _    | μs   |

| t <sub>REQ</sub> | SCL high time between the NSL falling edge and the first SCL falling edge | 300  | _    | _    | ns   |

| t <sub>NSL</sub> | NSL high time between two successive SSI reads                            | 200  | _    | _    | ns   |

## SSI3(A)

By default, the chip is configured to SSI3(A) selection; PSEL = 0 in the register setting.

The DO pin is held at a high state once the NSL pin is high.

## SSI3(B)

To configure the chip to SSI3(B) selection, set PSEL = 1 in the register setting.

The DO pin is at a tristate (high-impedance) state once the NSL pin is high.

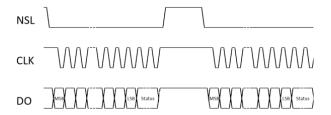

## Serial Synchronous Interface 2-Wire (SSI2)

The SSI2 protocol uses two pins from the AEAT-9955. These two pins are shared between the SSI and SPI protocols. To activate the SSI2 protocol, assert 0 on the MSEL and M1 pins and assert 1 on the M0 pin upon power-up.

- M2 → SSI\_Clock Input (CLK) signal for the SSI protocol, input to the AEAT-9955.

- M3 → SSI\_Data Output (DO) signal for the SSI protocol, output from the AEAT-9955.

Depending on the PSEL setting, it can be configured as SSI2(A) Ring Mode or SSI2(B) No Ring Mode.

Data is latched on the first CLK falling edge and is transmitted on the next falling edge.

| Symbol           | Description                                     | Min. | Тур. | Max.              | Unit |

|------------------|-------------------------------------------------|------|------|-------------------|------|

| t <sub>clk</sub> | Serial clock period                             | 250  | _    | t <sub>M</sub> /2 | ns   |

| t <sub>M</sub>   | Time required to place the chip in standby mode | _    | 16.5 | 18.0              | μs   |

## SSI2(A)

By default, the chip is configured to SSI2(A) selection; PSEL = 0 in the register setting.

Outputs single data position and remains low after LSB until the next monoflop (t<sub>M</sub>) expires.

| NSL |     |

|-----|-----|

| CLK |     |

| DO  | MSB |

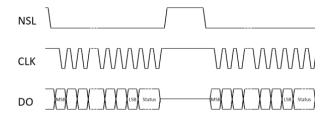

### SSI2(B)

To configure the chip to SSI2(B) selection, set PSEL = 1 in the register setting.

The same position data can be continuously output by sending clock train, and the data is separated by a single low pulse.

Data will be refreshed when the next monoflop (t<sub>M</sub>) expires.

#### **SSI READ Data Format**

#### NOTE:

- 7-b status: {Ready, MHI, MLO, OV, UV, Mem, Trck}

- See Status and Alarm for more details.

### **Safety and Non-safety Protocol Format**

The position serial interface is available in Safety and Non-safety format; applicable for SSI3, SSI2, and SPI-8.

| Position (n-bit)  |                 | Stati | us / Alarm (2 | 7-bit)      |     |     | Parity (1-bit) | )            |                  |

|-------------------|-----------------|-------|---------------|-------------|-----|-----|----------------|--------------|------------------|

| Position[(n-1):0] | READY MH        | MLO   | OV            | UV          | MEM | TRK | parity         |              |                  |

|                   |                 |       |               |             | •   |     |                |              |                  |

|                   |                 |       |               |             |     |     |                |              |                  |

| Position (n-bit)  |                 |       | Status / Al   | arm (8-bit) |     |     |                | SC (8-bit)   | CRC (8/16-bit)   |

| Position[(n-1):0] | Status[1:0] (1) | MHI   | MLO           | OV          | UV  | MEM | TRK            | SC [7:0] (2) | CRC [7/15:0] (3) |

#### NOTE:

- 1. 2-bit status to indicate the safety status:

- Status = 2b'00 Encoder not ready.

- Status = 2b'01 Encoder not ready, Force test failed.

- Status = 2b'10 Encoder ready.

- Status = 2b'11 Encoder ready, Force test passed.

- 2. SC denotes as *Sequence Count* or life counter that automatically increments on every position transmission. The counting starts from 1 to 255, and the initial value upon power-up is configurable.

- 3. CCRC polynomial 16b-CRC is 0x1021'h and 8b-CRC is 0x1D'h. Initial value is configurable (0x0000, 5555, AAAA, FFFF).

#### **Status and Alarm**

The error bit is triggered if Magnet High (MHI), Magnet Low (MLO), Memory Error (MEM), or communication error. Details of the error bit are available in the following register address.

|         | Bit    |        |     |     |    |    |     |       |  |  |

|---------|--------|--------|-----|-----|----|----|-----|-------|--|--|

| Address | 7      | 6      | 5   | 4   | 3  | 2  | 1   | 0     |  |  |

| 0x29    | RDY[1] | RDY[0] | MHI | MLO | OV | UV | MEM | TRACK |  |  |

- Ready: The chip is ready, and the ready value is 1.

- Parity: 1-b parity is even parity.

- Magnet High (MHI) Error: This indicates that the magnet strength detected by the chip is too strong. When this is set high consistently, change to a weaker magnet or increase the distance between the chip and the magnet. The value for this alarm is represented as 1.

- Magnet Low (MLO) Error: This indicates that the magnet strength detected by the chip is too weak. When this is set low consistently, change to a stronger magnet or decrease the distance between the chip and the magnet. The value for this alarm is represented as 1.

- Overvoltage (OV) Error: This indicates that the input supply has exceeded the limit. When this is set high consistently, check the supply line. The value for this alarm is represented as 1.

- Undervoltage (UV) Error: This indicates that the input supply has dropped below the limit. When this is set high

consistently, check the supply line. The value for this alarm is represented as 1.

- Memory Error (MEM) Error: This indicates that memory corruption has occurred. When this is set high, perform a power-cycle to reload the memory. The value for this alarm is represented as 1.

- **Tracker (TRK) Error:** This indicates that the angular error has exceeded 5° within 5 ms. When this is set high consistently, perform a power-cycle to re-initialize the sensor. The value for this alarm is represented as 1.

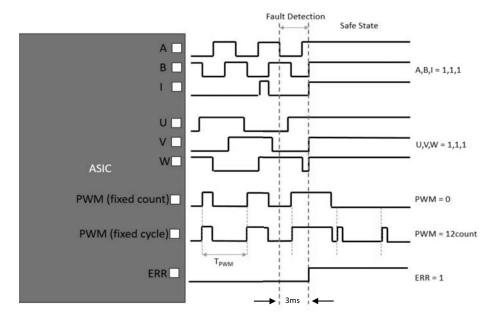

The ERR pin is a dedicated hardware pin for error indication and will automatically be cleared once all error bits in the register are cleared. It is a push-pull output configuration; float if unused.

Clear the alarm register by sending 0x3F'h to address 0x12'h.

Under Safety Mode, once fault is detected, the error pin flags to high after 3ms. The incremental ABI, the commutation UVW, and PWM enter Safe State.

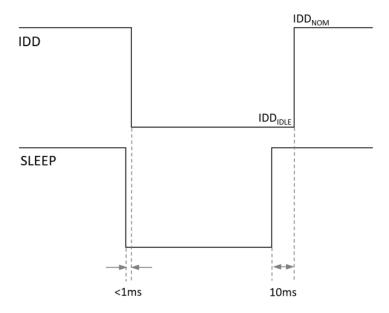

## **Power Modes**

The AEAT-9955 is designed with two power modes:

- Active Mode where the chip operates under full functions with normal current consumption, IDD<sub>NOM</sub>.

- **Sleep Mode** powers down the chip front-end and digital processing blocks, leaving only the detection block to track on user input with low current consumption, IDD<sub>IDLE</sub>. The SLEEP pin is an active low, tied to VDD is unused.

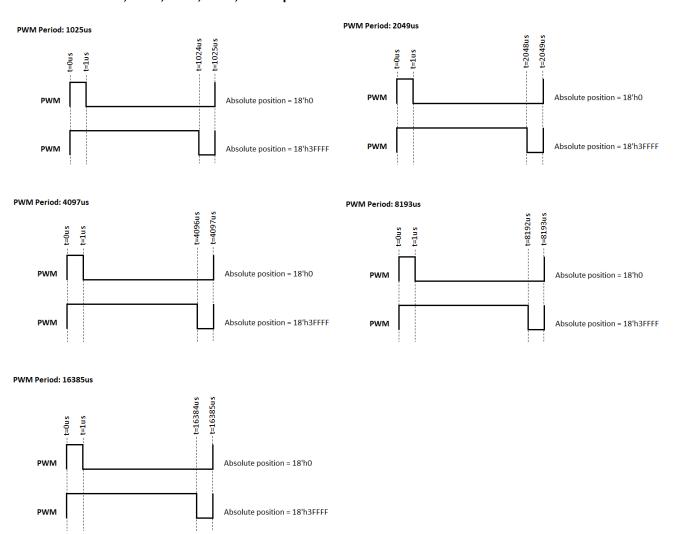

## **PWM**

The PWM protocol uses one output pin ( $W_PWM$ ) from the AEAT-9955. Note that the  $W_PWM$  pin is shared between the UVW and PWM protocols. The PWM signals are configurable to have a period of 1025, 2049, 4097, 8193, or 16385  $\mu$ s. During power-up, the PWM signal is 0 before chip ready.

PWM Signals (Period = 1025/2049/4097/8193/16385 μs)

PWM Period: 1025, 2049, 4097, 8193, 16385 μs

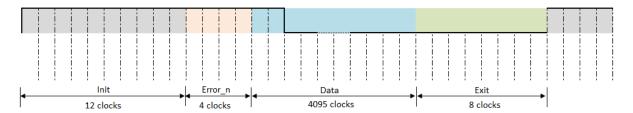

The PWM protocol is also available with Init, Error\_n, and Exit along with Data information.

#### PWM Signals (Period = 1047/2071/4119/8215/16407 μs)

PMW Period: 4119 µs

# **Incremental Output Format**

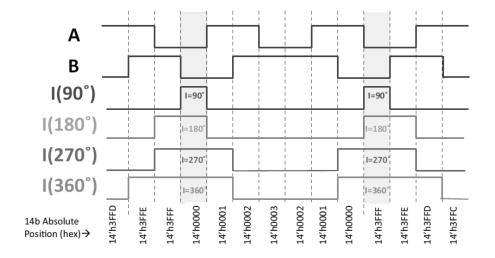

The AEAT-9955 provides ABI and UVW signals to indicate the incremental position of the motor.

### **ABI**

The ABI incremental interface is available to provide position data and direction data from the three output pins (A, B, and I).

The index signal marks the absolute angular position and typically occurs once per revolution. The ABI signal is configurable using the memory map registers. It supports the following configuration:

- Programmable CPR: 1 to 20,000 CPR

- Programmable I-width: 90, 180, 270, or 360 electrical degrees (°e)

- Programmable I-state: 90, 180, 270, or 360 electrical degrees (°e)

Figure 4: ABI Signal (4096 CPR, with Different I-Width Settings), Assuming the User Sets Hysteresis at 0.02 Mechanical Degrees

The index position is configurable among the incremental states.

The index signal rises high once per turn at the absolute zero position.

The number of indexes per revolutions is configurable from 1 pulse up to 128 pulses.

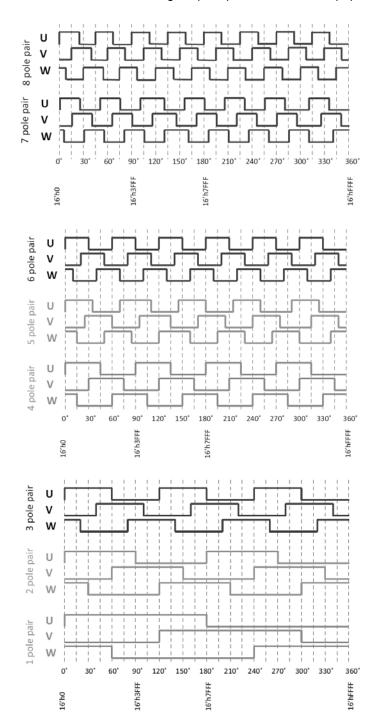

## **UVW**

Three-channel integrated commutation output (U, V, W) emulates Hall sensor feedback and is available using three output pins. Note that the W\_PWM pin is shared between the UVW and PWM protocols.

The AEAT-9955 can configure pole pairs from 1 to 32 (equivalent to 2 to 64 poles).

Note that signal U from the UVW protocol is tagged to signal I from the ABI protocol as shown in the following figure.

Figure 5: U-to-I Tagging

# Package Drawings (in mm)

Figure 6: AEAT-9955, 32 QFN Dimensions

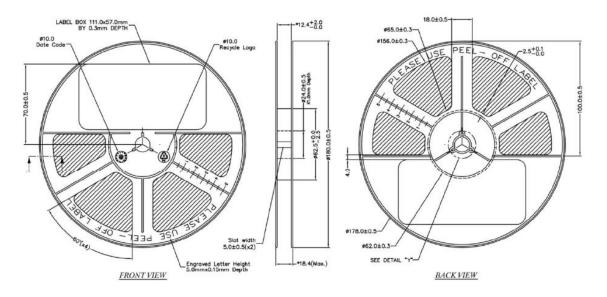

Figure 7: Reel Dimensions

# **Product Ordering Information**

| Ordering Part Number | Product Description                                 | Package                   | Delivery Form |

|----------------------|-----------------------------------------------------|---------------------------|---------------|

| AEAT-9955-100        | 18-Bits Magnetic Encoder On-Off Axis Tape Reel 1000 | QFN 32 leads, 5 mm × 5 mm | Tape and Reel |

| AEAT-9955-102        | 18-Bits Magnetic Encoder On-Off Axis Tape Reel 100  | QFN 32 leads, 5 mm × 5 mm | Tape and Reel |

| AEAT-9955-Q32        | 18-Bits Magnetic Encoder On-Off Axis                | QFN 32 leads, 5 mm × 5 mm | Tube          |

| Copyright © 2021–2023 Broadcom. All Rights Reserved. The term "Broadcom" refers to Broadcom Inc. and/or its subsidiaries. For more information, go to <a href="https://www.broadcom.com">www.broadcom.com</a> . All trademarks, trade names, service marks, and logos referenced herein belong to their respective companies.                                                                                                                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Broadcom reserves the right to make changes without further notice to any products or data herein to improve reliability, function, or design. Information furnished by Broadcom is believed to be accurate and reliable. However, Broadcom does not assume any liability arising out of the application or use of this information, nor the application or use of any product or circuit described herein, neither does it convey any license under its patent rights nor the rights of others. |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| <b>BROADCOM</b> °                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |