### **Application Note**

### **AEAT-9955**

# Magnetic Encoder IC: 10-Bit to 18-Bit Programmable Angular Magnetic Encoder with Safety

### **Description**

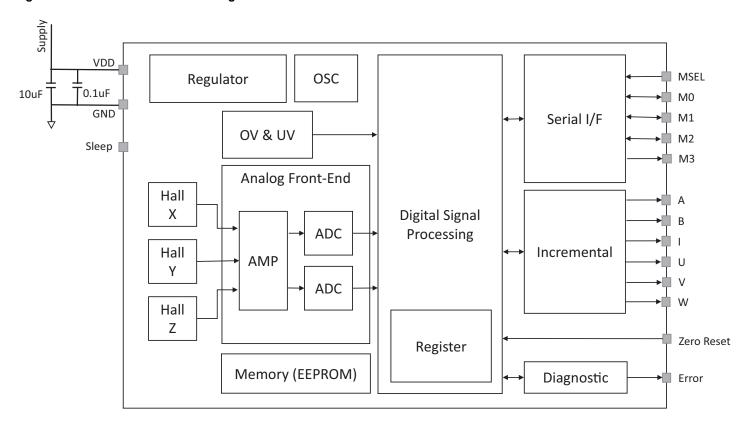

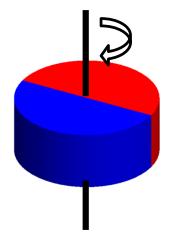

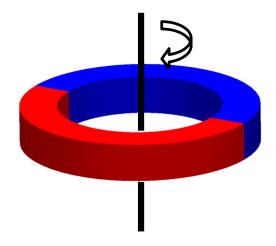

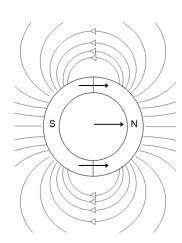

The Broadcom<sup>®</sup> AEAT-9955 is a CMOS magnetic sensor structure that is suitable for contactless 360° encoding based on the Hall effect. It provides an angle output up to 18 bits of resolution and simultaneous incremental output up to 20,000 CPR. An integrated Hall structure at the core of the device uses a single 2-pole disc or ring magnet to convert the magnetic field vector in the chip plane into an AC signal whose amplitude and phase correspond to the magnitude and direction of the field.

An internal digital-signal-processing unit then processes and conditions the raw AC signal from the sensor. The output signals are available in three different forms:

- Pulse-width modulation (PWM)

- Absolute 18-bit position through the 3-wire and 2-wire Synchronous Serial Interface (SSI) and the 4-wire Serial Protocol Interface (SPI)

- Incremental output (ABI and UVW signals)

These features can be programmed by configuring the internal registers in program mode.

More information about the AEAT-9955 product specifications is available in the product data sheet.

### **Operation Mode**

The AEAT-9955 features two types of operational modes: normal operation mode and configuration mode.

### **Normal Operation Mode**

Normal mode is the normal operating mode of the chip. The absolute output (10-bit to 18-bit absolute position data) is available through serial protocol pins (M0, M1, M2, and M3). The following are the output signal conditions during AEAT-9955 initialization:

- PWM signals all 0s

- ABI signals all 1s

- UVW signals all 0s

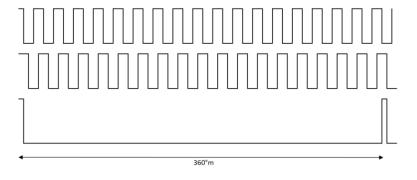

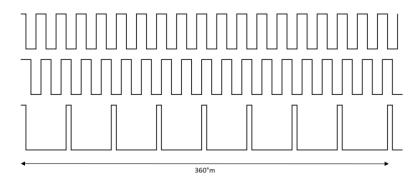

The incremental positions are indicated on ABI and UVW signals with a user-configurable CPR from 0 to 20,000 of ABI signals and pole pairs from 1 to 32 (2 to 64 poles) for UVW commutation signals.

# **Configuration Mode**

The AEAT-9955 has a built-in memory for multiple-time programming (MTP).

Programming of the AEAT-9955 can be performed with the HEDS-9955 programming kit or any tester/programmer device using the guidelines provided.

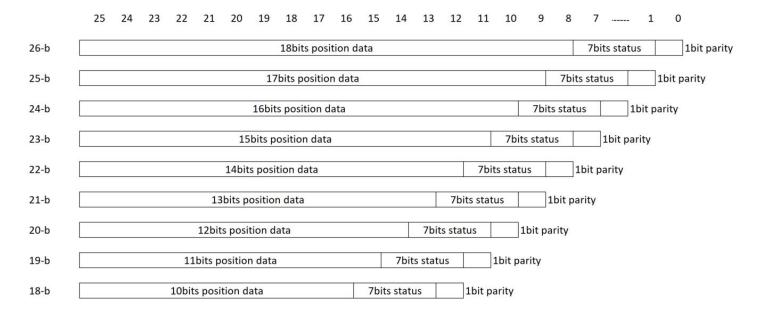

# Absolute and Incremental Programming

The absolute resolution can be set to 10, 11, 12, 13, 14, 15, 16, 17, or 18 bits. For incremental selection, ABI or UVW can be selected by following the instructions in the following sections. The PWM output is available as well.

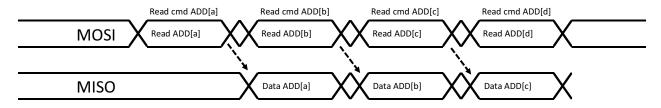

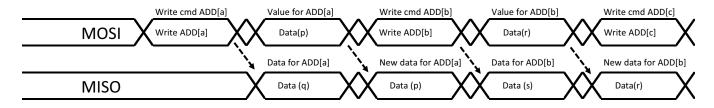

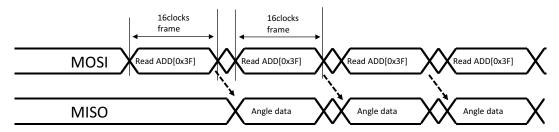

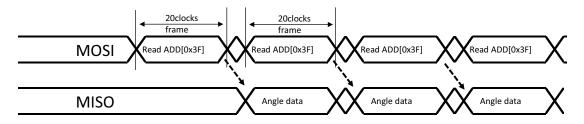

The shadow registers are programmable using the SPI protocol. Writing specific commands to specific addresses of the internal registers will program values of shadow registers to memory. The memory can be programmed multiple times.

### **Memory Map**

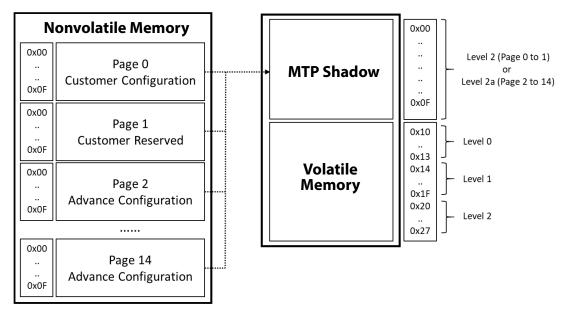

The AEAT-9955's memory consists of nonvolatile memory and volatile memory. The following figure illustrates the concept of nonvolatile memory, which is loaded into the MTP shadow.

Figure 1: Nonvolatile/Volatile Memory and MTP Shadow Block Diagram

MTP shadow registers are nonvolatile (upon power-up, the values are reloaded from EEPROM) and are not automatically written to EEPROM. To write MTP shadow register values to EEPROM (nonvolatile) memory, see EEPROM Programming. Additionally, EEPROM programming can be performed at a supply voltage of 3.3V or 5V. The MTP shadow registers are from address 0x00 to address 0x27. The following table lists the configurations of the volatile memory for address 0x20 to 0x2F.

**Table 1: Volatile Memory**

| Address      | Bit(s) | Name                    | Description                                                                        |

|--------------|--------|-------------------------|------------------------------------------------------------------------------------|

| 0x20 to 0x28 | N/A    | Factory Reserved        | Factory reserved.                                                                  |

| 0x29         | [7:0]  | Chip Status             | See Alarm.                                                                         |

|              | [7]    | Memory Busy             | Memory busy bit. 0: EEPROM programming completed 1: EEPROM programming in progress |

| 0.24         | [6]    | OTP Unlocked            | OTP unlocked status. 0: Locked 1: Unlocked                                         |

| 0x2A         | [3:2]  | Zero Reset Status       | Zero reset status. 10: Calibration pass 11: Calibration fail                       |

|              | [1:0]  | Auto Calibration Status | Calibration status. 10: Calibration pass 11: Calibration fail                      |

| 0x2B         | [7:0]  | Chip ID                 | Chip identification.                                                               |

| 0x2C to 0x2F | N/A    | Factory Reserved        | Factory reserved.                                                                  |

# **Customer Configuration Registers**

The following registers are available for users to store information and configure the encoder as required.

Table 2: Customer Reserved Registers (Page 1)

| Address | Bit(s) | Name                | Description       | Default |

|---------|--------|---------------------|-------------------|---------|

| 0x00    | [7:0]  | Customer Reserve 0  | User programmable | 8'h0    |

| 0x01    | [7:0]  | Customer Reserve 1  | User programmable | 8'h0    |

| 0x02    | [7:0]  | Customer Reserve 2  | User programmable | 8'h0    |

| 0x03    | [7:0]  | Customer Reserve 3  | User programmable | 8'h0    |

| 0x04    | [7:0]  | Customer Reserve 4  | User programmable | 8'h0    |

| 0x05    | [7:0]  | Customer Reserve 5  | User programmable | 8'h0    |

| 0x06    | [7:0]  | Customer Reserve 6  | User programmable | 8'h0    |

| 0x07    | [7:0]  | Customer Reserve 7  | User programmable | 8'h0    |

| 0x08    | [7:0]  | Customer Reserve 8  | User programmable | 8'h0    |

| 0x09    | [7:0]  | Customer Reserve 9  | User programmable | 8'h0    |

| 0x0A    | [7:0]  | Customer Reserve 10 | User programmable | 8'h0    |

| 0x0B    | [7:0]  | Customer Reserve 11 | User programmable | 8'h0    |

| 0x0C    | [7:0]  | Customer Reserve 12 | User programmable | 8'h0    |

| 0x0D    | [7:0]  | Customer Reserve 13 | User programmable | 8'h0    |

| 0x0E    | [7:0]  | Customer Reserve 14 | User programmable | 8'h0    |

| 0x0F    | [7:0]  | Customer Reserve 15 | User programmable | 8'h0    |

Table 3: Customer Configuration Registers (Page 0)

| Address | Bit(s) | Name           | Description                                                  | Default |

|---------|--------|----------------|--------------------------------------------------------------|---------|

|         |        |                | Enables the safety feature in the serial interface.          | 1       |

|         | [7]    | Safety Bit     | 1: Enable safety.                                            |         |

|         |        |                | 0: Disable safety.                                           |         |

|         |        |                | Selects the CRC type when the "Safety bit" = 1.              | 1       |

|         | [6]    | CRC Select     | 1: 16b CRC (CCITT False)                                     |         |

|         |        |                | 0: 8b CRC (SAE J1850)                                        |         |

|         |        |                | CRC initialize value when the "Safety bit" = 1.              | 11      |

| 0x00    |        |                | 00: 16'h0000 / 8'h00                                         |         |

|         | [5:4]  | CRC Initialize | 01: 16'h5555 / 8'h55                                         |         |

|         |        |                | 10: 16'hAAAA / 8'hAA                                         |         |

|         |        |                | 11: 16'hFFFF / 8'hFF                                         |         |

|         |        |                | Sequence Counter initialize value when the "Safety bit" = 1. | 0000    |

| 10.01   | [0.0]  | CC Initialina  | 0000: 1                                                      |         |

|         | [3:0]  | SC Initialize  | :                                                            |         |

|         |        |                | 1111: 16                                                     |         |

Table 3: Customer Configuration Registers (Page 0) (Continued)

| Address | Bit(s)             | Name                                      | Description                                                                                 | Default |

|---------|--------------------|-------------------------------------------|---------------------------------------------------------------------------------------------|---------|

| ]       |                    |                                           | Alarm report condition.                                                                     | 1       |

|         | [7]                | Alarm Latch                               | 1: Triggered alarm remains until user clears or power-cycles.                               |         |

|         |                    |                                           | 0: Triggered alarm resets once error recovered.                                             |         |

|         |                    |                                           | Enable high impedance mode.                                                                 | 1       |

|         | [6]                | SPI Output High-Z                         | 1: Disable high-z.                                                                          |         |

| [5]     |                    |                                           | 0: Enable high-z.                                                                           |         |

|         | [5]                | Reserved                                  | Reserved.                                                                                   | 0       |

|         |                    |                                           | Turn Off absolute position hysteresis.                                                      | 0       |

| [4]     | Aba Hyatarasia Off | 1: Turn Off absolute position hysteresis. |                                                                                             |         |

|         | [4]                | Abs. Hysteresis Off                       | 0: Do not turn Off absolute position hysteresis (follow the Level 2a setting).              |         |

|         |                    |                                           | Turn Off incremental output (ABI/UVW) safe state.                                           | 0       |

| 0x01    | [3]                | Inc. Safety Off                           | 1: Turn Off incremental output (ABI/UVW) safe state.                                        |         |

| OXO I   |                    |                                           | 0: Turn On incremental output (ABI/UVW) safe state.                                         |         |

|         |                    |                                           | Skip accuracy calibration during auto-calibration.                                          | 0       |

|         | [2]                | Accuracy Cal Skip                         | 1: Turn Off accuracy calibration during auto-calibration.                                   |         |

|         | [2]                |                                           | Do not turn Off accuracy calibration during auto-calibration (follow the Level 2a setting). |         |

|         |                    | Auto-calibration Hardware<br>Hold Time    | Time required to enable auto-calibration on the M1 pin.                                     | 0       |

|         | [1]                |                                           | 1: Auto-calibration started after holding M1 pin = 1 for 50 ms.                             |         |

|         |                    |                                           | 0: Auto-calibration started after holding M1 pin = 1 for 1 ms.                              |         |

|         |                    |                                           | Enable multiple use of auto-calibration on the M1 pin.                                      | 0       |

|         |                    | Multiple Auto-calibration                 | 1: Does not automatically clear auto-calibration hardware                                   |         |

|         | [0]                | Hardware                                  | (page 0, 0x06[7]) after auto-calibration using the M1 pin.                                  |         |

|         |                    |                                           | 0: Automatically clear auto-calibration hardware                                            |         |

|         |                    |                                           | (page 0, 0x06[7]) after auto-calibration using the M1 pin.                                  |         |

|         |                    |                                           | Magnetic field input high limit.                                                            | 1011    |

|         | [7:4]              | Magnetic High                             | 0000: 0 (lowest limit)                                                                      |         |

| 0x02    |                    |                                           | 1111: 15 (highest limit)                                                                    |         |

|         |                    |                                           | Magnetic field input low limit.                                                             | 0101    |

|         | [3:0]              | Magnetic Low                              | 0000: 0 (lowest limit)                                                                      |         |

|         |                    |                                           | 1111: 15 (highest limit)                                                                    |         |

Table 3: Customer Configuration Registers (Page 0) (Continued)

| Address | Bit(s) | Name                        | Description                                    |                      |                                                 | Default |

|---------|--------|-----------------------------|------------------------------------------------|----------------------|-------------------------------------------------|---------|

|         | [7:4]  | Filter Config1 (Level 1)    | [7:4] = Position                               | filter configuration | 1.                                              | 0000    |

|         |        |                             |                                                | •                    | nt on lag compensation value.                   | 0000    |

|         |        |                             | Recommend th                                   | ne following configu | uration set for a different filter.             |         |

|         |        |                             | Filter Value                                   | Filter Config1 [7:4] | Lag Compensation Adjustment [3:0] (Recommended) |         |

|         |        |                             | Follow Filter<br>Config2<br>(Level 2a)         | 0000                 | 0000                                            |         |

|         |        |                             | 163 µs                                         | 0001                 | 1000                                            |         |

|         |        |                             | 237 µs                                         | 0010                 | 1000                                            |         |

|         |        |                             | 491 μs                                         | 0010                 | 1000                                            |         |

|         |        |                             | 655 μs                                         | 0100                 | 1000                                            |         |

| )x03    | [3:0]  | Lag Compensation Adjustment | 984 μs                                         | 0101                 | 1000                                            |         |

|         |        |                             | 1.3 ms                                         | 0110                 | 1000                                            |         |

|         |        |                             | 1.6 ms                                         | 0111                 | 0111                                            |         |

|         |        |                             | 2.0 ms                                         | 1000                 | 0111                                            |         |

|         |        |                             | 2.0 ms                                         | 1000                 | 1010                                            |         |

|         |        |                             | 2.6 ms                                         | 1010                 | 1000                                            |         |

|         |        |                             | 3.3 ms                                         | 1010                 | 1101                                            |         |

|         |        |                             | 3.9 ms                                         | 1100                 | 1110                                            |         |

|         |        |                             | 4.6 ms                                         | 1101                 | 1100                                            |         |

|         |        |                             | 5.2 ms                                         | 1110                 | 1000                                            |         |

|         |        |                             | 6.6 ms                                         | 1111                 | 1111                                            |         |

| )x04    | [7.0]  | Decembed                    |                                                | 1111                 |                                                 | 0       |

| XU4     | [7:0]  | Reserved                    | Reserved                                       | avec per revelution  |                                                 | 000     |

|         |        |                             | Number of indexes per revolution. 000: 1 pulse |                      |                                                 | 000     |

|         |        |                             | 001: 2 pulses                                  |                      |                                                 |         |

|         |        |                             | 010: 4 pulses                                  |                      |                                                 |         |

|         | [7:5]  | Multi-Index                 | 011: 8 pulses                                  |                      |                                                 |         |

|         | []     |                             | 100: 16 pulses                                 |                      |                                                 |         |

|         |        |                             | 101: 32 pulses                                 |                      |                                                 |         |

|         |        |                             | 110: 64 pulses                                 |                      |                                                 |         |

| )x05    |        |                             | 111: 128 pulses                                | S                    |                                                 |         |

|         | [4]    | Reserved                    | Reserved.                                      |                      |                                                 | 00000   |

|         |        |                             | Configuration f                                | or acceleration/dec  | celeration response.                            | 00      |

|         |        |                             | 00: Basic                                      |                      |                                                 |         |

|         | [3:2]  | Acceleration Configuration  | 01: Moderately aggressive                      |                      |                                                 |         |

|         |        |                             | 10: Highly aggressive                          |                      |                                                 |         |

|         |        |                             | 11: Basic                                      |                      |                                                 |         |

|         | [1:0]  | Reserved                    | Reserved.                                      |                      |                                                 | 0       |

Table 3: Customer Configuration Registers (Page 0) (Continued)

| Address | Bit(s) | Name                                 | Description                                 | Default |

|---------|--------|--------------------------------------|---------------------------------------------|---------|

|         |        |                                      | Enables auto-calibration on the M1 pin.     | 0       |

| ]       | [7]    | Auto-calibration Hardware            | 0: Disable calibration.                     |         |

|         |        |                                      | 1: Enable calibration.                      |         |

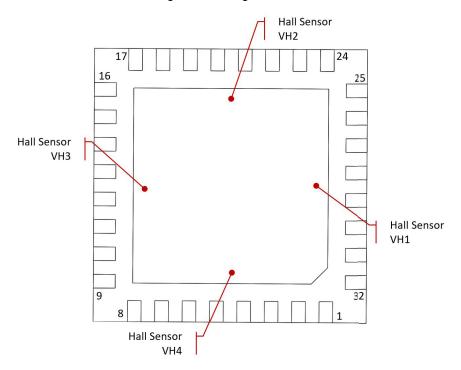

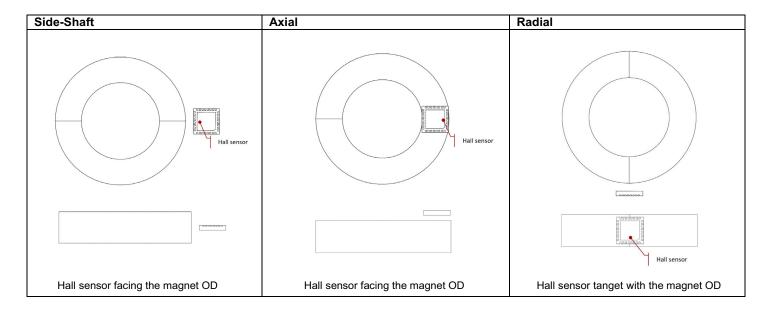

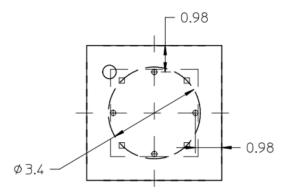

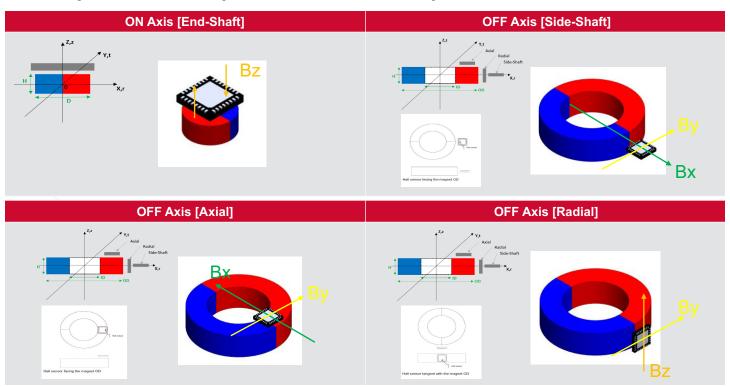

|         |        |                                      | Sensing axis configuration selection.       | 000     |

|         |        |                                      | 000: On-Axis                                |         |

|         | [6:4]  | Sensing Axis                         | 101: Off-Axis (radial)                      |         |

| 0x06    |        |                                      | 110: Off-Axis (axial)                       |         |

| UXUO    |        |                                      | 111: Off-Axis (side shaft)                  |         |

|         |        |                                      | Vertical Hall selection (off-axis only).    | 0000    |

|         |        |                                      | 1000: VH#1                                  |         |

|         | [2.0]  | Vertical Hall Selection <sup>a</sup> | 0100: VH#2                                  |         |

|         | [3:0]  |                                      | 0010: VH#3                                  |         |

|         |        |                                      | 0001: VH#4                                  |         |

|         |        |                                      | Other 4-bit combination values are invalid. |         |

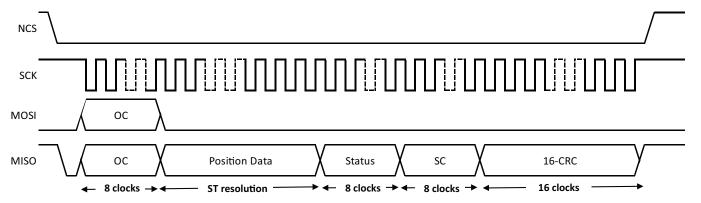

|         |        |                                      | SPI4 mode selection (per the MATS Table).   | 00      |

|         |        | SPI4 Mode                            | 00: SPI4-16 (16-bit parity)                 |         |

|         | [7:6]  |                                      | 01: SPI4-24a (24-bit parallel CRC)          |         |

|         |        |                                      | 10: SPI4-24b (24-bit serial CRC)            |         |

|         |        |                                      | 11: SPI4-8 (8-bit safety)                   |         |

|         |        |                                      | Commutation output pole-pair selection.     | 000011  |

| 0x07    |        |                                      | 000000: 0 pole pairs / OFF                  |         |

|         |        |                                      | 000001: 1 pole pair                         |         |

|         | [5:0]  | LDAM December                        | :                                           |         |

|         | [5.0]  | 0] UVW Resolution <sup>b</sup>       | 011111: 31 pole pairs                       |         |

|         |        |                                      | 100000: 32 pole pairs                       |         |

|         |        |                                      | 100001: 32 pole pairs                       |         |

|         |        |                                      | * Out-of-range limit to 32 pole pairs.      |         |

Table 3: Customer Configuration Registers (Page 0) (Continued)

| Address | Bit(s) | Name                                       | Description                                          | Default  |

|---------|--------|--------------------------------------------|------------------------------------------------------|----------|

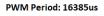

|         |        |                                            | 0000: PWM fixed period = 10 bits                     | 0000     |

|         |        |                                            | 0001: PWM fixed period = 11 bits                     |          |

|         |        | 0010: PWM fixed period = 12 bits           |                                                      |          |

|         |        |                                            | 0011: PWM fixed period = 13 bits                     |          |

|         |        |                                            | 0100: PWM fixed period = 14 bits                     |          |

|         | [7, 4] | Divini D                                   | *0101-0111: Out of range, PWM fixed period = 14 bits |          |

|         | [7:4]  | PWM Resolution <sup>b</sup>                | 1000: PWM fixed clock = 10 bits                      |          |

|         |        |                                            | 1001: PWM fixed clock = 11 bits                      |          |

|         |        |                                            | 1010: PWM fixed clock = 12 bits                      |          |

|         |        |                                            | 1011: PWM fixed clock = 13 bits                      |          |

|         |        |                                            | 1100: PWM fixed clock = 14 bits                      |          |

| 80x0    |        |                                            | *1101-1111: Out of range, PWM fixed clock = 14 bits  |          |

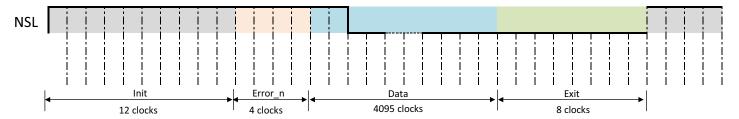

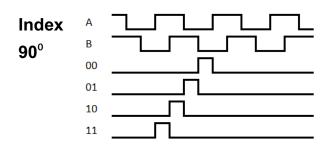

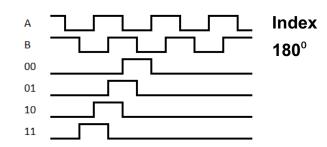

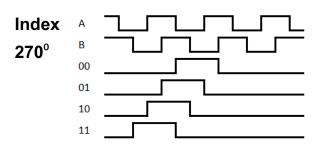

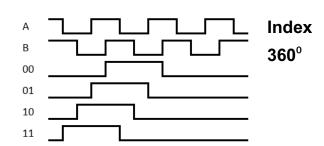

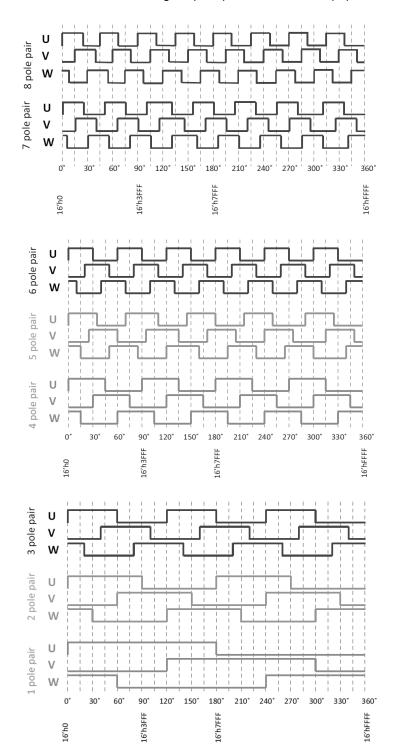

|         |        |                                            | Index width selection.                               | 00       |

|         |        |                                            | 00: 90e°                                             |          |

|         | [3:2]  | Index Width                                | 01: 180e°                                            |          |

|         | -      |                                            | 10: 270e°                                            |          |

|         |        |                                            | 11: 360e°                                            |          |

|         |        |                                            | Index location within incremental period selection.  | 00       |

|         |        | Index State                                | 00: A low B low                                      |          |

|         | [1:0]  |                                            | 01: A low B high                                     |          |

|         |        |                                            | 10: A high B high                                    |          |

|         |        |                                            | 11: A high B low                                     |          |

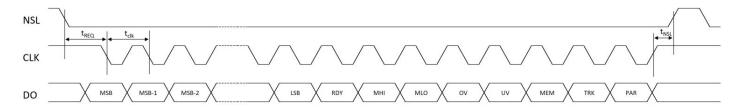

|         |        |                                            | Protocol mode selection with the MATS Table.         | 0        |

|         | [7]    | PSEL <sup>c</sup>                          | 0: SSI3a / SSI2a / All SPI4 modes                    |          |

| 0x09    |        | . 522                                      | 1: SSI3b / SSI2b / PWM                               |          |

|         | [6:0]  | Incremental Resolution [14:8] <sup>d</sup> | Incremental resolution selection.                    | 0000100  |

|         |        |                                            | 000-0000-0000-0000: 0 CPR (OFF)                      | 00000000 |

|         |        |                                            | 000-0000-0000-0001: 1 CPR                            |          |

|         |        |                                            | 000-0000-0000-0010: 2 CPR                            |          |

|         |        |                                            | 000-0000-0000-0011: 3 CPR                            |          |

| 0x0A    | [7:0]  | Incremental Resolution [7:0] <sup>d</sup>  | 000-0000-1000-0000: 128 CPR                          |          |

|         | []     | moremental resolution [1.0]                | :<br>000-0100-0000-0000: 1024 CPR                    |          |

| Ì       |        |                                            | :<br>010-0000-0000-0000: 8192 CPR                    |          |

|         |        |                                            | :<br>100-1110-0010-0000: 20,000 CPR                  |          |

Table 3: Customer Configuration Registers (Page 0) (Continued)

| Address | Bit(s) | Name                   | Description                                 | Default |

|---------|--------|------------------------|---------------------------------------------|---------|

|         |        |                        | Incremental output hysteresis selection.    | 100     |

|         |        |                        | 000: Hysteresis OFF                         |         |

|         |        |                        | 001: 0.01m°                                 |         |

|         |        |                        | 010: 0.02m°                                 |         |

|         | [7:5]  | Hysteresis             | 011: 0.04m°                                 |         |

|         |        |                        | 100: 0.08m°                                 |         |

|         |        |                        | 101: 0.17m°                                 |         |

|         |        |                        | 110: 0.35m°                                 |         |

| 000     |        |                        | 111: 0.70m°                                 |         |

| 0x0B    |        | Direction              | Counting direction selection.               | 0       |

|         | [4]    |                        | 0: Count up in clockwise direction.         |         |

|         |        |                        | 1: Count up in counter-clockwise direction. |         |

|         |        | N 0: 1 7 5 1 :         | Absolute output resolution selection.       | 0000    |

|         |        |                        | 0000: 18 bits                               |         |

| [2.0]   | [0.0]  |                        | 0001: 17 bits                               |         |

|         | [3:0]  | Single Turn Resolution | :                                           |         |

|         |        |                        | 1000: 10 bits                               |         |

|         |        |                        | * Out-of-range limit to 8-bit minimum.      |         |

- a. See Off-Axis Sensing Orientation.

- UVW: Flexible 6-bit UVW resolution up to 32 pole pairs.

PWM: Only the shown setting is available; other combinations are invalid.

- c. In conjunction with the MATS Table for input/output configuration.

- d. Flexible 15-bit Incremental resolution up to 20,000 CPR. Combinations above 20,000 are invalid.

### Table 4: Customer Single-Turn Reset (Page 0)

| Address | Bit(s) | Name         | Description                                   | Default   |

|---------|--------|--------------|-----------------------------------------------|-----------|

| 0x0C    | [7:0]  | Zero Reset 2 | MSB bit-17 to bit-10 of absolute single-turn. | 0000-0000 |

| 0x0D    | [7:0]  | Zero Reset 1 | Bit-9 to bit-2 of absolute single-turn.       | 0000-0000 |

| 0x0E    | [7:6]  | Zero Reset 0 | LSB bit-1 to bit-0 of absolute single-turn.   | 00        |

Table 5: Advance Configuration (Page 2/5/8/11)

| Address | Bit(s) | Name                     | Description                                                                                                                  | Default                      |

|---------|--------|--------------------------|------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| 0x00    | [7:0]  | Sin Static Gain [15:8]   | Digital static gain multiplier value for sin/cos inputs, calculated using                                                    | 0x00                         |

| 0x01    | [7:0]  | Sin Static Gain [7:0]    | auto-calibration; to adjust digital sin/cos VPP to 1.8V equivalent.                                                          | 0x00                         |

| 0x02    | [7:0]  | Cos Static Gain [15:8]   | 0x0000 = 100% (exception)                                                                                                    | 0x00                         |

| 0x03    | [7:0]  | Cos Static Gain [7:0]    | 0x0001 = ~0% : 0x4000 = 100% : 0xFFFF = 400%                                                                                 | 0x00                         |

| 0x04    | [7:0]  | Sin Static Offset [15:8] | Digital static offset value for sin/cos, calculated using auto-                                                              | 0x00                         |

| 0x05    | [7:0]  | Sin Static Offset [7:0]  | calibration; to adjust digital sin/cos Vmid to 1.0V equivalent.                                                              | 0x00                         |

| 0x06    | [7:0]  | Cos Static Offset [15:8] | 0x8000 = -1.0V                                                                                                               | 0x00                         |

| 0x07    | [7:0]  | Cos Static Offset [7:0]  | :<br>0x0000 = 0.0V<br>:<br>0x7FFF = 1.0V                                                                                     | 0x00                         |

| 0.00    | [7:4]  | Sin Raw Gain             | Analog raw gain configuration for sin.                                                                                       | 0000                         |

| 80x0    | [3:0]  | Cos Raw Gain             | Analog raw gain configuration for cos.                                                                                       | 0000                         |

|         | [7:4]  | Reserved                 | Reserved.                                                                                                                    | 0000                         |

| 0x09    | [3:0]  | Hall Bias                | Hall sensor bias current configuration.                                                                                      | Page 2: 1110<br>Others: 1101 |

| 0x0A    | [7:0]  | Reserved                 | Reserved.                                                                                                                    | 0x00                         |

| 0x0B    | [7:0]  | Reserved                 | Reserved.                                                                                                                    | 0x00                         |

| 0x0C    | [7:0]  | Cos Static Phase [15:8]  | Digital static phase value for cos (w.r.t sin), calculated using auto-                                                       | 0x00                         |

| 0x0D    | [7:0]  | Cos Static Phase [7:0]   | calibration; to maintain Cos/Sin phase delta per calibrated result.  0x0000 = 0 deg  :  0x4000 = 90 deg  :  0xFFFF = 360 deg | 0x00                         |

| 0x0E    | [7:0]  | Reserved                 | Reserved.                                                                                                                    | 0x00                         |

Table 6: Advance Configuration (Page 3/6/9/12)

| Address | Bit(s) | Name                   | Description                                                                   | Default    |

|---------|--------|------------------------|-------------------------------------------------------------------------------|------------|

| 0x00    | [7:0]  | ADC Configuration      | Fixed ADC configuration.                                                      | 0x08       |

|         |        |                        | Enable dynamic offset correction.                                             | 1          |

| 0x01    | [7]    | Dynamic Offset Enable  | 1: Enable dynamic offset correction.                                          |            |

| UXUT    |        |                        | 0: Disable dynamic offset correction.                                         |            |

|         | [6:0]  | Fixed Configuration    | Fixed test configuration.                                                     | 0000000    |

|         |        |                        | Enable dynamic gain correction.                                               | 1          |

|         | [7]    | Dynamic Gain Enable    | 1: Enable dynamic gain correction.                                            |            |

|         |        |                        | 0: Disable dynamic gain correction.                                           |            |

|         |        |                        | Phase measure configuration.                                                  | Page 3: 00 |

| 0x02    |        |                        | 00: No phase measurement.                                                     | Others: 10 |

|         | [6:5]  | Phase Measure          | 01: Phase measurement always ON.                                              |            |

|         | [0.0]  | Configuration (dft_en) | 10: Phase measurement ON after Offset/Gain values stable.                     |            |

|         |        |                        | 11: Phase measurement ON after 10 iterations of Offset/Gain value evaluation. |            |

|         |        |                        | Enable dynamic phase correction.                                              | Page 3: 0  |

|         | [7]    | ] Dynamic Phase Enable | 1: Enable dynamic phase correction.                                           | Others: 1  |

|         |        |                        | 0: Disable dynamic phase correction.                                          |            |

| 0x03    |        |                        | Phase hysteresis for phase correction.                                        | Page 3: 00 |

| 0.000   | [6:5]  |                        | 00: 0.04 deg                                                                  | Others: 01 |

|         |        | [6:5] Phase Hysteresis | 01: 0.08 deg                                                                  |            |

|         |        |                        | 10: 0.17 deg                                                                  |            |

|         |        |                        | 11: 0.34 deg                                                                  |            |

| 0x04    | [7:0]  | Fixed Configuration    | Fixed test configuration.                                                     | 0x55       |

|         | [7]    | Fixed Configuration    | Fixed configuration.                                                          | 0          |

|         | [6:4]  | doc_st_delta           | Dynamic offset stabilizer configuration.                                      | 001        |

|         |        |                        | Acceptance range to consider as "stable" offset.                              |            |

|         |        |                        | Higher = Lower sensitivity.                                                   |            |

|         | [3:2]  | doc_st_step            | Dynamic offset stabilizer configuration.                                      | 11         |

|         |        |                        | Rate of switching of Stabilizer state.                                        |            |

| 0x05    |        |                        | 00: No change of Stabilizer state upon power-up.                              |            |

| OXOO    |        |                        | Higher = Higher sensitivity.                                                  |            |

|         | [1:0]  | doc_st_init            | Dynamic offset stabilizer configuration.                                      | 11         |

|         |        |                        | State of stabilizer at power-up.                                              |            |

|         |        |                        | 00: Very unstable (high sensitivity).                                         |            |

|         |        |                        | 01: Slightly unstable (middle sensitivity).                                   |            |

|         |        |                        | 10: Slightly stable (middle sensitivity).                                     |            |

|         |        |                        | 11: Very stable (low sensitivity).                                            |            |

Table 6: Advance Configuration (Page 3/6/9/12) (Continued)

| Address | Bit(s) | Name                       | Description                                      | Default |

|---------|--------|----------------------------|--------------------------------------------------|---------|

|         | [7]    | Fixed Configuration        | Fixed configuration.                             | 0       |

|         | [6:4]  | dgc_st_delta               | Dynamic gain stabilizer configuration.           | 001     |

|         |        |                            | Acceptance range to consider as "stable" gain.   |         |

|         |        |                            | Higher = Lower sensitivity.                      |         |

|         | [3:2]  | dgc_st_step                | Dynamic gain stabilizer configuration.           | 11      |

|         |        |                            | Rate of switching of Stabilizer state.           |         |

| )x06    |        |                            | 00: No change of Stabilizer state upon power-up. |         |

| 7,00    |        |                            | Higher = Higher sensitivity.                     |         |

|         | [1:0]  | dgc_st_init                | Dynamic gain stabilizer configuration.           | 11      |

|         |        |                            | State of stabilizer at power-up.                 |         |

|         |        |                            | 00: Very unstable (high sensitivity).            |         |

|         |        |                            | 01: Slightly unstable (middle sensitivity).      |         |

|         |        |                            | 10: Slightly stable (middle sensitivity).        |         |

|         |        |                            | 11: Very stable (low sensitivity).               |         |

|         | [7]    | <b>Fixed Configuration</b> | Fixed configuration.                             | 0       |

|         | [6:4]  | dpc_st_delta               | Dynamic phase stabilizer configuration.          | 001     |

|         |        |                            | Acceptance range to consider as "stable" phase.  |         |

|         |        |                            | Higher = Lower sensitivity.                      |         |

|         | [3:2]  | dpc_st_step                | Dynamic phase stabilizer configuration.          | 11      |

|         |        |                            | Rate of switching of Stabilizer state.           |         |

| )x07    |        |                            | 00: No change of Stabilizer state upon power-up. |         |

| 7,01    |        |                            | Higher = Higher sensitivity.                     |         |

|         | [1:0]  | dpc_st_init                | Dynamic phase stabilizer configuration.          | 11      |

|         |        |                            | State of stabilizer at power-up.                 |         |

|         |        |                            | 00: Very unstable (high sensitivity).            |         |

|         |        |                            | 01: Slightly unstable (middle sensitivity).      |         |

|         |        |                            | 10: Slightly stable (middle sensitivity).        |         |

|         |        |                            | 11: Very stable (low sensitivity).               |         |

Table 6: Advance Configuration (Page 3/6/9/12) (Continued)

| Address    | Bit(s) | Name                      | Description                                                                  |       |  |  |  |  |

|------------|--------|---------------------------|------------------------------------------------------------------------------|-------|--|--|--|--|

|            |        |                           | Position filter configuration.                                               | 0000  |  |  |  |  |

|            |        |                           | 0000: Dynamic Filter                                                         |       |  |  |  |  |

|            |        |                           | 0001: 163 μs                                                                 |       |  |  |  |  |

|            |        |                           | 0010: 237 μs                                                                 |       |  |  |  |  |

|            |        |                           | 0011: 491 μs                                                                 |       |  |  |  |  |

|            |        |                           | 0100: 655 μs                                                                 |       |  |  |  |  |

|            |        |                           | 0101: 984 µs                                                                 |       |  |  |  |  |

|            |        |                           | 0110: 1.3 ms                                                                 |       |  |  |  |  |

| x08        | [7:4]  | Filter Config2 (Level 2a) | 0111: 1.6 ms                                                                 |       |  |  |  |  |

| X00        |        |                           | 1000: 2.0 ms                                                                 |       |  |  |  |  |

|            |        |                           | 1001: 2.3 ms                                                                 |       |  |  |  |  |

|            |        |                           | 1010: 2.6 ms                                                                 |       |  |  |  |  |

|            |        |                           | 1011: 3.3 ms                                                                 |       |  |  |  |  |

|            |        |                           | 1100: 3.9 ms                                                                 |       |  |  |  |  |

|            |        |                           | 1101: 4.6 ms                                                                 |       |  |  |  |  |

|            |        |                           | 1110: 5.2 ms                                                                 |       |  |  |  |  |

|            |        |                           | 1111: 6.6 ms                                                                 |       |  |  |  |  |

|            | [3:0]  | Fixed Configuration       | Fixed test configuration.                                                    | 1011  |  |  |  |  |

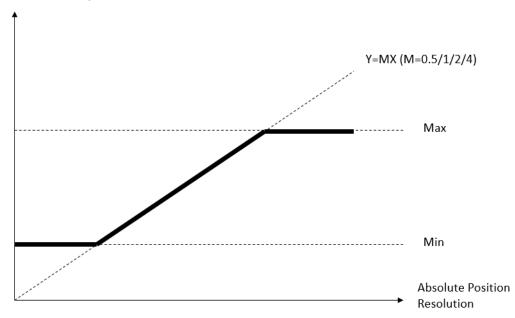

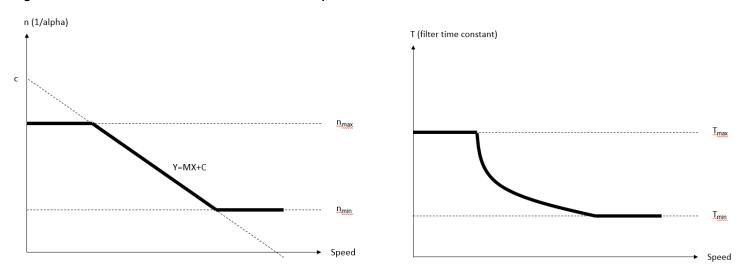

| )x09       | [7:4]  | Dyn. Filter Slope         | Configuration for Dynamic Filter.                                            | 0101  |  |  |  |  |

| X03        | [3:0]  | Dyn. Filter Y-intercept   | See Dynamic and Static Filter Function for further explanation.              | 0011  |  |  |  |  |

| x0A        | [7:4]  | Dyn. Filter Max           |                                                                              | 0001  |  |  |  |  |

| XUA        | [3:0]  | Dyn. Filter Min           |                                                                              | 0110  |  |  |  |  |

| · · · O.D. | [7:3]  | Reserved                  |                                                                              | 00000 |  |  |  |  |

| x0B        | [2:0]  | Dyn. Filter Hysteresis    |                                                                              | 011   |  |  |  |  |

|            | [7]    | Reserved                  | Reserved.                                                                    | 0     |  |  |  |  |

|            | [6]    | Acceleration Algorithm    | 1 to enable the acceleration algorithm.                                      | 1     |  |  |  |  |

|            | [5]    | Stop Algorithm            | 1 to enable the break algorithm.                                             | 0     |  |  |  |  |

| x0C        | [4]    | Deceleration Algorithm    | 1 to enable the deceleration algorithm.                                      | 1     |  |  |  |  |

|            | [3]    | Speed interpolation       | 1 to enable speed info interpolation.                                        | 1     |  |  |  |  |

|            | [2:0]  |                           | 19b configuration for filter compensation.                                   | 0x7   |  |  |  |  |

| )x0D       | [7:0]  |                           | 0x78C5C: Default, optimize for constant speed application.                   | 0x8C  |  |  |  |  |

| x0E        | [7:0]  | Filter Compensation       | 0x58C50: Optimize for high acceleration/deceleration application.            | 0x5C  |  |  |  |  |

| //\UL      | [7.0]  | ·                         | 0x58C4C: Balance between constant speed and high acceleration/ deceleration. | 0.00  |  |  |  |  |

### Table 7: Advance Configuration (Page 4/7/10/13)

| Address | Bit(s) | Name                                           | Description                                                          | Default       |  |  |  |

|---------|--------|------------------------------------------------|----------------------------------------------------------------------|---------------|--|--|--|

| 0x00    | [7:0]  | Fixed Configuration                            | Fixed configuration.                                                 | Page 13: 0x80 |  |  |  |

|         |        |                                                |                                                                      | Others: 0xE6  |  |  |  |

| 0x01    | [7:0]  | Fixed Configuration                            | Fixed configuration.                                                 | 0x80          |  |  |  |

| 0x02    | [7:0]  | Fixed Configuration                            | Fixed configuration.                                                 | 0x44          |  |  |  |

| 0x03    | [7:0]  | [7:0] Fixed Configuration Fixed configuration. |                                                                      |               |  |  |  |

|         | [7:6]  | Fixed Configuration                            | Fixed configuration.                                                 | 01            |  |  |  |

|         | [5:4]  | Accuracy Calibration                           | 00: Perform accuracy calibration as part of auto-calibration.        | 00            |  |  |  |

|         |        | Enable                                         | 11: Do not perform accuracy calibration as part of auto-calibration. |               |  |  |  |

|         |        |                                                | Etc: Invalid.                                                        |               |  |  |  |

|         | [3:2]  | Raw Gain Calibration                           | 10: Perform raw gain calibration as part of auto-calibration.        | 10            |  |  |  |

| 0x04    |        | Enable                                         | 11: Do not perform raw gain calibration as part of auto-calibration. |               |  |  |  |

|         |        |                                                | Etc: Invalid.                                                        |               |  |  |  |

|         | [1]    | Gain Calibration Enable                        | 0: Perform digital gain calibration.                                 | 0             |  |  |  |

|         |        |                                                | 1: Do not perform digital gain calibration.                          |               |  |  |  |

|         | [0]    | Offset Calibration Enable                      | 0: Perform digital offset calibration.                               | 0             |  |  |  |

|         |        |                                                | 1: Do not perform digital offset calibration.                        |               |  |  |  |

| 0x05    | [7:0]  | Fixed Configuration                            | Fixed configuration.                                                 | 0x25          |  |  |  |

| 0x06    | [7:0]  | Fixed Configuration                            | Fixed configuration.                                                 | 0x73          |  |  |  |

| 0x07    | [7:0]  | Fixed Configuration                            | Fixed configuration.                                                 | Page 4: 0x88  |  |  |  |

|         |        |                                                |                                                                      | Others: 0x80  |  |  |  |

Table 7: Advance Configuration (Page 4/7/10/13) (Continued)

| Address | Bit(s) | Default                         |                                                                  |                |

|---------|--------|---------------------------------|------------------------------------------------------------------|----------------|

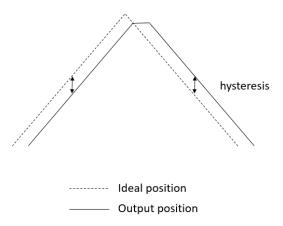

|         |        |                                 | Configuration for absolute position hysteresis.                  | 110            |

|         |        |                                 | 000: hys2_max = 0.02 deg                                         |                |

|         |        |                                 | 001: hys2_max = 0.04 deg                                         |                |

|         |        |                                 | 010: hys2_max = 0.08 deg                                         |                |

|         | [7.5]  | Absolute Pos. Hysteresis        | 011: hys2_max = 0.17 deg                                         |                |

|         | [7:5]  | Max                             | 100: hys2_max = 0.35 deg                                         |                |

|         |        |                                 | 101: hys2_max = 0.70 deg                                         |                |

|         |        |                                 | 110: hys2_max = 1.4 deg                                          |                |

|         |        |                                 | 111: Turn OFF absolute position hysteresis                       |                |

|         |        |                                 | See Position Data Hysteresis for further explanation.            |                |

|         |        |                                 | Configuration for absolute position hysteresis.                  | Page 4: 110    |

|         |        |                                 | 000: hys2_min = 0 deg                                            | Others: 111    |

| 0x08    |        |                                 | 001: hys2_min = 0.003 deg                                        |                |

| UXUO    |        |                                 | 010: hys2_min = 0.005 deg                                        |                |

|         | [4:2]  | Absolute Pos. Hysteresis<br>Min | 011: hys2_min = 0.011 deg                                        |                |

|         | [4.2]  |                                 | 100: hys2_min = 0.022 deg                                        |                |

|         |        |                                 | 101: hys2_min = 0.044 deg                                        |                |

|         |        |                                 | 110: hys2_min = 0.088 deg                                        |                |

|         |        |                                 | 111: hys2_min = 0.176 deg                                        |                |

|         |        |                                 | See Position Data Hysteresis for further explanation.            |                |

|         |        |                                 | Configuration for absolute position hysteresis.                  | 00             |

|         |        |                                 | 00: hys2_cfg = 0.5                                               |                |

|         | [1:0]  | Absolute Pos. Hysteresis        | 01: hys2_cfg = 1                                                 |                |

|         | [1.0]  | Configuration                   | 10: hys2_cfg = 2                                                 |                |

|         |        |                                 | 11: hys2_cfg = 4                                                 |                |

|         |        |                                 | See Position Data Hysteresis for further explanation.            |                |

| 0x09    | [7:0]  | Filter Compensation             | Decimal 0 – 1023 for the lag compensation calculation. Each step | Page 4: 0x02BC |

| 0x0A    | [7:0]  | Factor                          | increases/reduces the compensation equivalent to 80 ns.          | Others: 0x0443 |

| 0x0B    | [7:0]  | Reserved                        | Reserved.                                                        | 0x00           |

| 0x0C    | [7:0]  | Fixed Configuration             | Fixed configuration.                                             | 0x04           |

| 0x0D    | [7:0]  | Fixed Configuration             | Fixed configuration.                                             | 0x06           |

| 0x0E    | [7:0]  | Fixed Configuration             | Fixed configuration.                                             | 0x0A           |

Table 8: Advance Configuration (Page 14)

| Address | Bit(s) | Name                         | Description                                                                                                                                                                 | Default |

|---------|--------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 0x00    | [7:0]  | Fixed Configuration          | Fixed configuration.                                                                                                                                                        | 0x00    |

| )x01    | [7:0]  | Fixed Configuration          | Fixed configuration.                                                                                                                                                        | 0x00    |

| x02     | [7:0]  | Debug                        | Set to 0x80 to read out sin/cos information.                                                                                                                                | 0x00    |

| )x03    | [7:0]  | Fixed Configuration          | Fixed configuration.                                                                                                                                                        | 0x00    |

|         | [7:5]  | Fixed Configuration          | Fixed configuration.                                                                                                                                                        | 111     |

|         | [4]    | Filter Enable                | 0: Disable filter. 1: Enable filter.                                                                                                                                        | 1       |

|         | [3]    | Filter Compensation Enable   | Disable filter compensation.     Enable filter compensation.                                                                                                                | 1       |

| )x04    | [2]    | <b>Fixed Configuration</b>   | Fixed configuration.                                                                                                                                                        | 0       |

|         | [1]    | Dynamic Correction (dc_clip) | <ul><li>0: Allow abrupt change on dynamic offset/gain/phase correction values.</li><li>1: Limit to gradual change on dynamic offset/gain/phase correction values.</li></ul> | 1       |

|         | [0]    | Fixed Configuration          | Fixed configuration.                                                                                                                                                        | 1       |

|         | [7]    | Accuracy Correction Enable   | Disable accuracy correction.     Enable accuracy correction.                                                                                                                | 1       |

|         | [6:5]  | Forced Test Enable           | When Safety feature enabled (Page 0, address 0x00 [bit 7] = 1). 00: Disable power-up auto alarm check.  11: Enable power-up auto alarm check.                               | 11      |

|         | [4]    | ST Error Enable              | 0: Disable ST error. 1: Enable ST error.                                                                                                                                    | 1       |

| 0x05    | [3]    | MHI Error Enable             | 0: Disable MHI error. 1: Enable MHI error.                                                                                                                                  | 1       |

|         | [2]    | MLO Error Enable             | 0: Disable MLO error. 1: Enable MLO error.                                                                                                                                  | 1       |

|         | [1]    | OV Error Enable              | 0: Disable OV error. 1: Enable OV error.                                                                                                                                    | 1       |

|         | [0]    | UV Error Enable              | 0: Disable UV error. 1: Enable UV error.                                                                                                                                    | 1       |

| )x06    | [7:0]  | Fixed Configuration          | Fixed configuration.                                                                                                                                                        | 0x00    |

| )x07    | [7:0]  | Fixed Configuration          | Fixed configuration.                                                                                                                                                        | 0x00    |

| )x08    | [7:0]  | Fixed Configuration          | Fixed configuration.                                                                                                                                                        | 0x00    |

| )x09    | [7:0]  | Fixed Configuration          | Fixed configuration.                                                                                                                                                        | 0x00    |

| )x0A    | [7:0]  | Fixed Configuration          | Fixed configuration.                                                                                                                                                        | 0x00    |

| )x0B    | [7:0]  | Fixed Configuration          | Fixed configuration.                                                                                                                                                        | 0x00    |

| )x0C    | [7:0]  | Fixed Configuration          | Fixed configuration.                                                                                                                                                        | 0x00    |

| 0x0D    | [7:0]  | Fixed Configuration          | Fixed configuration.                                                                                                                                                        | 0x00    |

| 0x0E    | [7:0]  | <b>Fixed Configuration</b>   | Fixed configuration.                                                                                                                                                        | 0x00    |

# **EEPROM Passcode (Level 2 Memory Access)**

Perform the following steps to set a memory passcode:

- 1. Write value 8'hAB to address 0x10 to unlock Level 1 memory access.

- 2. Write the desired passcode 7x8 bits to the memory address from 0x18 to 0x1E.

- 3. Write 8'hBA to address 0x1F to set the passcode.

**NOTE:** The factory/default passcode is h00-h00-h00-h00-h00-h00.

### **EEPROM Unlock**

The AEAT-9955 consists of three levels of memory:

- 1. Level 0: No unlock required.

- 2. Level 1: Unlock required. To unlock, write address 0x10 = 8'hAB.

- 3. Level 2: Unlock required. To unlock, after unlocking Level 1, write address 0x18-0x1E = <User Passcode>.

- 4. Level 2a: Unlock required. To unlock, after unlocking Level 2, write address 0x1F = 8'hCD.

#### NOTE:

- Default user passcode = All 0s, meaning that no additional write is required at these addresses to unlock Level 2 if the user passcode has not been created.

- Level 2a access is applicable only for date codes starting from January 2025, with the product marking identification "E", as shown in the following figure:

### **EEPROM Page**

Perform the following steps to load the EEPROM page to the MTP register:

- 1. Perform the steps in EEPROM Unlock to unlock the EEPROM.

- 2. To change the EEPROM page, write the desired page number to address 0x16 to load the selected EEPROM page into the MTP shadow register. For example, writing the value 0x00 to address 0x16 loads the Customer Configuration Registers (Page 0).

**NOTE:** Upon power-up, the MTP shadow register is loaded with the Customer Configuration Registers (Page 0).

# **EEPROM Programming**

Perform the following steps to program the MTP shadow register to EEPROM:

- Write the desired values to the current MTP register (Customer Reserve / Configuration Shadow register).

- 2. Verify the written value by reading back all registers.

- 3. Write value 8'hA1 to address 0x14 to program the current MTP registers to EEPROM.

- 4. Read memory busy bit[7] address 0x2A:

- 0: EEPROM programming completed

- 1: EEPROM programming in progress

**NOTE:** EEPROM programming is required before changing the EEPROM page.

### **Encoder Calibration**

#### **Auto-Calibration Function**

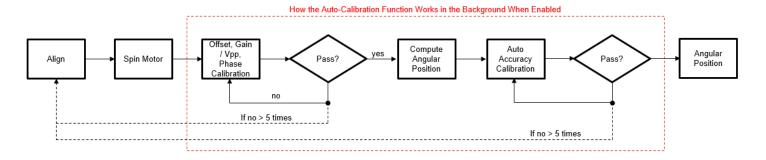

The AEAT-9955 encoder series comes with an Auto-Calibration function that utilizes a complex built-in algorithm to calibrate the encoder into achieving its most accurate angular accuracy. As it is designed for ease of use and cost-effectiveness by circumventing the need for a reference encoder, this calibration mode requires the users to simply align the magnet to the rotary shaft, rotate the magnet, and enable the Auto-Calibration function, and the AEAT-9955 encoder itself will perform the calibration and notify the user if the function is successfully completed. The following figure describes the sequence of this function.

Figure 2: AEAT-9955 Sequence of Auto-Calibration

As shown in the preceding figure, upon enabling the Auto-Calibration function, the AEAT-9955 first calibrates the offset, gain, and phase of the sine/cosine signals that it receives from the magnet. This is the AEAT-9955 way of ensuring that the magnet is first properly aligned within an acceptable calibration range. If it is not, the AEAT-9955 will disqualify the calibration and notify the user that the calibration has failed. Otherwise, the AEAT-9955 will proceed to compute the angular position and perform the Auto-Calibration function.

The AEAT-9955 encoder series allows users to further adjust its internal settings in an attempt to pass this phase. In the case when either the magnet is not properly aligned or the magnet does not quite fit the specifications for an optimal performance, the user can adjust the AEAT-9955 internal settings to pass the calibration at the detriment of performance and overall accuracy.

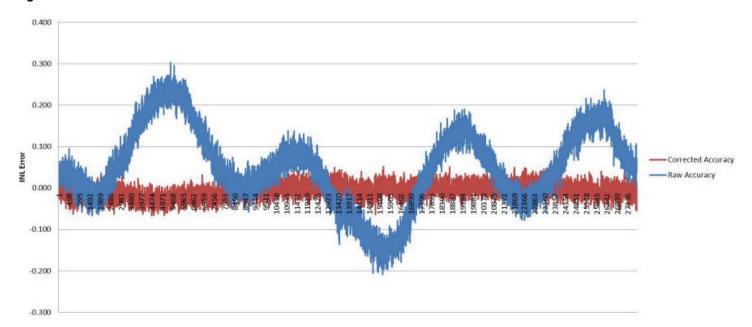

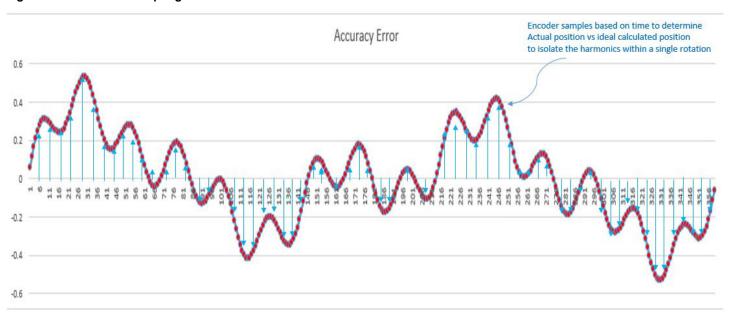

The Auto-Calibration function first takes in the computed angular position and calculates the harmonics of the angular accuracy error present within a 360-degree rotation of a magnet and stores them as correction points within the AEAT-9955 internal memory. These correction points will then be used to compensate the errors to achieve an optimal accuracy. The following figure illustrates the before and after Auto-Calibration function and its accuracy difference.

Figure 3: AEAT-9955 Before and After Auto-Calibration

**NOTE:** For this function to be as effective as possible, the user must ensure that during calibration the speed of the rotation of the magnet is stable with as minimal of a speed ripple as possible.

#### **Auto-Calibration without Lookup Table**

The differences between the sampled actual positions and the calculated ideal positions are stored in the AEAT-9955's internal memory, referred to as the lookup table. Auto-calibration without the lookup table reflects the raw accuracy of the magnet system, as illustrated in Figure 3 (blue line: Raw Accuracy). This feature allows users to implement their own algorithms for lookup table compensation.

### **Auto-Calibration with Lookup Table**

The lookup table represents the populated points of raw accuracy. Auto-calibration with the lookup table provides the corrected accuracy, calculated by subtracting the raw accuracy from the lookup table values, as illustrated in Figure 3 (red line: Corrected Accuracy).

Auto-calibration can be performed in two ways: either via an SPI register write-in or via hardware pin M1. The methods are described in the following two sections.

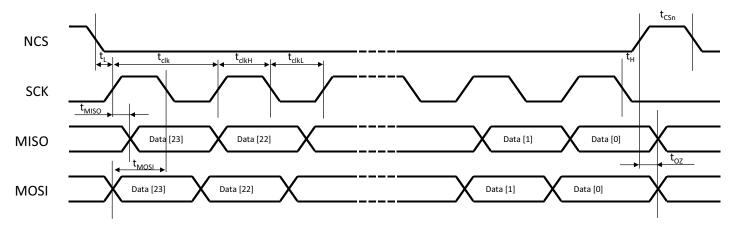

#### **SPI Register Auto-Calibration**

- 1. Mount the encoder to the motor system (with a magnet).

- 2. Rotate the magnet at a constant speed ranging from 10 rpm to 2000 rpm.

- 3. Once the speed stabilizes, write value 8'h2 to address 0x15 to initiate the calibration sequence.

- 4. Read the calibration status on bit [1:0] address 0x2A.

- 10: Calibration pass

- 11: Calibration fail

- 5. Write value 8'h0 to address 0x15 to exit the calibration sequence.

- 6. The calibration value is automatically stored in memory; no further programming is required.

- To erase the calibration value, write value 8'h1 to address 0x15.

- To return to operation mode, write value 8'h0 to address 0x15.

### Hardware Pin M1 (Trigger) Calibration

- 1. Mount the encoder to the motor system (with a magnet).

- 2. Rotate the magnet at a constant speed ranging from 10 rpm to 2000 rpm.

- 3. Once the speed stabilizes, pull the signal high, M1 for more than 50 ms to initiate the calibration sequence.

- 4. Read the calibration status on output pin ABI.

- If AB = 1, I = 0: Calibration pass

- If AB = 1, I = 1: Calibration fail

- 5. The calibration value is automatically stored in memory; no further programming is required.

The AEAT-9955 not only allows users to perform its Auto-Calibration function through its various communication protocols via software means, it also allows users to perform the same calibration function via hardware through the use of one of its dedicated pads. This section explains how the hardware-based pad-initiated calibration can be performed and what settings can be changed to impact its behavior.

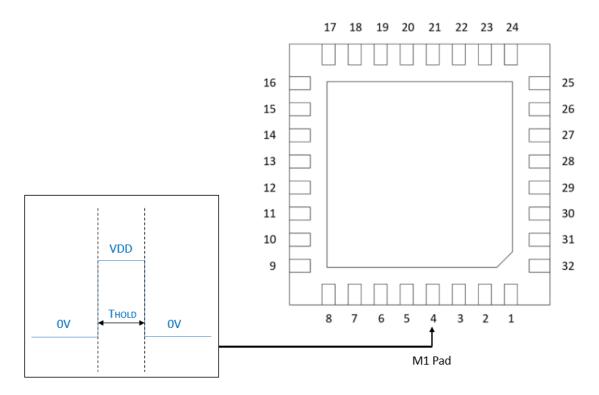

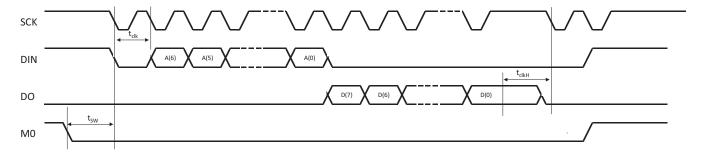

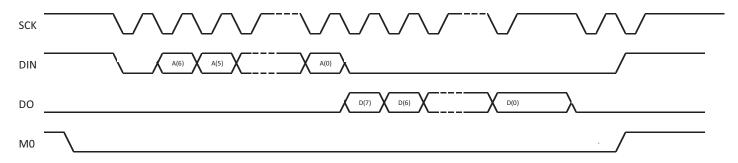

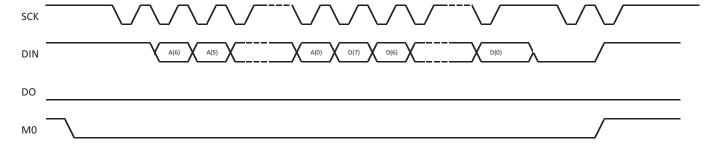

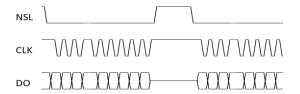

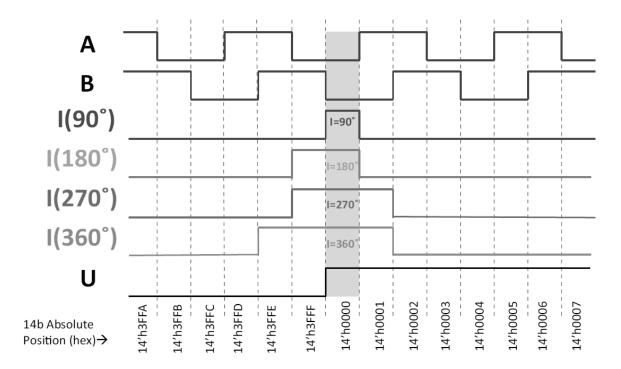

The following figure illustrates the pattern of signal necessary to trigger a pad-initiated calibration.

Figure 4: Method to Trigger Pad-Initiated Calibration

#### Pin Configurations (Bottom View)

As per the preceding figure, to trigger a pad-initiated calibration, the user must send a signal into the pad 4 or M1 pad by triggering a valid VDD high for a T<sub>HOLD</sub> duration of time while the magnet is rotating at stable speeds. Then the user must monitor the pad 8 or A pad, the pad 9 or B pad, and the pad 10 or I pad to know if the pad-initiated calibration is successful.

- If A/B/I = High/High/Low, calibration is successful.

- If A/B/I = High/High/High, calibration is not successful.

The flow of what occurs internally is as discussed earlier in the Auto-Calibration Function section. This means that should users want to modify the calibration steps, they may refer to the previous section. Although the internal calibration within the system is identical for both hardware- and software-triggered calibration, the method to initiate calibration differs. To further simplify pad-initiated calibration for customers, the AEAT-9955 offers several settings to adjust the criteria for triggering this function. See the settings in Table 3, Customer Configuration Registers (Page 0), which are as follows:

- Auto-calibration Hardware Hold Time (address 0x01 [bit 1])

- Multiple Auto-calibration Hardware (address 0x01 [bit 0])

- Auto-calibration Hardware (address 0x06 [bit 7])

#### **Zero Reset Calibration**

The AEAT-9955 allows users to configure a zero reset position. The following is the calibration procedure.

#### Via an SPI Register

- 1. Stop the encoder to the motor system at the desired location.

- 2. Once it is stationary, write value 8'h8 to address 0x15 to reset the absolute single-turn position.

- 3. Read the calibration status on bit [3:2] address 0x2A.

- 10: Calibration pass

- 11: Calibration fail

- 4. Write value 8'h0 to address 0x15 to exit the calibration sequence.

- 5. The offset value is automatically stored in memory; no further programming is required.

- To erase the calibration value, write value 8'h4 to address 0x15.

- To return to operation mode, write value 8'h0 to address to 0x15.

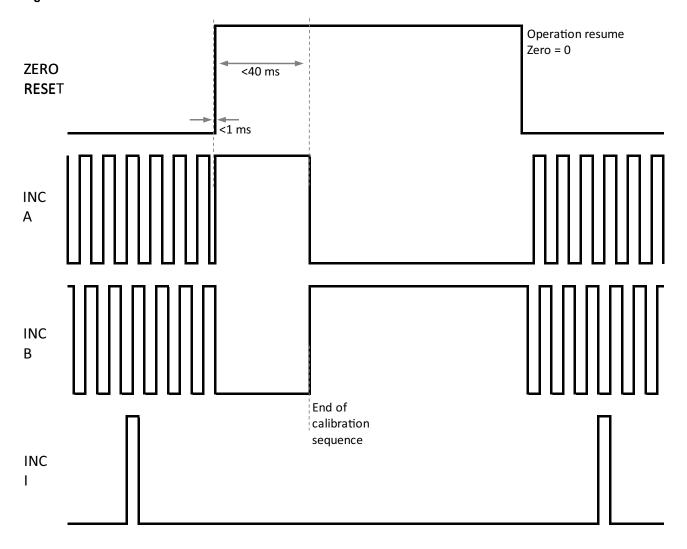

Figure 5: Zero Reset Calibration

# **Compensation for Misalignment**

The AEAT-9955 encoder actively detects magnetic flux in real time through its integrated Hall sensors. The detected magnetic flux is then converted into signals interpreted by the encoder to determine if any mechanical misalignment of the magnet has occurred during operation.

If any misalignment occurs, the AEAT-9955 encoder compensates in real time for imperfections in the sine and cosine signals generated by the misalignments. This compensation occurs in the background and improves the encoder's tolerance to magnet misalignment.

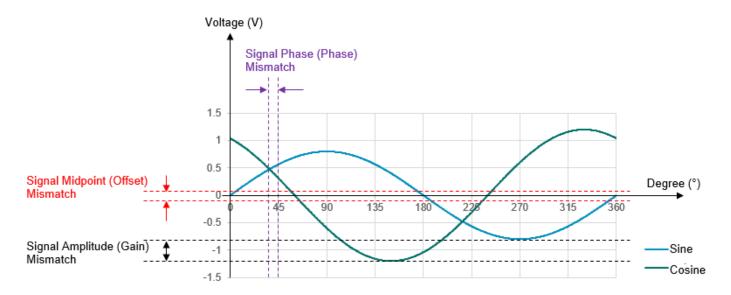

In an uncompensated system, misalignment can distort the critical sine and cosine signals generated from the magnetic flux, which are used in the encoder's positioning computation. An example of a poorly aligned magnet is shown in the following figure, where the signal perceived by the encoder exhibits errors in offset, gain, and phase.

Figure 6: An Uncompensated Sine/Cosine Detected by the AEAT-9955 during Magnet Misalignment

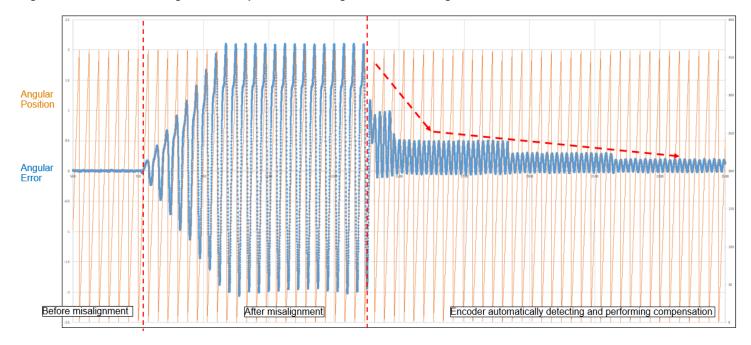

Because compensation for any magnet misalignment occurs in real time, the system performs this adjustment in small increments. This means that whenever a misalignment happens, the AEAT-9955 encoder requires several magnet rotations, depending on the magnitude of the errors introduced, to detect and fully compensate for these inaccuracies.

The following figure demonstrates a typical angular error immediately after a misalignment occurs, up to the point when the system detects the error and begins compensation. In each magnetic turn, the error is calculated using a perfect optical reference encoder against our measured device under test (DUT).

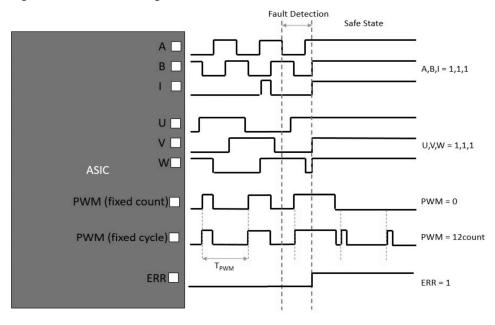

Figure 7: AEAT-9955 Misalignment Compensation During Deliberate Misalignment