## ACPL-C799U

### 動作温度範囲の広い $\pm 50$ mV 光絶縁型 シグマ - デルタ変調器

#### 概要

Broadcom® ACPL-C799U は、光結合技術を利用したガルバニック絶縁を備え、アナログ入力信号を高速データ・ストリームに変換する 1 ビット二次シグマ-デルタ ( $\Sigma$ - $\Delta$ ) 変調器です。ACPL-C799U は、適切なデジタル・フィルタを使用することにより、5V 電源からダイナミック・レンジ 77dB で動作します。 $\pm 50$ mV (フルスケール  $\pm 80$ mV) の差動入力は、モータ相電流検出などの用途においてシャント抵抗や他の低電圧信号源への直接接続に理想的です。

アナログ入力は、内蔵クロックを使ったシグマ-デルタ・オーバーサンプリングにより、連続的にサンプリングされます。信号情報は、周波数 10MHz の変調器データに 1 の密度として含まれ、このデータは、コード化され絶縁境界を越えて伝送された後、デジタル値 1 と 0 の高速データ・ストリームに復調されます。元の信号情報は、デジタル・フィルタを使用して復元できます。データおよびクロック用シリアル・インターフェースの電源範囲は広く 3V ~ 5.5V です。

高度な光結合技術との組み合わせにより、変調器は、高いノイズ余裕度と優れたアイソレーション・モード過渡耐性を提供します。ACPL-C799U は、最小 0.5 mm の絶縁物厚 (DTI) を持ち、確実な強化絶縁と高い動作絶縁電圧を提供し、フェイル・セーフ設計に最適です。これら卓越した絶縁性能は、容量結合または磁気結合を利用した DTI がマイクロメートル単位の代替デバイスにはない特長です。この絶縁型 A-D コンバータは、ストレッチ SO-8 (SSO-8) パッケージで提供され、従来の電流トランスデューサよりも低コストでモータの電流を正確に測定するために必要な高信頼性、小型化、高絶縁性能、および温度特性を提供します。

#### 特長

- 1 ビット二次シグマ-デルタ変調器

- 内部クロック： 10 MHz

- ノード・ミッシング・コード 16 ビット分解能 (12 ビット ENOB)

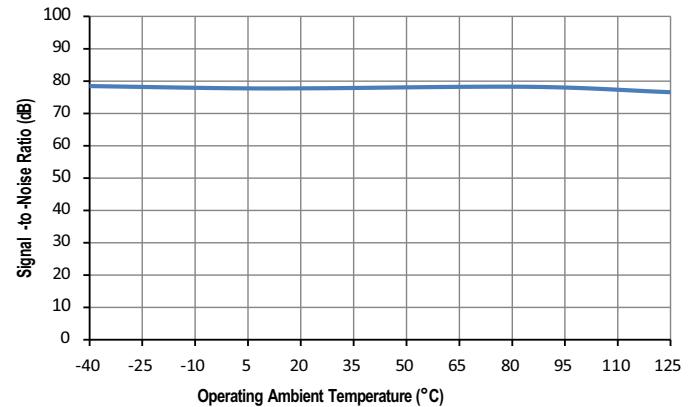

- 信号対ノイズ比： 77 dB (標準)

- コンパクトな、表面実装 SSO-8 パッケージ

- 卓越した光学分離および絶縁性能

- 同相過渡耐性： 25 kV/ $\mu$ s

- 安全規格：

- IEC/EN/DIN EN 60747-5-5：動作絶縁電圧 1414 V<sub>PEAK</sub>

- UL 1577：絶縁電圧 5000 V<sub>RMS</sub>、1 分

- CAN/CSA-C22.2 No. 62368-1

#### 仕様

- 広い動作温度範囲： -40°C ~ +125°C

- ゲイン誤差：  $\pm 1\%$

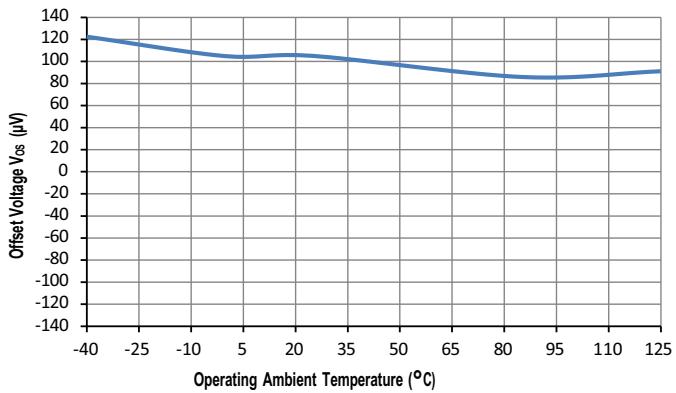

- オフセット・ドリフト：  $\pm 1.3 \mu$ V/°C 最大

- 単一 5V 電源でリニア入力電圧範囲：  $\pm 50$  mV (フルスケール  $\pm 80$ mV)

- 広いデジタル・インターフェース電源範囲： 3V ~ 5.5V

#### 応用例

- モータ相およびレール電流検出

- 電力インバータ電流検出

- 産業プロセス制御

- データ収集システム

- 各種電流検出

- 従来の電流トランスデューサの置換

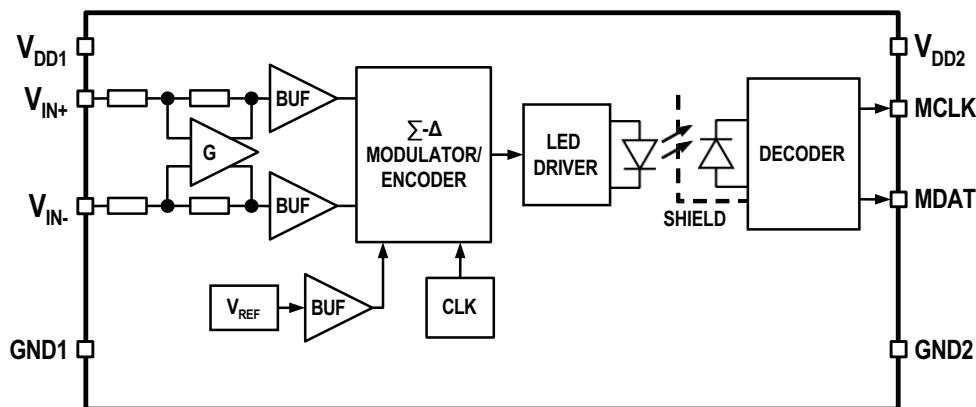

## 回路図

図 1：回路図

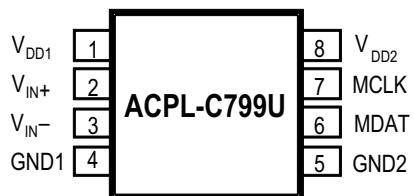

## ピン配置と説明

図 2：ピン配置

## ピンの説明

表 1：ピンの説明

| ピン番号 | 記号        | 概要                          |

|------|-----------|-----------------------------|

| 1    | $V_{DD1}$ | 信号入力側（アナログ側）の電源電圧（GND1 基準）  |

| 2    | $V_{IN+}$ | 正アナログ入力。推奨入力範囲 $\pm 50$ mV  |

| 3    | $V_{IN-}$ | 負アナログ入力。推奨入力範囲 $\pm 50$ mV  |

| 4    | GND1      | 信号入力側の電源グランド                |

| 5    | GND2      | データ/クロック出力側（デジタル側）の電源グランド   |

| 6    | MDAT      | 変調器データ出力                    |

| 7    | MCLK      | 変調器クロック出力                   |

| 8    | $V_{DD2}$ | データ出力側（デジタル側）の供給電源（GND2 基準） |

## オーダ情報

表2：オーダ情報

| 型名         | オプション<br>(RoHS 指令準拠) | パッケージ         | 表面実装 | テープ & リール | UL 5000 VRMS / 1<br>分定格 | IEC/EN/DIN EN<br>60747-5-5 | 梱包単位           |

|------------|----------------------|---------------|------|-----------|-------------------------|----------------------------|----------------|

| ACPL-C799U | -000E                | ストレッチ<br>SO-8 | X    | —         | X                       | X                          | 80 個/<br>チューブ  |

|            | -500E                |               | X    | X         | X                       | X                          | 1000 個/<br>リール |

ご注文の際は、型名欄から選択した製品型名とオプション欄のご希望のオプションとを組み合わせて発注してください。

例：

ACPL-C799U-500E は、表面実装パッケージ、テープ & リール梱包、RoHS 指令準拠の製品です。

オプションのデータ・シートもご用意しています。詳細は、Broadcom の正規販売代理店までお問い合わせください。

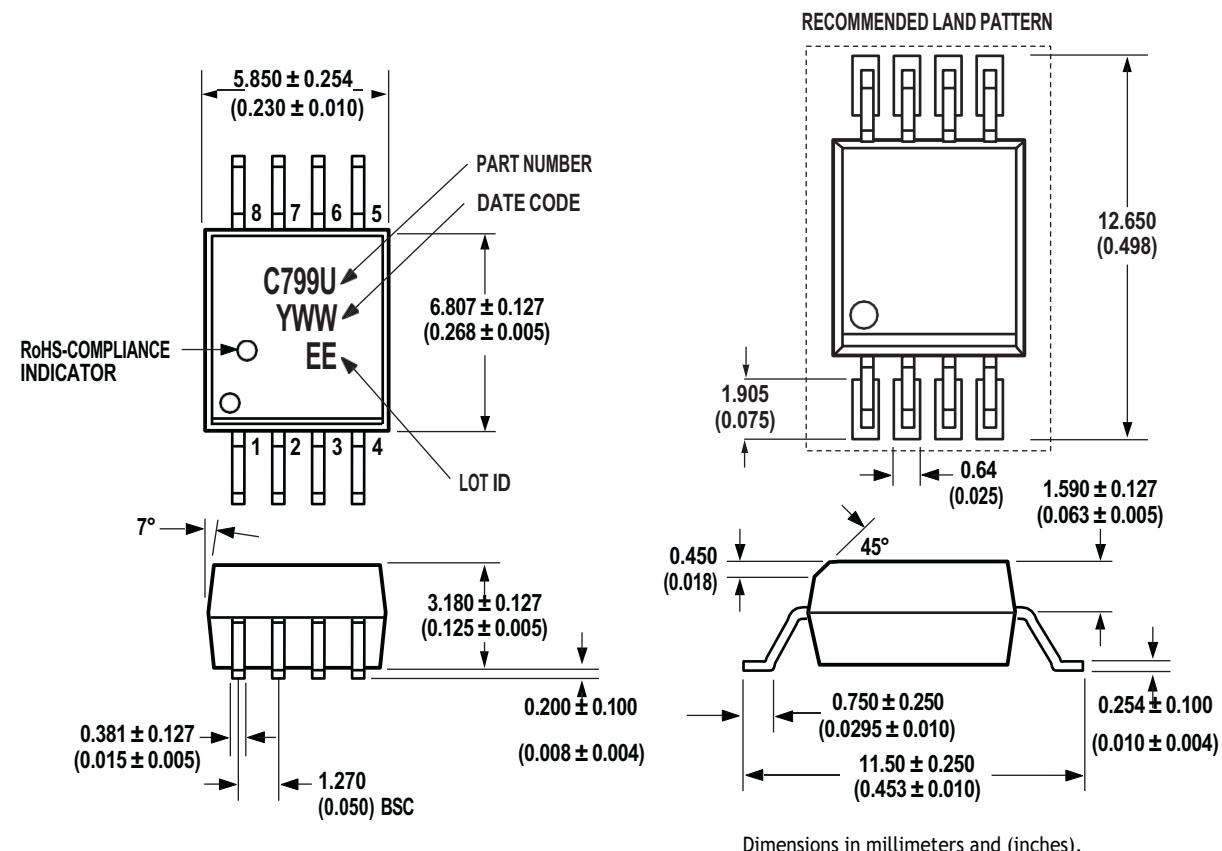

## パッケージ寸法図

### ストレッチ SO-8 パッケージ (SSO-8)

図 3：パッケージ寸法図

Dimensions in millimeters and (inches).

Notes:

Lead coplanarity = 0.1 mm (0.004 inches).

Floating lead protrusion = 0.25 mm (10 mils) max.

## 推奨鉛フリー IR プロファイル

JEDEC 規格 J-STD-020 (最新版) に準拠したリフロー条件を推奨。非ハロゲン化物系フラックスを使用してください。

## 安全規格

The ACPL-C799U is approved by the following organizations.

表 3：Regulatory Information

|                         |                                                                                                                       |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------|

| IEC/EN/DIN EN 60747-5-5 | Approval with Maximum Working Insulation Voltage $V_{IORM} = 1414$ V <sub>PEAK</sub>                                  |

| UL                      | Approval under UL 1577, component recognition program up to $V_{ISO} = 5000$ V <sub>RMS</sub> /1 minute. File E55361. |

| CSA                     | Approval under CAN/CSA-C22.2 No. 62368-1.                                                                             |

## IEC/EN/DIN EN 60747-5-5 絶縁特性

表 4 : IEC/EN/DIN EN 60747-5-5 Insulation Characteristics

| Description                                                                                                                                                               | Symbol                | Value       | Units             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-------------|-------------------|

| Installation Classification per DIN VDE 0110/1.89, Table 1                                                                                                                |                       |             |                   |

| For rated mains voltage $\leq 600 \text{ V}_{\text{RMS}}$                                                                                                                 | —                     | I-IV        | —                 |

| For rated mains voltage $\leq 1000 \text{ V}_{\text{RMS}}$                                                                                                                | —                     | I-III       | —                 |

| Climatic Classification                                                                                                                                                   | —                     | 40/125/21   | —                 |

| Pollution Degree (DIN VDE 0110/1.89)                                                                                                                                      | —                     | 2           | —                 |

| Maximum Working Insulation Voltage                                                                                                                                        | $V_{\text{IORM}}$     | 1414        | $V_{\text{PEAK}}$ |

| Input to Output Test Voltage, Method b<br>$V_{\text{IORM}} \times 1.875 = V_{\text{PR}}$ , 100% Production Test with $t_m = 1$ second, Partial Discharge $< 5 \text{ pC}$ | $V_{\text{PR}}$       | 2652        | $V_{\text{PEAK}}$ |

| Input to Output Test Voltage, Method a<br>$V_{\text{IORM}} \times 1.6 = V_{\text{PR}}$ , Type and Sample Test, $t_m = 10$ seconds, Partial Discharge $< 5 \text{ pC}$     | $V_{\text{PR}}$       | 2262        | $V_{\text{PEAK}}$ |

| Highest Allowable Overvoltage (Transient Overvoltage, $t_{\text{ini}} = 60$ seconds)                                                                                      | $V_{\text{IOTM}}$     | 8000        | $V_{\text{PEAK}}$ |

| Safety-Limiting Values (Maximum values allowed in the event of a failure)                                                                                                 |                       |             |                   |

| Case Temperature                                                                                                                                                          | $T_s$                 | 175         | °C                |

| Input Current <sup>a</sup>                                                                                                                                                | $I_{s,\text{INPUT}}$  | 230         | mA                |

| Output Power <sup>a</sup>                                                                                                                                                 | $P_{s,\text{OUTPUT}}$ | 600         | mW                |

| Insulation Resistance at $T_s$ , $V_{\text{IO}} = 500\text{V}$                                                                                                            | $R_s$                 | $\geq 10^9$ | Ω                 |

a. Transient voltage of 2 seconds up to 6V on the inputs does not cause latch-up or damage to the device.

## 絶縁と安全に関連する仕様

表 5 : Insulation and Safety-Related Specifications

| Parameter                                         | Symbol | Value | Units | Conditions                                                                                                                                                 |

|---------------------------------------------------|--------|-------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Minimum External Air Gap (External Clearance)     | L(101) | 8.0   | mm    | Measured from input terminals to output terminals, shortest distance through air.                                                                          |

| Minimum External Tracking (External Creepage)     | L(102) | 8.0   | mm    | Measured from input terminals to output terminals, shortest distance path along body.                                                                      |

| Minimum Internal Plastic Gap (Internal Clearance) | —      | 0.5   | mm    | Through insulation distance, conductor to conductor, usually the direct distance between the photoemitter and photodetector inside the optocoupler cavity. |

| Tracking Resistance (Comparative Tracking Index)  | CTI    | >175  | V     | DIN IEC 112/VDE 0303 Part 1                                                                                                                                |

| Isolation Group                                   | —      | IIIa  | —     | Material Group (DIN VDE 0110, 1/89, Table 1)                                                                                                               |

## 絶対最大定格

表 6 : Absolute Maximum Ratings

| Parameter                          | Symbol                                           | Min. | Max.            | Units | Note |

|------------------------------------|--------------------------------------------------|------|-----------------|-------|------|

| Storage Temperature                | $T_S$                                            | -55  | +150            | °C    | —    |

| Ambient Operating Temperature      | $T_A$                                            | -40  | +125            | °C    | —    |

| Supply Voltage                     | $V_{DD1}, V_{DD2}$                               | -0.5 | 6.0             | V     | —    |

| Steady-State Input Voltage         | $V_{IN+}, V_{IN-}$                               | -2   | $V_{DD1} + 0.5$ | V     | a    |

| Two-Second Transient Input Voltage | $V_{IN+}, V_{IN-}$                               | -6   | $V_{DD1} + 0.5$ | V     | b    |

| Digital Output Voltages            | MCLK, MDAT                                       | -0.5 | $V_{DD2} + 0.5$ | V     | —    |

| Lead Solder Temperature            | 260°C for 10 seconds, 1.6 mm below seating plane |      |                 |       | —    |

a. Absolute maximum DC current on the inputs = 100 mA, no latch-up or device damage occurs.

b. Transient voltage of 2 seconds up to 6V on the inputs does not cause latch-up or damage to the device.

## 推奨動作条件

表 7 : Recommended Operating Conditions

| Parameter                     | Symbol             | Min. | Max. | Units | Note |

|-------------------------------|--------------------|------|------|-------|------|

| Ambient Operating Temperature | $T_A$              | -40  | +125 | °C    | —    |

| $V_{DD1}$ Supply Voltage      | $V_{DD1}$          | 4.5  | 5.5  | V     | —    |

| $V_{DD2}$ Supply Voltage      | $V_{DD2}$          | 3    | 5.5  | V     | —    |

| Analog Input Voltage          | $V_{IN+}, V_{IN-}$ | -50  | +50  | mV    | a    |

a. Full scale signal input range 80 mV.

## 電気特性仕様

All minimum and maximum values are at recommended conditions, unless otherwise noted. All typical values are at  $T_A = 25^\circ\text{C}$ ,  $V_{DD1} = 5\text{V}$ ,  $V_{DD2} = 5\text{V}$ , tested with a Sinc3 filter and 256 decimation ratio.

表 8 : Electrical Specifications

| Parameter                                | Symbol              | Min. | Typ. | Max. | Units                        | Test Conditions/Notes                                                                                          | Figure | Note |

|------------------------------------------|---------------------|------|------|------|------------------------------|----------------------------------------------------------------------------------------------------------------|--------|------|

| Static Characteristics                   |                     |      |      |      |                              |                                                                                                                |        |      |

| Resolution                               | —                   | 16   | —    | —    | Bits                         | Decimation filter output set to 16 bits.                                                                       | —      | —    |

| Integral Nonlinearity                    | INL                 | -16  | ±8   | 16   | LSB                          | See <a href="#">定義</a> .                                                                                       | —      | —    |

| Differential Nonlinearity                | DNL                 | -0.9 | —    | 0.9  | LSB                          | No missing codes, guaranteed by design. See <a href="#">定義</a> .                                               | —      | —    |

| Offset Error                             | $V_{OS}$            | -1.0 | 0.1  | 1.0  | mV                           | $T_A = 25^\circ\text{C}$ , $V_{DD1} = 5\text{V}$ . Short before anti-aliasing filter. See <a href="#">定義</a> . | 5      | —    |

| Offset Error Drift vs. Temperature       | $dV_{OS}/dT_A$      | -1.3 | ±0.1 | 1.3  | $\mu\text{V}/^\circ\text{C}$ | $V_{DD1} = 5\text{V}$                                                                                          | —      | a    |

| Offset Drift vs. $V_{DD1}$               | $dV_{OS}/dV_{DD1}$  | —    | 0.1  | —    | mV/V                         | —                                                                                                              | —      | —    |

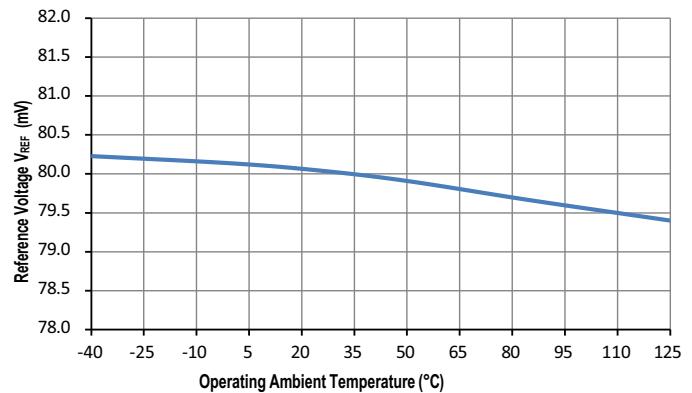

| Internal Reference Voltage               | $V_{REF}$           | —    | 80   | —    | mV                           | —                                                                                                              | —      | —    |

| Reference Voltage Tolerance (Gain Error) | —                   | -1   | —    | 1    | %                            | $T_A = 25^\circ\text{C}$ . See <a href="#">定義</a> .                                                            | —      | —    |

| $V_{REF}$ Drift vs. Temperature          | $dV_{REF}/dT_A$     | —    | 50   | —    | $\text{ppm}/^\circ\text{C}$  | —                                                                                                              | —      | —    |

|                                          |                     |      |      |      |                              |                                                                                                                |        |      |

| $V_{REF}$ Drift vs. $V_{DD1}$            | $dV_{REF}/dV_{DD1}$ | —    | 50   | —    | $\mu\text{V}/\text{V}$       | —                                                                                                              | —      | —    |

| Analog Inputs                            |                     |      |      |      |                              |                                                                                                                |        |      |

表8 : Electrical Specifications (続き)

| Parameter                                   | Symbol           | Min.                   | Typ.                   | Max. | Units | Test Conditions/Notes                                                                              | Figure | Note |

|---------------------------------------------|------------------|------------------------|------------------------|------|-------|----------------------------------------------------------------------------------------------------|--------|------|

| Full-Scale Differential Voltage Input Range | FSR              | —                      | V <sub>REF</sub>       | —    | mV    | V <sub>IN</sub> = V <sub>IN+</sub> - V <sub>IN-</sub>                                              | —      | b    |

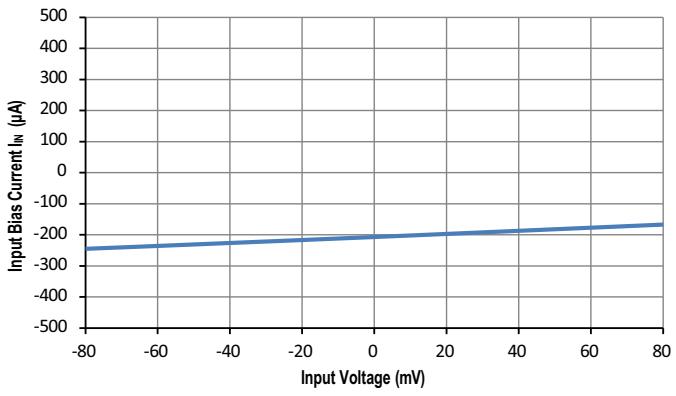

| Input Bias Current                          | I <sub>INA</sub> | —                      | -0.2                   | —    | mA    | V <sub>DD1</sub> = 5V, V <sub>DD2</sub> = 5V,<br>V <sub>IN+</sub> = V <sub>IN-</sub> = 0V          | 7      | c    |

| Input Resistance                            | R <sub>IN</sub>  | —                      | 1.9                    | —    | kΩ    | Across V <sub>IN+</sub> or V <sub>IN-</sub> to GND1                                                | —      | c    |

| Input Capacitance                           | C <sub>INA</sub> | —                      | 8                      | —    | pF    | Across V <sub>IN+</sub> or V <sub>IN-</sub> to GND1,<br>V <sub>p-p</sub> = 80 mV, 1 MHz sine wave. | —      | —    |

| Dynamic Characteristics                     |                  |                        |                        |      |       | VS = -50 mVp to 50 mVp, 1 kHz sine wave                                                            |        |      |

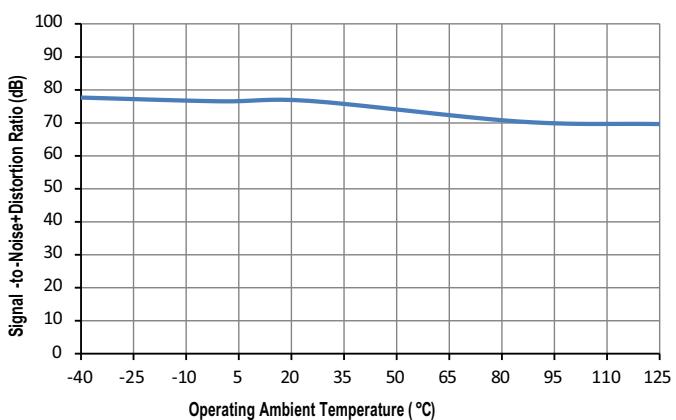

| Signal-to-Noise Ratio                       | SNR              | 70                     | 77                     | —    | dB    | See 定義.                                                                                            | 8      | —    |

| Signal-to-(Noise + Distortion) Ratio        | SNDR             | 64                     | 76                     | —    | dB    | See 定義.                                                                                            | 9      | —    |

| Effective Number of Bits                    | ENOB             | —                      | 12                     | —    | Bits  | See 定義.                                                                                            | —      | —    |

| Isolation Transient Immunity                | CMR              | 25                     | —                      | —    | kV/μs | V <sub>CM</sub> = 1 kV. See 定義.                                                                    | —      | —    |

| Digital Outputs                             |                  |                        |                        |      |       |                                                                                                    |        |      |

| Output High Voltage                         | V <sub>OH</sub>  | V <sub>DD2</sub> - 0.4 | V <sub>DD2</sub> - 0.2 | —    | V     | I <sub>OUT</sub> = -4 mA                                                                           | —      | —    |

| Output Low Voltage                          | V <sub>OL</sub>  | —                      | 0.2                    | 0.4  | V     | I <sub>OUT</sub> = 4 mA                                                                            | —      | —    |

| Power Supply                                |                  |                        |                        |      |       |                                                                                                    |        |      |

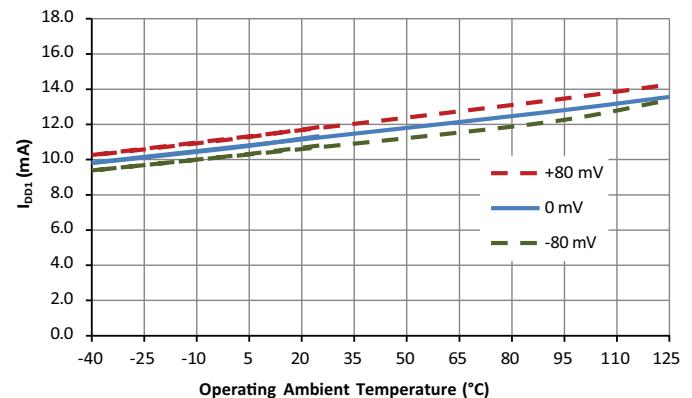

| V <sub>DD1</sub> Supply Current             | I <sub>DD1</sub> | —                      | 11.3                   | 17.5 | mA    | —                                                                                                  | 10     | —    |

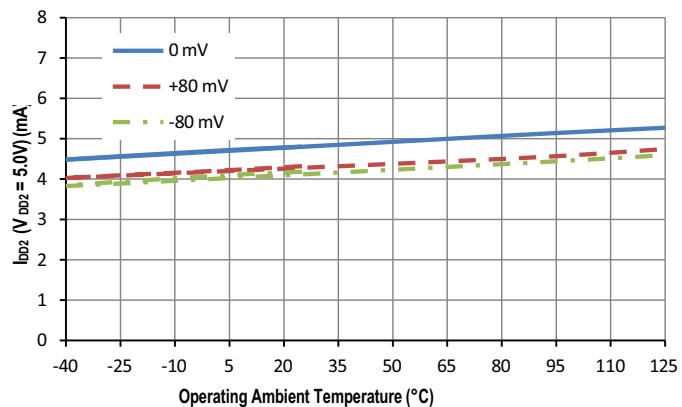

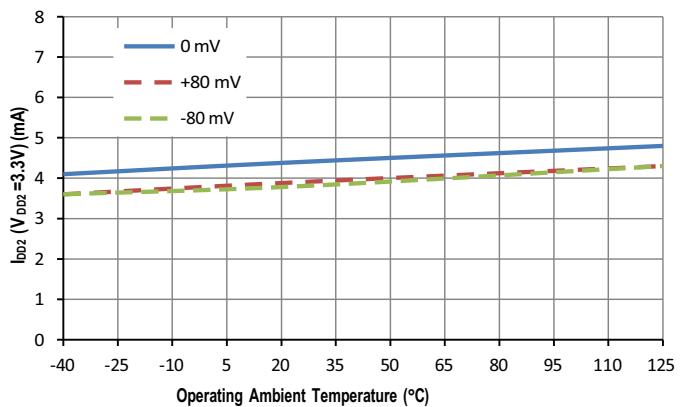

| V <sub>DD2</sub> Supply Current             | I <sub>DD2</sub> | —                      | 5                      | 6.5  | mA    | —                                                                                                  | 11, 12 | —    |

a. The maximum offset error Vos\_max and minimum offset error Vos\_min is determined within the full operating temperature range. Offset Error Drift vs. Temperature is calculated by using the box method:  $dV_{OS}/dT_A = (Vos_{max} - Vos_{min}) / \text{AmbientTempRange}$ .

b. Beyond the positive full-scale input range the data output is all ones. Beyond the negative full-scale input range the data output is all zeroes.

c. Time averaged values are shown.  $R_{IN} = V_{IN} / I_{IN}$ .

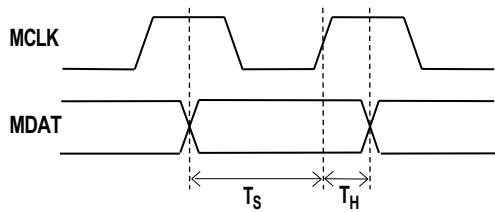

## タイミング仕様

All minimum and maximum values are at recommended conditions, unless otherwise noted. All typical values are at  $T_A = 25^\circ\text{C}$ ,  $V_{DD1} = 5\text{V}$ ,  $V_{DD2} = 5\text{V}$ .

表 9 : Timing Specifications

| Parameter                               | Symbol     | Min. | Typ. | Max. | Units | Test Conditions       | Figure             |

|-----------------------------------------|------------|------|------|------|-------|-----------------------|--------------------|

| Modulator Clock Output Frequency        | $f_{MCLK}$ | 9    | 10   | 11   | MHz   | $C_L = 15 \text{ pF}$ | <a href="#">13</a> |

| Modulator Clock Duty Cycle              | DC         | 40   | 50   | 70   | %     | $C_L = 15 \text{ pF}$ | —                  |

| Modulator Clock Rising Time             | $t_R$      | —    | 5    | —    | ns    | $C_L = 15 \text{ pF}$ | —                  |

| Modulator Clock Falling Time            | $t_F$      | —    | 5    | —    | ns    | $C_L = 15 \text{ pF}$ | —                  |

| Data Setup Time Before MCLK Rising Edge | $t_S$      | 50   | 70   | —    | ns    | $C_L = 15 \text{ pF}$ | —                  |

| Data Hold Time After MCLK Rising Edge   | $t_H$      | 10   | 20   | —    | ns    | $C_L = 15 \text{ pF}$ | —                  |

図 4 : MCLK and MDAT Data Timing

## パッケージ特性

表 10 : Package Characteristics

| Parameter                                | Symbol    | Min. | Typ.       | Max. | Units                   | Test Conditions                                                                 | Note |

|------------------------------------------|-----------|------|------------|------|-------------------------|---------------------------------------------------------------------------------|------|

| Input-Output Momentary Withstand Voltage | $V_{ISO}$ | 5000 | —          | —    | $\text{V}_{\text{RMS}}$ | $\text{RH} \leq 50\%$ ,<br>$t = 1 \text{ minute}$ ,<br>$T_A = 25^\circ\text{C}$ | a, b |

| Input-Output Resistance                  | $R_{I-O}$ | —    | $>10^{14}$ | —    | $\Omega$                | $V_{I-O} = 500 \text{ V}_{\text{DC}}$                                           | c    |

| Input-Output Capacitance                 | $C_{I-O}$ | —    | 0.5        | —    | $\text{pF}$             | $f = 1 \text{ MHz}$                                                             | c    |

- a. In accordance with UL 1577, each optocoupler is proof tested by applying an insulation test voltage  $6000 \text{ V}_{\text{RMS}}$  for 1 second (leakage detection current limit,  $I_{L-0} = 5 \text{ A}$ ). This test is performed before the 100% production test for partial discharge (method b) shown in [表 4, IEC/EN/DIN EN 60747-5-5 Insulation Characteristics](#).

- b. The Input-Output Momentary Withstand Voltage is a dielectric voltage rating that should not be interpreted as an input-output continuous voltage rating. For the continuous voltage rating, refer to [表 4, IEC/EN/DIN EN 60747-5-5 Insulation Characteristics](#) and your equipment-level safety specification.

- c. This is a two-terminal measurement: pins 1 through 4 are shorted together and pins 5 through 8 are shorted together.

## 標準特性

図 5 : Offset Voltage Change vs. Temperature

図 6 : Reference Voltage  $V_{REF}$  Change vs. Temperature

図 7 : Input Current vs. Input Voltage

図 8 : SNR vs. Temperature

図 9 : SNDR vs. Temperature

図 10 :  $I_{DD1}$  ( $V_{DD1} = 5V$ ) vs. Temperature at Various  $V_{IN}$  DC Inputs

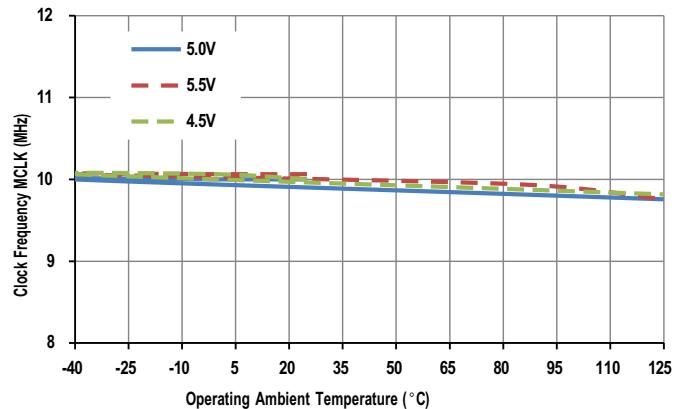

図 11 :  $I_{DD2}$  ( $V_{DD2} = 5V$ ) vs. Temperature at Various  $V_{IN}$  DC Inputs図 12 :  $I_{DD2}$  ( $V_{DD2} = 3.3V$ ) vs. Temperature at Various  $V_{IN}$  DC Inputs図 13 : Clock Frequency vs. Temperature at Various  $V_{DD1}$

## 定義

### 積分非線形性 (INL)

INL は、オフセット誤差とゲイン誤差を除いた状態で、ADC 伝達関数の端点を通る直線からの伝達曲線の最大のずれです。

### 微分非線形性 (DNL)

DNL は、ADC 伝達曲線における 2 つの隣り合ったコード間の 1 LSB の理想値からの実際のコード幅のずれです。DNL は、閉ループ用途では重要な仕様です。DNL 誤差が  $\pm 1$  LSB 未満の場合、ノーミッシング・コードと単調伝達関数が保証されます。

### オフセット誤差

オフセット誤差は、ミッドスケール・コード（無符号デシメーション・フィルタを有する 16 ビット・システムでは 32,768）に対応する実際の入力電圧の 0V からのずれです。オフセット誤差は、ソフトウェアまたはハードウェアにより補正することができます。

### ゲイン誤差（フルスケール誤差）

ゲイン誤差は、正フルスケール・ゲイン誤差と負フルスケール・ゲイン誤差を含みます。正フルスケール・ゲイン誤差は、オフセット誤差が除去された状態で、正フルスケール・コード（16 ビット・システムでは 65,535）に対応する実際の入力電圧の理想差動入力電圧 ( $V_{IN+} - V_{IN-} = +80$  mV) からのずれです。負フルスケール・ゲイン誤差は、オフセット誤差が除去された状態で、負フルスケール・コード（16 ビット・システムでは 0）に対応する実際の入力電圧の理想差動入力電圧 ( $V_{IN+} - V_{IN-} = -80$  mV) からのずれです。ゲイン誤差は、基準誤差を含みます。ゲイン誤差は、ソフトウェアまたはハードウェアにより補正することができます。

### 信号対ノイズ比 (SNR)

SNR は、サンプリング周波数の 1/2 以下の周波数の AC 信号電力とノイズ電力の測定比率です。ノイズ電力は、高調波信号と DC を除きます。

### 信号対（ノイズ + 歪み）比 (SNDR)

SNDR は、ADC の出力における AC 信号電力と、ノイズおよび歪み電力の測定比率です。信号電力は、基本入力信号の RMS 振幅です。ノイズおよび歪み電力は、サンプリング周波数 (DC を除く) の半分までのすべての非基本信号の RMS 総和です。

### 有効ビット数 (ENOB)

ENOB によって、以下で定義される正弦入力（ビット単位）の ADC の有効分解能が決まります。

$$ENOB = (SNDR - 1.76) / 6.02$$

### Isolation Transient Immunity (CMR)

アイソレーション過渡耐性（同相除去または CMR としても知られる）は、絶縁境界を跨いで印加され、変調器クロックまたはデータが不正となる同相電圧の最低上昇/下降率です。データおよびクロック出力は、1  $\mu$ s の同相過渡発生後に、仕様の範囲内で測定されます。

## アプリケーション情報

### 標準的な応用回路

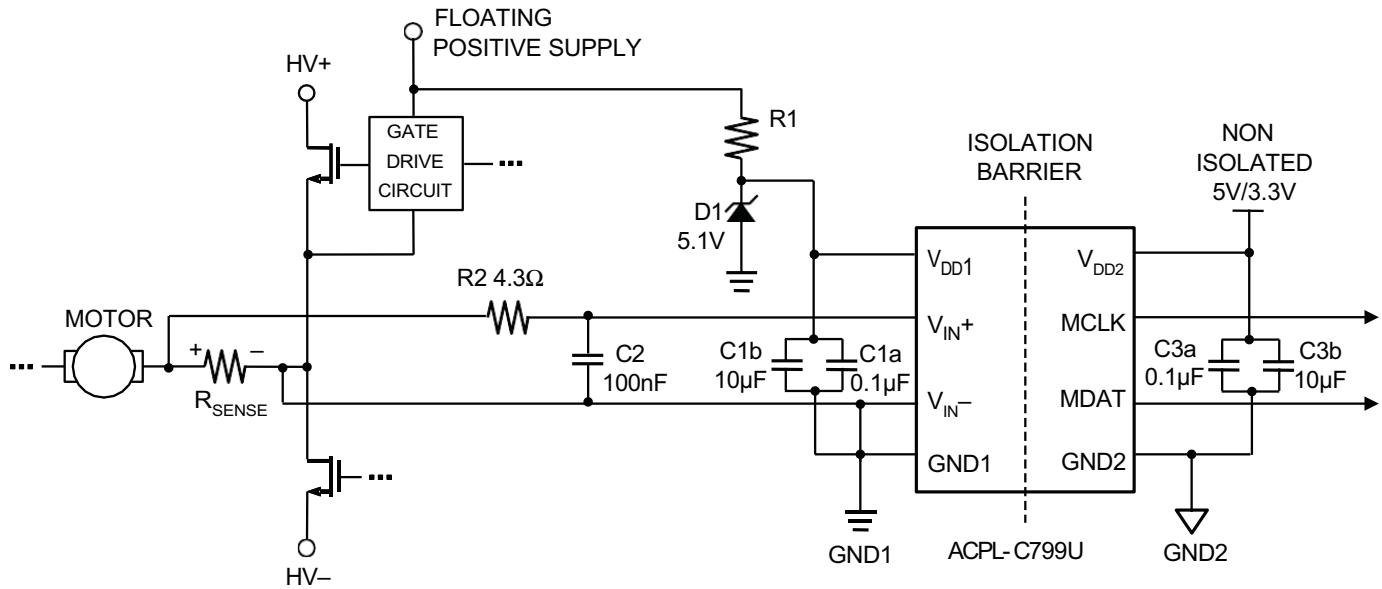

図 14 は、モータ相電流を検出する標準的な応用回路です。適切なシャント抵抗を選択することにより、1A 未満から 400A を超える広範囲の電流を検出することができます。

図 14 : Typical Application Circuit in Motor Phase Current Sensing

### シャント抵抗

電流検出シャント抵抗は、低抵抗（消費電力を最小にする）、低インダクタンス（動作に悪影響を及ぼす可能性がある di/dt 誘導電圧スパイクを最小にする）、および適正公差（全体回路精度を維持する）でなければなりません。シャント抵抗の値を選択するには、通常、消費電力を最小にしながら精度が最大になるようにします。抵抗値が小さいほど消費電力が少なくなり、抵抗を大きくすると、絶縁型変調器の最大入力範囲を利用して回路精度を改善することができます。

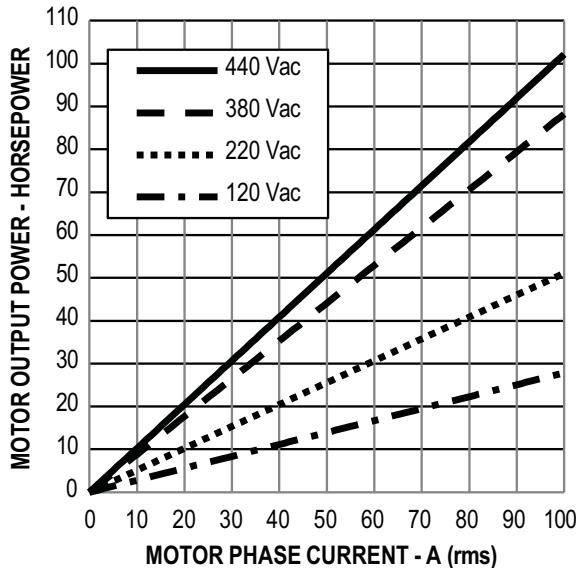

図 15 : Motor Output Horsepower vs. Motor Phase Current and Supply

シャント抵抗を選択するには、まずシャント抵抗が検出する電流の大きさを決めることがあります。図 15 のグラフは、三相誘導モータの各相の RMS 電流を、平均モータ出力（馬力 = hp）とモータ駆動電源電圧の関数として示したもので、シャント抵抗の最大値は、測定する電流と絶縁型変調器の最大推奨入力電圧により決まります。最大抵抗値は、通常動作中に抵抗を流れるピーク電流で最大推奨入力電圧を割ることにより求めることができます。たとえば、モータの最大 RMS 電流が 70 A<sub>rms</sub>、通常動作中に最大 50% の過負荷を許容できる場合、ピーク電流は 150A (= 70×1.414×1.5) となります。過負荷状態を考慮せず最大入力電圧が 50mV と仮定した場合、シャント抵抗の最大値は約 0.5 mΩ になります。この場合、過負荷状態での最大入力電圧は、75 mV (150A×0.5 mΩ) になりますが、それでも  $\pm 80$  mV FSR の範囲内です。

シャント抵抗の最大平均消費電力は、抵抗値に最大 RMS 電流の二乗を乗じて求めることができます、前の例では約 2.45W です。

シャント抵抗の消費電力が大きすぎる場合、抵抗値を小さくすることで消費電力を減らすことができます。抵抗の最小値は、正確さおよび精度の設計要件にも依存します。抵抗値を小さくするほどシャント抵抗の両端電圧が低くなりますが、オフセットとノイズは値が一定であるため、これらが信号振幅に占める割合が大きくなります。抵抗値は、個々の設計要件に応じて最小値と最大値の間で選択します。

検出電流がシャント抵抗を著しく加熱するほど大きいとき、抵抗の温度係数 (tempco) は、シャント抵抗の信号依存温度上昇により非線形性となることがあります。この現象は、シャント抵抗と周囲の間の熱抵抗が大きくなるほど顕著になります。この現象は、シャント抵抗の熱抵抗を小さくするか tempco の低い抵抗器を使用することにより緩和することができます。熱抵抗を低減するには、PC基板上でシャント抵抗の位置を変更するか、より大きいPC基板トレースを使用してより多くの熱を放散させるか、あるいはヒート・シンクを使用するなどの方法があります。

2端子抵抗器の場合、抵抗値が小さくなるほど、リード線の抵抗が全抵抗値に占める割合が大きくなります。これは、抵抗精度に 2 つの大きな影響を及ぼします。第一に、抵抗器の実抵抗が、リードの長さ、リードの曲がり方、基板にどれだけ差し込まれているか、また実装の際にリードが半田をどれだけ吸い上げるかなどの因子に影響されることがあります（これらの問題については、さらに詳述します）。第二に、リードは、通常、抵抗体自体の材料よりも高い tempco を持つ銅などの材料から作られるため、シャント抵抗全体の tempco が高くなります。4 端子抵抗器を使用することにより、これらの影響を排除することができます。4 端子抵抗器は、抵抗体自体の両端に直接ケルビン接続された 2 つの追加端子を有し、これらを抵抗体の両端の電圧を監視するために使用し、他の2つの端子を、負荷電流を流すために使用します。ケルビン接続のため、負荷電流が流れるリード部分の電圧降下は、測定電圧に影響を及ぼしません。

最大 70A<sub>rms</sub> (71 hp または 53 kW) のモータ駆動電流の検出に適したさまざまなサプライヤの 2 端子および 4 端子表面実装型シャント抵抗の例を 表 11 に示します。

表 11 : Example of Two-Terminal and Four Terminal Shunt Resistors for Motor Drives up to 350 A<sub>rms</sub>

| Manufacturer/Shunt Resistor Part Number | Shunt Resistor Type | Shunt Resistance | Maximum RMS Current | Motor Power Range 120Vac to 440Vac |           |

|-----------------------------------------|---------------------|------------------|---------------------|------------------------------------|-----------|

|                                         |                     | mΩ               | A                   | hp                                 | kW        |

| KOA/CSR Series                          | Four-terminal       | 5                | 7                   | 1.8 to 6.7                         | 1.4 to 5  |

| Isabellenhütte/BVS Series               | Two-terminal        |                  |                     |                                    |           |

| Vishay/WSL4026 Series                   | Four-terminal       | 2                | 17                  | 4 to 17                            | 3 to 13   |

| Isabellenhütte/BVE Series               | Two-terminal        |                  |                     |                                    |           |

| KOA/PSG4 Series                         | Four-terminal       | 1                | 35                  | 9 to 36                            | 7 to 27   |

| KOA/PSB Series                          | Two-terminal        |                  |                     |                                    |           |

| Isabellenhütte/BVR Series               | Four-terminal       | 0.5              | 70                  | 19 to 72                           | 14 to 54  |

| KOA/PSJ2 Series                         | Two-terminal        |                  |                     |                                    |           |

| Vishay/WSLP3921L2                       | Two-Terminal        | 0.2              | 177                 | 49 to 181                          | 37 to 135 |

| Vishay/WSLP5931L1                       | Two-Terminal        | 0.1              | 354                 | 99 to 362                          | 74 to 270 |

シャント抵抗を実装するための PC 基板レイアウトを行う際、いくつかの点に注意が必要です。抵抗器へのケルビン接続は、抵抗器本体の下で行い、互いに近接させて絶縁型変調器の入力まで引いてきます。これにより、接続配線のループ面積が最小になり、測定信号に対する浮遊磁界の干渉が減少します。シャント抵抗が絶縁型変調器回路とは別の PC 基板に実装される場合、しっかりと巻かれたツイスト・ペア線で同じ効果を得ることができます。

また、PC 基板の複数の配線層を使用して電流容量を高めることができます。PC 基板の各層間で電流が分散しやすくなるよう、抵抗器の各非ケルビン端子のまわりに多数のメッキ貫通ビアを配置します。PC 基板は、各層に 2 オンス (70  $\mu$ m) または 4 オンス (140  $\mu$ m) の銅を使用しているので、電流容量は 20A を超えます。また、PC 基板上の導電トレースをかなり大きくしてヒート・シンクとして利用することにより、シャント抵抗の消費電力容量を改善することができます。負荷電流が PC 基板に入り出すビアを設けることもまた有効です。

## シャント抵抗の接続

図 14 に、絶縁型変調器にシャント抵抗を接続するための推奨方法を示します。ACPL-C799U の  $V_{IN+}$  はシャント抵抗の正端子に接続され、 $V_{IN-}$  が GND1 に接続されていることから、電源リターン・バスは、シャント抵抗の負端子への検出ラインとして働きます。これにより、1 対のワイヤまたは PC 基板トレースで絶縁型変調器回路にシャント抵抗を接続することができます。シャント抵抗の負側への入力回路を基準とすることにより、抵抗器上の負荷電流によって生じる過渡ノイズが同相電圧に見えるため、電流検出信号を妨害しません。このことは、モータ駆動回路に流れ大きな負荷電流に加え、回路配線が持つ寄生インダクタンスにより生じるノイズ・スパイクとオフセットが、シャント抵抗の両端で測定される小さい電圧と比較して大きいので重要です。

ゲート駆動回路と電流検出回路の両方に同じ電源を使用する場合、絶縁型変調器の GND1 からシャント抵抗への配線が、ゲート駆動電源グランドへの唯一の電流リターン・バスであることが、グランド・ループの問題の可能性をなくすためにきわめて重要です。絶縁型変調器回路とゲート駆動回路の間で唯一直接接続しても構わるのは、正電源ラインのみです。

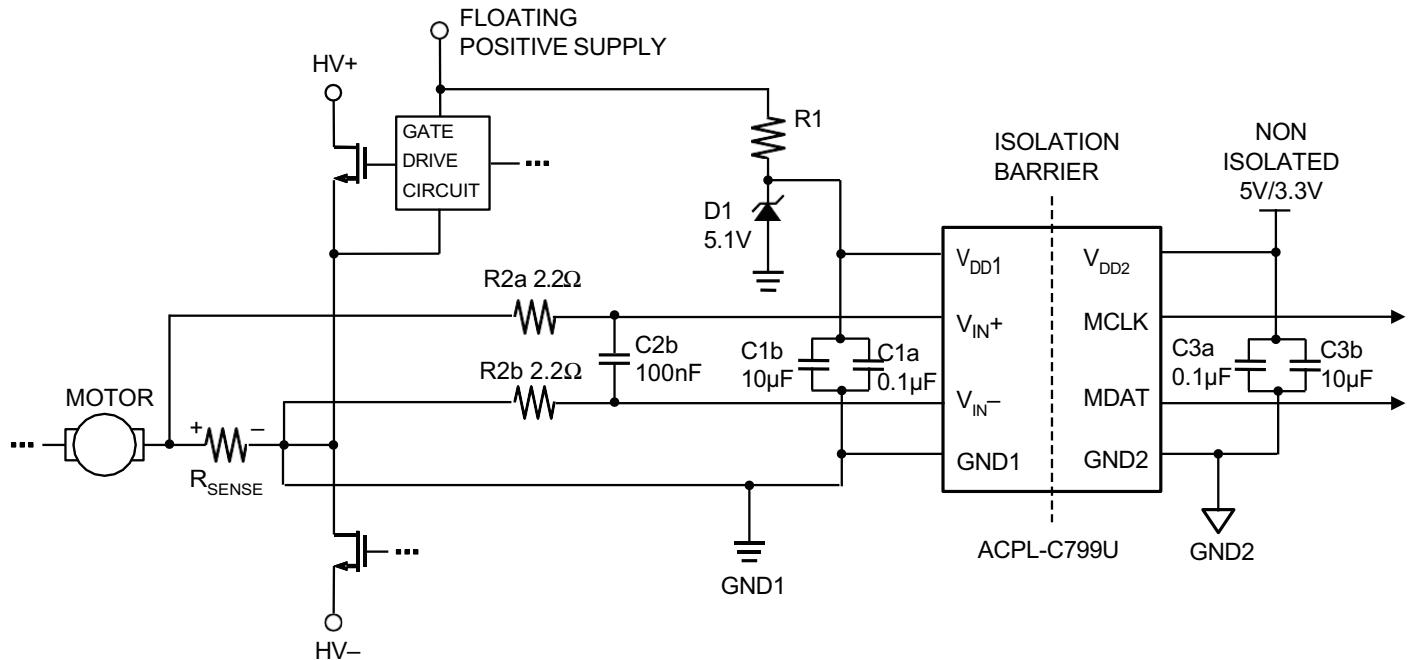

しかしながら、用途により、電源リターン・バスに流れる電源電流が、オフセットまたはノイズの問題を引き起こすことがあります。その場合、図 16 のように、 $V_{IN+}$  と  $V_{IN-}$  を 2 本の配線でシャント抵抗の両端に直接接続し、電源リターン・バス用には別の第 3 の配線で GND1 をシャント抵抗に接続することにより性能を高めることができます。完全差動アンプの同相により両方のピンに生じる入力電流は、フィルタ抵抗 (R2a と R2b) 上で釣り合い、相殺されます。片方のピンで発生したノイズは、コンデンサ C2 により、もう片方のピンにカッピングされ同相ノイズだけが発生しますが、このノイズはデバイスにより排除されます。このように接続したとき、両方の入力ピンがバイパスされます。検出信号に対する電磁障害を最小にするため、絶縁型変調器にシャント抵抗を接続するすべての配線 (2 線または 3 線方式) は、ツイスト・ペア線または PC 基板上の近接トレースとします。

図 16 : Schematic for Three-Conductor Shunt Connection

入力ラインに直列に接続された図 14 の抵抗  $R_2$  や図 16 の  $R_{2a}$  および  $R_{2b}$  は、入力バイパス・コンデンサ  $C_2$  と共にローパス・アンチエイリアシング・フィルタを構成します。また、これらの抵抗には別の重要な機能があります。シャント抵抗、入力バイパス・コンデンサ、そしてこれらを接続するワイヤまたはトレースのインダクタンスからなる回路にはリンクギングが発生する場合がありますが、前述の抵抗はこのリンクギングを減衰させます。入力回路に生じた入力サンプリング周波数付近のリンクギングが、未減衰のまま残っていると、ベースバンドにエイリアスし、デバイス出力に疑似ノイズが発生する場合があります。

## アナログ入力

ACPL-C799U フロントエンドには、完全差動アンプに続いてシグマ-デルタ変調器が含まれます。完全差動アナログ入力は  $\pm 50$  mV (フルスケール  $\pm 80$  mV) の信号を受け入れ、これは、モータ相電流検出などの用途において、シャント電流検出抵抗や他の低レベル信号ソースに直接接続するのに理想的です。フルスケール範囲 ( $\pm 80$  mV) 内であれば、より広い入力範囲 (たとえば、 $\pm 75$  mV) を使用し、過電流または過負荷検出することができます。

## ラッチアップの検討

特に頻繁に過渡ノイズを受けるような信号源に直接接続する用途では、CMOS デバイスのラッチアップに対するリスクを慎重に検討する必要があります。ACPL-C799U のアナログ入力回路は、モータ駆動や他の電力インバータ・システムなどのノイズの多い環境でしばしば遭遇する過渡やサージからの回復が早くなるように設計されています。

短絡や過負荷を含む他の状況は、入力への過渡電圧の原因となる可能性があります。ACPL-C799U は、アナログ入力に対して最大  $-2$  V の DC 電圧と、最大  $-6$  V の 2 秒過渡電圧で検証され、ラッチアップもデバイス破損もありません。

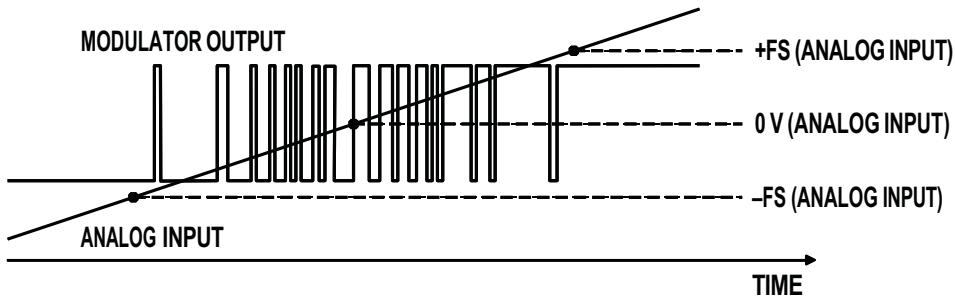

## 変調器データ出力とデジタル・フィルタ

入力信号情報は、1と0の密度によって表された変調器出力データ・ストリームに含まれます。図17に示すように、1の密度は入力信号電圧に比例します。0Vの差動入力信号は、理想的には1と0が等しい密度のデータ・ストリームを生成します。データ・ストリームでは、-50 mVの差動入力は、18.75%の1密度に対応し、+50mVの差動入力は、81.25%の1密度によって表されます。差動入力が +80 mV 以上では、理想的にはデータ・ストリームがすべて1になり、-80 mV 未満の入力は理想的にはすべてゼロになります。表12はこの関係を示します。

図17：Modulator Output vs. Analog Input

表12：Input Voltage with Ideal Corresponding Density of 1s at Modulator Data Output and ADC Code

| Analog Input             | Voltage Input | Density of 1s | ADC Code (16-bit unsigned decimation) |

|--------------------------|---------------|---------------|---------------------------------------|

| +Full-Scale              | +80 mV        | 100%          | 65,535                                |

| +Recommended Input Range | +50 mV        | 81.25%        | 53,248                                |

| Zero                     | 0 mV          | 50%           | 32,768                                |

| -Recommended Input Range | -50 mV        | 18.75%        | 12,288                                |

| -Full-Scale              | -80 mV        | 0%            | 0                                     |

### 注：

1. With a bipolar offset binary coding scheme, the digital code begins with digital 0 at -FS input and increases proportionally to the analog input until the full-scale code is reached at the +FS input. The zero crossing occurs at the mid-scale input.

2. The ideal density of 1s at modulator data output can be calculated with  $V_{IN}/160 \text{ mV} + 50\%$ ; similarly, the ADC code can be calculated with  $(V_{IN}/160 \text{ mV}) \times 65,536 + 32,768$ , assuming a 16-bit unsigned decimation filter.

デジタル・フィルタは、変調器からのシングルビット・データ・ストリームを、一般的な A/D コンバータのデジタル出力と同様なマルチビット出力ワードに変換します。この変換により、ワード出力のデータ・レートも減少します（デシメーション）。ACPL-C799Uと一緒に Sinc3 フィルタを使用することを推奨します。256 デシメーション比と 16 ビット・ワード設定の場合、出力データ・レートは 39 kHz (= 10 MHz/256) です。このフィルタは、ASIC、FPGA または DSP で実現できます。いくつかの ADC コードと、それらに対応する入力電圧を表12に示します。

## 電源とバイパス

図 14 に示すように、フローティング電源（多くの用途で、ハイサイド・パワートランジスタを駆動するために使用されたものと同じ電源）は、シンプルなツエナー・ダイオード（D1）を使用して 5V に調整することができます。このとき、抵抗 R1 の値は、既存のフローティング電源からの十分な電流の供給を確保できるように選択する必要があります。電流検出抵抗、つまりシャント（ $R_{SENSE}$ ）からの電圧信号は、RC アンチエイリアシング・フィルタ（R2 と C2）を介して、ACPL-C799U の入力に印加されます。最後に、ACPL-C799U からのクロックとデータ出力がデジタル・フィルタに接続されます。応用回路は比較的シンプルですが、最適な性能を得るには、いくつかの注意点があります。

絶縁型変調器の電源は、ほとんどの場合、パワートランジスタのゲート駆動回路に給電するために使用されるものと同じ電源から供給されます。専用の電源が必要な場合は、通常、既存のトランスに、追加の巻線を加えて得ることができます。或いは、ライン電源トランスや高周波 DC-DC コンバータなど、何らかのシンプルな絶縁型電源を使用できます。

また、フローティング電源電圧を 5V に削減するために 3 端子レギュレータを使用することもできます。電源の高周波ノイズやリップルを低減するため、抵抗またはインダクタを、レギュレータの入力と直列に使用することにより、レギュレータの入力バイパス・コンデンサとともにローバス・フィルタを形成することができます。

図 14 に示すバイパス・コンデンサ（C1a、C1b、および C3a）は、絶縁型変調器の入力および出力電源ピンの可能なかぎり近くに配置する必要があります。バイパス・コンデンサが必要となるのは、絶縁型変調器内部の信号が高速デジタルであるからです。より適切にフィルタリングするために、1  $\mu$ F ~ 10  $\mu$ F のコンデンサ（C3b）を追加して使用できます。

入力バイパス・コンデンサ C2 の場合は、高周波ノイズが低い周波数にエイリアシングして入力信号に干渉するのを防ぐためにアンチエイリアシング・フィルタの一部にもなります。

## PC 基板レイアウト

プリント回路基板（PCB）のレイアウト設計は、バイパス・コンデンサをできるだけ電源ピンの近くに配置すること、出力信号ラインを入力信号ラインから遠ざけること、グランドと電源をプレーンにすることなどを考慮してください。さらに、PCB レイアウトにおける、主に入力回路と出力回路間の浮遊容量結合が、絶縁型変調器のアイソレーション過渡耐性（CMR）に影響を及ぼすことがあります。最適な CMR 性能を得るため、PC 基板レイアウトにおいて、回路の入力側と出力側の間の距離を最大限離し、グランド・プレーンやパワー・プレーンを絶縁型変調器の本体の真下を通さず、またパッケージ・ボディ下に広げないようにすることにより、浮遊容量結合が最小になるようにしてください。

Copyright © 2024 Broadcom. All Rights Reserved. 用語「Broadcom」は、Broadcom Inc. および/またはその子会社を指します。 詳細については、[jp.broadcom.com](http://jp.broadcom.com) をご覧ください。 本書に記載された商標、商標名、サービス・マーク、ロゴはすべて、各社が所有権を有しています。

Broadcom は、信頼性、機能または設計を改善するために、本書の製品またはデータを通知なしに変更する権利を留保します。 Broadcom によって提供される情報の正確さと信頼性には細心の注意を払っています。 しかしながら、Broadcom は、この情報の適用または使用、あるいは本書に記載された製品または回路の適用または使用から生じるいかなる責任も負わず、特許権や他の権利によるいかなるライセンスも譲渡しません。