### ACFJ-332B

## Industrial Dual-Channel High-Speed Gate Drive Optocoupler for MOSFET/GaN with Rail-to-Rail Output Voltage in SO-24 Package

### **Overview**

The Broadcom ACFJ-332B driver is a dual-channel, high-speed, rail-to-rail output gate drive optocoupler, which comes in a compact, surface-mountable SO-24 package with two independent isolated channels for space savings. It provides an isolation voltage of 5000  $\rm V_{RMS}$  between input and output channels and functional isolation voltage up to 700  $\rm V_{RMS}$  between two output channels.

The ACFJ-332B operates with a wide range of input voltage and driver output voltage. It also offers enhanced features such as an input buffer drive with TTL and CMOS compatible logics, an enable pin (EN) to support a system functional safety requirement, programmable dead time between two driver channels, and input power supply under-voltage lockout protection to drive MOSFET/GaN at high-frequency DC-DC and AC-DC converters.

The Broadcom isolation products provide reinforced insulation and reliability that deliver safe signal isolation critical in high-temperature industrial applications.

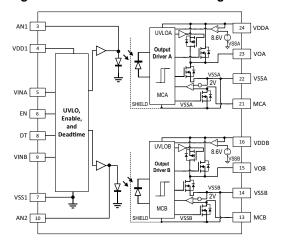

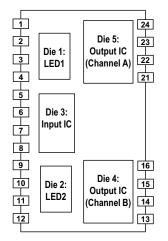

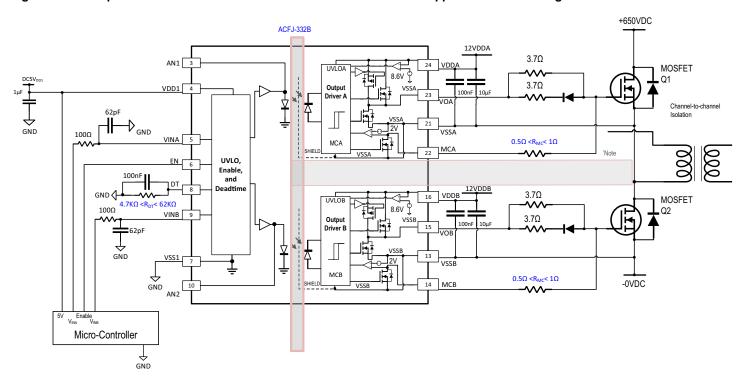

Figure 1: ACFJ-332B Functional Diagram

### **Features**

- Industrial temperature range: –40°C to +125°C

- Wide operating supply range:

- VDD1 range: 3.0V to 5.5V

- VDDA and VDDB range: 10V to 25V

- Low supply current allows bootstrap half-bridge topology

- TTL and CMOS compatible inputs

- EN pin for enhanced safety feature

- Programmable dead time

- Under-voltage lockout (UVLO) protection with hysteresis:

- VDD1 UVLO: 2.7V

- VDDA and VDDB UVLO: 8.6V

- Rail-to-rail output driver voltage

- Minimum peak output current: ±2.4A

- Minimum Miller clamp sinking current: 1A

- Maximum propagation delay: 65 ns

- Maximum channel-to-channel skew: 15 ns

- High noise immunity

- Common mode transient immunity (CMTI): 150 kV/μs at V<sub>CM</sub> = 1500V

- Dual isolated channels in SO-24 package with 8.3-mm creepage and clearance

- 3.5-mm creepage between two output drivers

- Worldwide safety approvals:

- UL/cUL 1577 5000 V<sub>RMS</sub> for 1 minute

- IEC/EN 60747-5-5  $V_{IORM}$  = 1414  $V_{PEAK}$

### **Applications**

- Power supply and EV charging

- Renewable energy inverter and storage

- Motor drive for industrial automation and robotics

CAUTION!

Take normal static precautions in the handling and assembly of this component to prevent damage, degradation, or both that might be induced by ESD. The components featured in this data sheet are not to be used in military or aerospace applications or environments. The component is not AEC-Q100 qualified and not recommended for automotive applications.

## **Ordering Information**

| Part Number | Option (RoHS Compliant) | Package | Surface Mount | Tape and Reel | IEC 60747-5-5 | Output Driver<br>UVLO Level | Quantity     |

|-------------|-------------------------|---------|---------------|---------------|---------------|-----------------------------|--------------|

| ACFJ-332B   | -000E                   | SO-24   | X             |               | X             | 8V                          | 45 per tube  |

|             | -500E                   |         | Х             | X             | X             |                             | 850 per reel |

To order, choose a part number from the part number column and combine with the desired option from the option column to form an order entry.

#### Example:

ACFJ-332B-500E to order a product with an output UVLO voltage of 8V, SO-24 surface-mount package in tape and reel packaging with IEC 60747-5-5 Safety Approval in RoHS compliant.

Option data sheets are available. Contact your Broadcom sales representative or authorized distributor for information.

## **Package Outline Drawing**

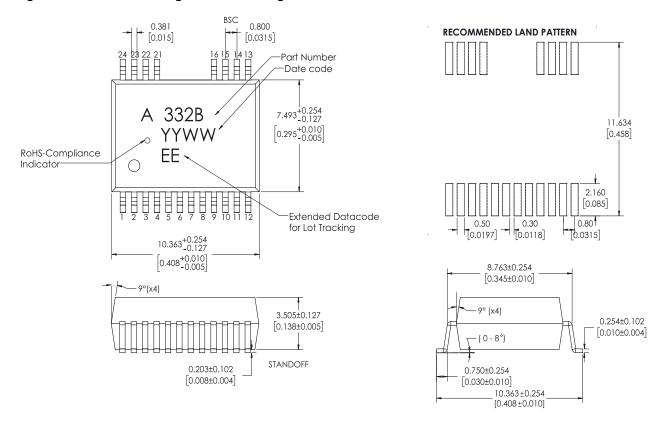

Figure 2: ACFJ-332B Package Outline Drawing

#### NOTE:

- Dimensions are in millimeters (inches).

- Lead coplanarity = 0.10 mm (0.004 inches), Mold Flash on each side = 0.203 mm (0.008 inches) max.

Customers should contact their PCB manufacturers for solder-mask tolerance between and around signal pads.

### **Recommended PB-Free IR Profile**

Recommended reflow condition as per JEDEC Standard, J-STD-020 (latest revision).

**NOTE:** Non-halide flux should be used.

## **Product Overview Description**

The ACFJ-332B (shown in Figure 1) is a dual-channel, high-speed, rail-to-rail output isolated MOSFET/GaN gate driver in a compact SO-24 package. The ACFJ-332B is designed with many enhanced features to enable seamless integration with control circuitry and support functional safety requirements.

It can operate over wide input supply VDD1 range of 3V to 5.5V and driver output supply VDDA and VDDB range of 10V to 25V. Both input and output supplies have under-voltage lockout protection, whereby when UVLO protection is triggered, both output drivers (VOA and VOB) are pulled to low state. With the dead time control disabled, its respective input pins (VINA and VINB) can control the dual isolated output drivers independently without an external buffer, since the two input pins (VINA and VINB) are TTL and CMOS logic levels compatible. By connecting an external resistor to the DT pin, the dead time control feature is functional. The output drivers are now configured as a pair of half-bridge drivers, with desired dead time interval inserted between the two channels.

An enable (EN) logic control is integrated inside the ACFJ-332B to allow hard shut down of the output drivers when it is pulled to a low state. When the enable pin is not connected, the ACFJ-332B is disabled via an internal 500-k $\Omega$  resistor pull down to VSS1.

With the enhanced features offered by the ACFJ-332B, it is ideal for use in gate driver applications that require flexibility in system integration and control, high common-mode noise immunity, active Miller current clamping, and high input-to-output isolation as well as channel-to-channel isolation.

## **Package Pinout and Descriptions**

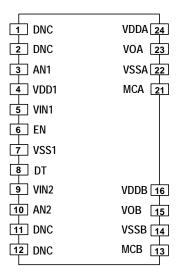

Figure 3: ACFJ-332B Pin Configuration

| Pin No. | Pin Name | Description                                                                                                                                                                                                                                                                                                                                                 |

|---------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | DNC      | Do not connect externally. This pin is connect to the IC lead frame.                                                                                                                                                                                                                                                                                        |

| 2       | DNC      | Do not connect externally. This pin is connect to the IC lead frame.                                                                                                                                                                                                                                                                                        |

| 3       | AN1      | Input LED1 anode. For testing purpose, do not connect to the external circuit.                                                                                                                                                                                                                                                                              |

| 4       | VDD1     | Input positive power supply.                                                                                                                                                                                                                                                                                                                                |

| 5       | VINA     | Input control signal for A-channel driver. VINA input is compatible to TTL/CMOS logic levels. This pin has an internal pull-down 500-k $\Omega$ resistor. Tie this pin to ground if it is not used.                                                                                                                                                         |

| 6       | EN       | Input enable pin. A logic high input for at least 50 ns enables both A channel and B channel drivers. This pin has an internal pull-down 500-k $\Omega$ resistor.                                                                                                                                                                                           |

| 7       | VSS1     | Input ground.                                                                                                                                                                                                                                                                                                                                               |

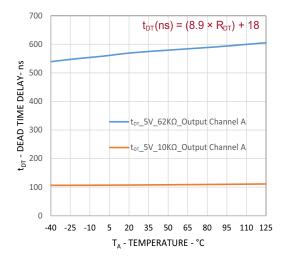

| 8       | DT       | Dead time input control. Connects a resistor (RDT) between the DT pin and the VSS1 pin to adjust dead time according to the equation: $t_{DT}$ in (ns) = $(8.9 \times R_{DT}) + 18$ , $R_{DT}$ in (k $\Omega$ ). Add a bypass ceramic capacitor of 0.1 $\mu$ F to the DT pin for noise filtering. If the DT feature is not in use, it must be tied to VDD1. |

| 9       | VINB     | Input control signal for B-channel driver. VINB input is compatible to TTL/CMOS logic. This pin has an internal pull-down 500-k $\Omega$ resistor. Tie this pin to ground if it is not in use.                                                                                                                                                              |

| 10      | AN2      | Input LED2 anode. For testing purpose, do not connect to the external circuit.                                                                                                                                                                                                                                                                              |

| 11      | DNC      | Do not connect externally. This pin is connected to the IC lead frame.                                                                                                                                                                                                                                                                                      |

| 12      | DNC      | Do not connect externally. This pin is connected to the IC lead frame.                                                                                                                                                                                                                                                                                      |

| 13      | MCB      | Miller clamp output for the B-channel driver. Connect the MCB pin to the VSSB pin if it is not in use.                                                                                                                                                                                                                                                      |

| 14      | VSSB     | B-channel output ground.                                                                                                                                                                                                                                                                                                                                    |

| 15      | VOB      | B channel Gate drive output.                                                                                                                                                                                                                                                                                                                                |

| 16      | VDDB     | B-channel positive power supply.                                                                                                                                                                                                                                                                                                                            |

| 21      | MCA      | Miller clamp output for the A-channel driver. Connect the MCA pin to the VSSA pin if it is not in use.                                                                                                                                                                                                                                                      |

| 22      | VSSA     | A-channel output ground.                                                                                                                                                                                                                                                                                                                                    |

| 23      | VOA      | A-channel Gate drive output.                                                                                                                                                                                                                                                                                                                                |

| 24      | VDDA     | A-channel positive power supply.                                                                                                                                                                                                                                                                                                                            |

# **Regulatory Information**

The ACFJ-332B is approved by the following organizations:

| UL/cUL | UL/cUL 1577, compliance with U.S. and Canadian requirements, component recognition program up to V <sub>ISO</sub> = |

|--------|---------------------------------------------------------------------------------------------------------------------|

|        | 5000 V <sub>RMS</sub> .                                                                                             |

| IEC/EN | IEC/EN 60747-5-5                                                                                                    |

|        | Maximum working insulation voltage, V <sub>IORM</sub> = 1414 V <sub>PEAK</sub>                                      |

|        | Highest allowable overvoltage, V <sub>IOTM</sub> = 8000 V <sub>PEAK</sub>                                           |

### **IEC/EN 60747-5-5 Insulation Characteristics**

| Description                                                                                                                                                      | Symbol                                                    | Characteristic     | Unit           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|--------------------|----------------|

| Insulation Classification per DIN VDE 0110/1.89, Table 1                                                                                                         |                                                           |                    |                |

| For Rated Mains Voltage ≤ 600 V <sub>RMS</sub>                                                                                                                   |                                                           | I – IV             |                |

| For Rated Mains Voltage ≤ 1000 V <sub>RMS</sub>                                                                                                                  |                                                           | I – III            |                |

| Climatic Classification                                                                                                                                          |                                                           | 40/125/21          |                |

| Pollution Degree (DIN VDE 0110/1.89)                                                                                                                             |                                                           | 2                  |                |

| Maximum Working Insulation Voltage                                                                                                                               | V <sub>IORM</sub>                                         | 1414               | $V_{PEAK}$     |

| Input to Output Test Voltage, Method b <sup>a</sup> $V_{IORM}$ x 1.875 = $V_{PR}$ , 100% Production Test with $t_m$ = 1 second, Partial Discharge < 5 pC         | V <sub>PR</sub>                                           | 2652               | $V_{PEAK}$     |

| Input to Output Test Voltage, Method $a^a$ $V_{IORM} \ x \ 1.6 = V_{PR}, \text{Type and Sample Test, } t_m = 10 \text{ seconds,}$ $Partial \ Discharge < 5 \ pC$ | V <sub>PR</sub>                                           | 2262               | $V_{PEAK}$     |

| Highest Allowable Overvoltage <sup>a</sup> (Transient Overvoltage t <sub>ini</sub> = 60 seconds)                                                                 | V <sub>IOTM</sub>                                         | 8000               | $V_{PEAK}$     |

| Safety-Limiting Values – maximum values allowed in the event of a failure <sup>b</sup> Case Temperature Input Current Output Power                               | T <sub>S</sub> I <sub>S,INPUT</sub> P <sub>S,OUTPUT</sub> | 175<br>400<br>1200 | °C<br>mA<br>mW |

| Insulation Resistance at T <sub>S</sub> , V <sub>IO</sub> = 500V                                                                                                 | R <sub>S</sub>                                            | > 10 <sup>9</sup>  | Ω              |

a. Refer to the optocoupler section of the Isolation and Control Components Designer's Catalog, under the Product Safety Regulation section IEC/EN 60747-5-5, for a detailed description of Method a and Method b partial discharge test profiles.

## **Insulation and Safety Related Specifications**

| Parameter                                         | Symbol | Value | Unit  | Conditions                                                                                                                         |

|---------------------------------------------------|--------|-------|-------|------------------------------------------------------------------------------------------------------------------------------------|

| Minimum External Air Gap (Clearance)              | L(101) | 8.3   | mm    | Measured from input terminals to output terminals, shortest distance through air.                                                  |

| Minimum External Tracking (Creepage)              | L(102) | 8.3   | mm    | Measured from input terminals to output terminals, shortest distance path along body.                                              |

| Minimum Internal Plastic Gap (Internal Clearance) |        | 0.5   | mm    | Through insulation distance conductor to conductor, usually the straight-line distance thickness between the emitter and detector. |

| Tracking Resistance (Comparative Tracking Index)  | CTI    | 400   | Volts | DIN IEC 112/VDE 0303 Part 1.                                                                                                       |

| Isolation Group                                   |        | II    | •     | Material Group (DIN VDE 0110).                                                                                                     |

b. Isolation characteristics are guaranteed only within the safety maximum ratings that must be ensured by protective circuits in application. Surface-mount classification is Class A in accordance with CECCOO802.

## **Absolute Maximum Ratings**

Unless otherwise specified, all voltages at input IC reference to  $V_{SS1}$ , all voltages at A-channel output IC reference to  $V_{SSA}$ , and all voltages at B-channel output IC reference to  $V_{SSB}$ .

| Parameter                                     | Symbol                                | Min.        | Max. | Unit | Note |

|-----------------------------------------------|---------------------------------------|-------------|------|------|------|

| Storage Temperature                           | T <sub>S</sub>                        | <b>–</b> 55 | 150  | °C   |      |

| Operating Temperature                         | T <sub>A</sub>                        | -40         | 125  | °C   |      |

| IC junction Temperature                       | T <sub>J</sub>                        | _           | 150  | °C   |      |

| Input Supply Voltage                          | V <sub>DD1</sub>                      | -0.3        | 6    | V    |      |

| Input Control Signal Voltage                  | VIN <sub>A</sub> , VIN <sub>B</sub>   | -0.3        | 6    | V    |      |

| Input Enable Voltage                          | V <sub>EN</sub>                       | -0.3        | 6    | V    |      |

| Dead Time Control Input Voltage               | V <sub>DT</sub>                       | -0.3        | 6    | V    |      |

| Output Supply Voltage                         | $V_{DDA}, V_{DDB}$                    | -0.3        | 30   | V    |      |

| Output Driver Voltage                         | $V_{OA}, V_{OB}$                      | -0.3        | 30   | V    |      |

| Miller Clamp Voltage                          | V <sub>MCA</sub> , V <sub>MCB</sub>   | -0.3        | 30   | V    |      |

| Peak Output Current                           | I <sub>OA</sub>  ,  I <sub>OB</sub>   | _           | 4    | Α    | а    |

| Peak Miller Clamp Current                     | I <sub>MCA</sub>  ,  I <sub>MCB</sub> | _           | 4    | Α    | а    |

| Channel-to-Channel Internal Isolation Voltage | V <sub>SSA</sub> – V <sub>SSB</sub>   | _           | 1414 | V    | 1    |

| Input IC Power Dissipation                    | P <sub>IN</sub>                       | _           | 150  | mW   | b    |

| Output IC Power Dissipation (one channel)     | P <sub>OUTA</sub> , P <sub>OUTB</sub> | _           | 400  | mW   | С    |

| Total Power Dissipation                       | P <sub>TOTAL</sub>                    | _           | 950  | mW   | d    |

- a. Maximum pulse width = 1  $\mu$ s, maximum duty = 0.7%. Operation conditions must not exceed the maximum IC junction temperature of  $T_{J(max)}$  = 150°C.

- b. Input IC power dissipation is derated linearly above 105°C from 150 mW to 100 mW at 125°C for the high effective thermal conductivity board. For the low effective thermal conductivity board, input IC power dissipation is derated linearly above 105°C from 150 mW to 70 mW at 125°C. See Thermal Resistance Model for ACFJ-332B for details.

- c. Each channel output IC power dissipation is limited to 400 mW. Output IC power dissipation is derated linearly above 105°C from 400 mW to 320 mW at 125°C for the high effective thermal conductivity board. For the low effective thermal conductivity board, output IC power dissipation is derated linearly above 105°C from 400 mW to 240 mW at 125°C. The PCB thermal resistance characteristic has to be considered so as not to exceed absolute maximum rating. See Thermal Resistance Model for ACFJ-332B for details.

- d. Total power dissipation is derated linearly above 105°C from 950 mW to 740 mW at 125°C for the high effective thermal conductivity board. For the low effective thermal conductivity board, the total IC power dissipation is derated linearly above 105°C from 950 mW to 550 mW at 125°C. See Thermal Resistance Model for ACFJ-332B for details.

## **Recommended Operating Conditions**

Unless otherwise specified, all voltages at input IC reference to  $V_{SS1}$ , all voltages at A-channel output IC reference to  $V_{SSA}$  and all voltages at B-channel output IC reference to  $V_{SSB}$ .

| Parameter                             | Symbol                                        | Min. | Max. | Unit | Note |

|---------------------------------------|-----------------------------------------------|------|------|------|------|

| Operating Temperature                 | T <sub>A</sub>                                | -40  | 125  | °C   |      |

| Input Supply Voltage                  | V <sub>DD1</sub>                              | 3    | 5.5  | V    |      |

| Output Supply Voltage                 | $V_{DDA}, V_{DDB}$                            | 10   | 25   | V    |      |

| Dead Time Resistor Range              | R <sub>DT</sub>                               | 10   | 62   | kΩ   | а    |

| Input IC Supply Decoupling Capacitor  | C <sub>VDD1</sub>                             | 1    | _    | μF   | b    |

| Output IC Supply Decoupling Capacitor | C <sub>VDDA</sub> , C <sub>VDDB</sub>         | 10   | _    | μF   | С    |

| Minimum Input Pulse Width             | t <sub>ON(VINA)</sub> , t <sub>ON(VINB)</sub> | 50   | _    | ns   | d    |

- a. The dead time ( $t_{DT}$ ) range is programmable from 110 ns to 572 ns using this formula:  $t_{DT}$  in (ns) = (8.9 ×  $R_{DT}$ ) + 18,  $R_{DT}$  in (k $\Omega$ ).

- b. Connect the input supply decoupling capacitor between  $\rm V_{\rm DD1}$  to  $\rm V_{\rm SS1}.$

- c. Connect the output supply decoupling capacitor between  $\rm V_{DDA}$  to  $\rm V_{SSA}$  and  $\rm V_{DDB}$  to  $\rm V_{SSB}$

- d. Minimum input pulse width for a guarantee output pulse under no load conditions.

## **Electrical and Switching Specifications**

Unless otherwise specified, all minimum and maximum specifications are at recommended operating conditions; all voltages at input IC reference to  $V_{SSA}$  and all voltages at B-channel output IC reference to  $V_{SSB}$ . All typical values at  $T_A = 25^{\circ}C$ ,  $V_{DD1} - V_{SS1} = 3.3V$  or 5V,  $V_{DDA} - V_{SSA} = 15V$ ,  $V_{DDB} - V_{SSB} = 15V$ . The DT pin is tied to  $V_{DD1}$  (DT disabled), except for the  $t_{DT}$  test.

| Parameter                                            | Symbol                                         | Min. | Тур. | Max. | Unit | Test Conditions                              | Fig. | Note |  |

|------------------------------------------------------|------------------------------------------------|------|------|------|------|----------------------------------------------|------|------|--|

| DC Specifications                                    |                                                |      |      |      |      |                                              |      |      |  |

| Supply Current                                       |                                                |      |      |      |      |                                              |      |      |  |

| Input Supply Current (Quiescent)                     | I <sub>VDD1</sub>                              | _    | 1.5  | 2.7  | mA   | VIN <sub>A</sub> = 0V, VIN <sub>B</sub> = 0V | 24   |      |  |

| Input Supply Current at Operation (per channel)      | I <sub>VDD1_SW</sub>                           | _    | 6.3  | _    | mA   | f = 200 kHz,<br>Duty cycle = 50%             |      |      |  |

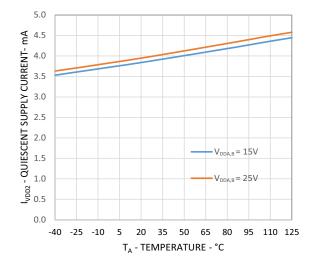

| Output Supply Current (Quiescent per channel)        | $I_{VDDA}$ , $I_{VDDB}$                        | _    | 4    | 5.9  | mA   | VIN <sub>A</sub> = 0V, VIN <sub>B</sub> = 0V | 25   |      |  |

| Output Supply Current at Operation (per channel)     | I <sub>VDDA_SW</sub> ,<br>I <sub>VDDB_SW</sub> | _    | 4.4  | _    | mA   | f = 200 kHz,<br>Duty cycle = 50%,<br>No load |      |      |  |

| V <sub>DD1</sub> UVLO Threshold                      |                                                |      |      |      |      |                                              |      |      |  |

| V <sub>DD1</sub> UVLO Threshold Voltage, Low to High | V <sub>UV1_TH+</sub>                           | 2.4  | 2.7  | 2.95 | V    |                                              |      |      |  |

| V <sub>DD1</sub> UVLO Threshold Voltage, High to Low | V <sub>UV1_TH</sub> _                          | 2.2  | 2.5  | 2.75 | V    |                                              |      |      |  |

| V <sub>DD1</sub> UVLO Hysteresis                     | V <sub>UV1_HYS</sub>                           | _    | 0.2  | _    | V    |                                              |      |      |  |

| Parameter                                                                   | Symbol                                             | Min. | Тур.                      | Max. | Unit | Test Conditions                                           | Fig. | Note |

|-----------------------------------------------------------------------------|----------------------------------------------------|------|---------------------------|------|------|-----------------------------------------------------------|------|------|

| V <sub>DDA</sub> and V <sub>DDB</sub> UVLO Threshold (8V UVL                | O Version)                                         | •    | <u> </u>                  | I    | ı    |                                                           |      | 1    |

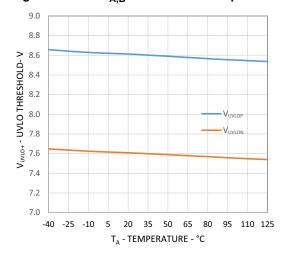

| ${ m V}_{ m DDA}$ and ${ m V}_{ m DDB}$ UVLO Threshold Voltage, Low to High | V <sub>UVLOA_TH+</sub> ,<br>V <sub>UVLOB_TH+</sub> | 8.1  | 8.6                       | 9.1  | V    |                                                           | 16   |      |

| ${ m V}_{ m DDA}$ and ${ m V}_{ m DDB}$ UVLO Threshold Voltage, High to Low | V <sub>UVLOA_TH</sub> ,<br>V <sub>UVLOB_TH</sub>   | 7.1  | 7.6                       | 8.1  | V    |                                                           | 16   |      |

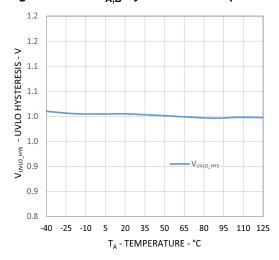

| V <sub>DDA</sub> and V <sub>DDB</sub> UVLO Hysteresis                       | V <sub>UVLOA_HYS</sub> ,<br>V <sub>UVLOB_HYS</sub> | _    | 1.0                       | _    | V    |                                                           | 17   |      |

| Input Control Threshold (VIN <sub>A</sub> , VIN <sub>B</sub> , EN)          |                                                    | •    | <u>'</u>                  | •    |      |                                                           | *    |      |

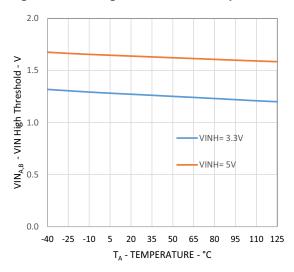

| Input Control High Threshold Voltage                                        | VIN <sub>AH</sub> , VIN <sub>BH</sub>              | 2    | _                         | _    | V    |                                                           | 18   |      |

| Input Control Low Threshold Voltage                                         | VIN <sub>AL</sub> , VIN <sub>BL</sub>              | _    | _                         | 0.8  | V    |                                                           | 19   |      |

| Enable High Threshold Voltage                                               | V <sub>ENH</sub>                                   | 2    | _                         | _    | V    |                                                           | 22   |      |

| Enable Low Threshold Voltage                                                | V <sub>ENL</sub>                                   | _    | _                         | 8.0  | V    |                                                           | 23   |      |

| Gate Driver Output (V <sub>OA</sub> , V <sub>OB</sub> )                     |                                                    |      |                           |      |      |                                                           |      | 1    |

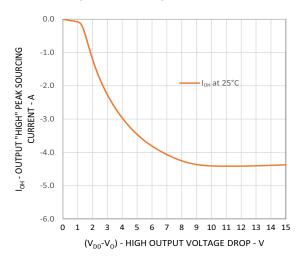

| Output High Peak Sourcing Current                                           | I <sub>OAH</sub> , I <sub>OBH</sub>                | _    | -4.0                      | -2.5 | Α    | $V_{DDA} - V_{OA} = 15V,$ $V_{DDB} - V_{OB} = 15V$        |      | а    |

| Output Low Peak Sinking Current                                             | I <sub>OAL</sub> , I <sub>OBL</sub>                | 2.4  | 4.0                       | _    | Α    | $V_{OA} - V_{SSA} = 15V,$<br>$V_{OB} - V_{SSB} = 15V$     |      | а    |

| Output High Transistor on Resistance, R <sub>DS(ON)</sub>                   | R <sub>OAH</sub> , R <sub>OBH</sub>                | _    | 15                        | _    | Ω    | $I_{OA} = -10 \text{ mA},$<br>$I_{OB} = -10 \text{ mA}$   |      |      |

| Output Low Transistor on Resistance, R <sub>DS(ON)</sub>                    | R <sub>OAL</sub> , R <sub>OBL</sub>                | _    | 1.2                       | _    | Ω    | I <sub>OA</sub> = 10 mA,<br>I <sub>OB</sub> = 10 mA       |      |      |

| High Level Output Voltage                                                   | V <sub>OAH</sub> , V <sub>OBH</sub>                | _    | V <sub>DDA,B</sub> – 0.15 | _    | V    | $I_{OA} = -10 \text{ mA},$<br>$I_{OB} = -10 \text{ mA}$   |      |      |

| Low Level Output Voltage                                                    | V <sub>OAL</sub> , V <sub>OBL</sub>                | _    | 0.01                      | _    | V    | I <sub>OA</sub> = 10 mA,<br>I <sub>OB</sub> = 10 mA       |      |      |

| Clamp Parameters                                                            |                                                    | I    |                           |      |      |                                                           | -    | 1    |

| Clamp Threshold Voltage                                                     | V <sub>MCA_TH</sub> ,<br>V <sub>MCB_TH</sub>       | 1.5  | 1.8                       | 2.1  | V    |                                                           |      |      |

| Clamp Low Peak Sinking Current                                              | I <sub>MCAL</sub> , I <sub>MCBL</sub>              | 1.0  | 2.2                       | _    | Α    | $V_{MCA} = V_{SSA} + 3.5V,$<br>$V_{MCB} = V_{SSB} + 3.5V$ |      |      |

| Parameter                                                                                       | Symbol               | Min. | Тур. | Max. | Unit  | Test Conditions                                                                     | Fig. | Note |

|-------------------------------------------------------------------------------------------------|----------------------|------|------|------|-------|-------------------------------------------------------------------------------------|------|------|

| AC Specifications                                                                               |                      |      | 1    |      | - II  |                                                                                     |      |      |

| V <sub>DD1</sub> - V <sub>SS1</sub> = 5V                                                        |                      |      |      |      |       | Rg(external) = $4.7\Omega$ ,                                                        |      |      |

| Propagation Delay Time from VIN <sub>A,B</sub> to V <sub>OA,B</sub> , Low to High (per channel) | t <sub>PLH</sub>     | _    | 35   | 65   | ns    | Cload = 2.2 nF,<br>f = 200 kHz,<br>Duty cycle = 50%                                 |      |      |

| Propagation Delay Time from VIN <sub>A,B</sub> to V <sub>OA,B</sub> , High to Low (per channel) | t <sub>PHL</sub>     | _    | 40   | 65   | ns    |                                                                                     |      |      |

| V <sub>DD1</sub> - V <sub>SS1</sub> = 3.3V                                                      |                      |      |      | 1    |       |                                                                                     |      |      |

| Propagation Delay Time from VIN <sub>A,B</sub> to V <sub>OA,B</sub> , Low to High (per channel) | t <sub>PLH</sub>     | _    | 40   | 70   | ns    | -                                                                                   |      |      |

| Propagation Delay Time from $VIN_{A,B}$ to $V_{OA,B}$ , High to Low (per channel)               | t <sub>PHL</sub>     | _    | 43   | 70   | ns    |                                                                                     |      |      |

| V <sub>DD1</sub> – V <sub>SS1</sub> = 3.3V or 5V                                                |                      |      | 1    | 1    |       |                                                                                     |      |      |

| Pulse Width Distortion (t <sub>PHL</sub> – t <sub>PLH</sub> )                                   | PWD                  | -22  | _    | 22   | ns    |                                                                                     |      | b    |

| Dead Time Distortion Caused by Any Two<br>Parts (t <sub>PLH</sub> – t <sub>PHL</sub> )          | DTD                  | -26  | _    | 26   | ns    |                                                                                     |      | С    |

| Channel-to-Channel Skew                                                                         | t <sub>CSK</sub>     | -15  | _    | 15   | ns    |                                                                                     |      | d    |

| Output 20% to 80% Rise Time (per channel)                                                       | t <sub>R</sub>       | _    | 10   | 17   | ns    |                                                                                     |      |      |

| Output 80% to 20% Fall Time (per channel)                                                       | t <sub>F</sub>       | _    | 10   | 18   | ns    |                                                                                     |      |      |

| Output High Level Common Mode Transient Immunity                                                | CM <sub>H</sub>      | 150  | _    | _    | kV/μs | $VIN_A = VIN_B = 5V$ $V_{DDA} = V_{DDB} = 15V$ $V_{CM} = 1500V$ $T_A = 25^{\circ}C$ |      | е    |

| Output Low Level Common Mode Transient Immunity                                                 | CM <sub>L</sub>      | 150  | _    | _    | kV/µs | $VIN_A = VIN_B = 0V$ $V_{DDA} = V_{DDB} = 15V$ $V_{CM} = 1500V$ $T_A = 25^{\circ}C$ |      | f    |

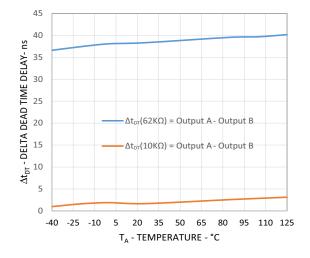

| Dead Time Programming (Design Value Set                                                         | by R <sub>DT</sub> ) | ·    | •    |      |       |                                                                                     |      |      |

| Dead Time                                                                                       | t <sub>DT</sub>      | _    | 110  | _    | ns    | R <sub>DT</sub> = 10 kΩ                                                             |      | g    |

|                                                                                                 |                      | _    | 572  | _    | ns    | $R_{DT}$ = 62 k $\Omega$                                                            |      | g    |

|                                                                                                 |                      |      |      | *    |       |                                                                                     |      |      |

- a. Short circuit pulsed current at  $V_{DD}$   $V_{SS}$  = 15V and pulse duration less than 1  $\mu$ s.

- b. Pulse width distortion (PWD) is defined as t<sub>PHL</sub> t<sub>PLH</sub> for any given device.

- c. Dead time distortion (DTD) is defined as t<sub>PLH</sub> t<sub>PHL</sub> between any two parts under the same test condition. A negative DTD reduces original system dead time, while a positive DTD increases original system dead time.

- d. Channel-to-channel skew ( $t_{CSK}$ ) is defined as propagation delay difference between two channels under the same test conditions.

- e. Common mode transient immunity in the high state is the maximum tolerable  $dV_{CM}/dt$  of the common mode pulse,  $V_{CM}$ , to ensure that the output will remain in the high state (that is,  $V_O > 12V$ ).

- f. Common mode transient immunity in a low state is the maximum tolerable  $dV_{CM}/dt$  of the common mode pulse,  $V_{CM}$ , to ensure that the output will remain in a low state (that is,  $V_O < 1.0V$ ).

- g. Dead time is measured at the gate driver outputs,  $V_{OA}$  and  $V_{OB}$ . The measured dead time value includes the effect of dead time distortion (DTD):  $t_{DT}$  in (ns) = (8.9 ×  $R_{DT}$ ) + 18,  $R_{DT}$  in (k $\Omega$ ).

## **Package Characteristics**

| Parameter                                | Symbol           | Min. | Тур.             | Max. | Unit             | Test Conditions                               | Note    |

|------------------------------------------|------------------|------|------------------|------|------------------|-----------------------------------------------|---------|

| Input-Output Momentary Withstand Voltage | V <sub>ISO</sub> | 5000 | _                | _    | V <sub>RMS</sub> | RH < 50%, t = 1 min.<br>T <sub>A</sub> = 25°C | a, b, c |

| Resistance (Input-Output)                | R <sub>I-O</sub> | _    | 10 <sup>14</sup> | _    | Ω                | V <sub>I-O</sub> = 500 Vdc                    | С       |

| Capacitance (Input-Output)               | C <sub>I-O</sub> | _    | 0.9              | _    | pF               | f = 1 MHz                                     |         |

- a. In accordance with UL1577, each optocoupler is proof-tested by applying an insulation test voltage ≥ 6000 V<sub>RMS</sub> for 1 second.

- b. The Input-Output Momentary Withstand Voltage is a dielectric voltage rating that should not be interpreted as an input-output continuous voltage rating. For the continuous voltage, ratings refer to your equipment level safety specification or the IEC/EN 60747-5-5 Insulation Characteristics table.

- c. Device is consider as a two-terminal device: pins 1 to 12 shorted together and pins 13 to 24 shorted together.

### **Parameter Measurements**

Figure 4 depicts the test setup to measure the gate driver's propagation delay. These settings correlate to the loading effects found in most automotive applications.

Figure 4: Propagation Delay Measurement Test Setup

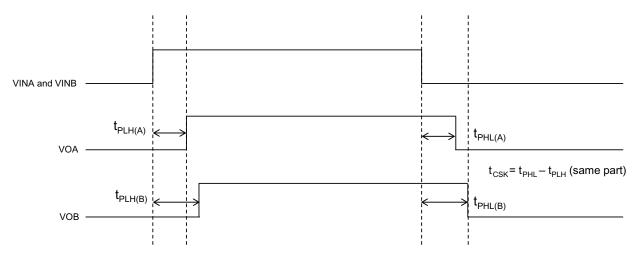

Figure 5 shows the propagation delay measurements and reference waveforms with dead time feature disabled from the test setup shown in Figure 4.

Figure 5: Propagation Delay Waveforms with Dead Time Disabled (DT Is Tied to VDD1)

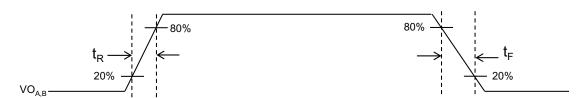

Figure 6 shows the 20% to 80% rise and fall time measurement.

Figure 6: Rise and Fall Time Measurement

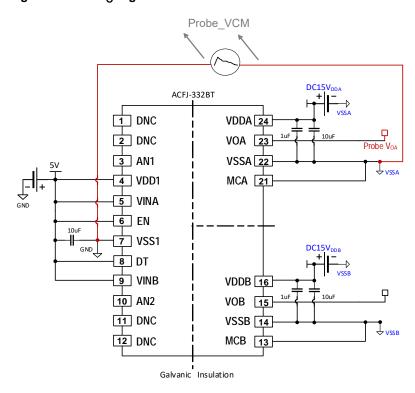

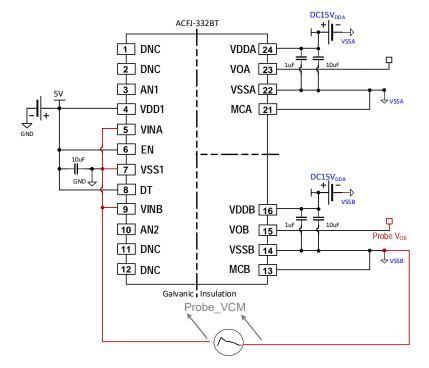

The common mode rejection test circuitries are shown in the following figures. Both CMR High (Figure 7) and Low (Figure 8)  $V_O$  are probed in the presence of  $V_{CM}$  at 1500V.

Figure 7: CMR V<sub>O</sub> High Test Circuit

Figure 8: CMR V<sub>O</sub> Low Test Circuit

## **Thermal Resistance Model for ACFJ-332B**

The diagram for measurement is shown in Figure 9. This is a multichip package with five heat sources. The effect of heating of one die due to the adjacent dice are considered by applying the theory of linear superposition. Here, one die is heated first and the temperatures of all the dice are recorded after thermal equilibrium is reached. Then, the second die is heated and all the dice temperatures are recorded and so on, until the fifth die is heated. With the known ambient temperature, die junction temperature, and power dissipation, the resultant thermal resistance can then be determined. The thermal resistance calculation can be casted into a 5-by-5 matrix form from the five heat sources.

Figure 9: Diagram of ACFJ-332B for Thermal Resistance Model

| R <sub>11</sub> | R <sub>12</sub> | R <sub>13</sub> | R <sub>14</sub>                                       | R <sub>15</sub> |   | P <sub>1</sub> |   | T <sub>1</sub> |

|-----------------|-----------------|-----------------|-------------------------------------------------------|-----------------|---|----------------|---|----------------|

| R <sub>21</sub> | $R_{22}$        | $R_{23}$        | R <sub>24</sub><br>R <sub>34</sub><br>R <sub>44</sub> | R <sub>25</sub> |   | P <sub>2</sub> |   | $T_2$          |

| R <sub>31</sub> | $R_{32}$        | $R_{33}$        | $R_{34}$                                              | $R_{35}$        | • | P <sub>3</sub> | = | $T_3$          |

| R <sub>41</sub> | R <sub>42</sub> | R <sub>43</sub> | R <sub>44</sub>                                       | R <sub>45</sub> |   | $P_4$          |   | $T_4$          |

| R <sub>51</sub> | R <sub>52</sub> | R <sub>53</sub> | R <sub>54</sub>                                       | R <sub>55</sub> |   | P <sub>5</sub> |   | T <sub>5</sub> |

### **Definitions**

R11: Thermal Resistance of Die1 due to heating of Die1 (°C/W)

R12: Thermal Resistance of Die1 due to heating of Die2 (°C/W)

R13: Thermal Resistance of Die1 due to heating of Die3 (°C/W)

R14: Thermal Resistance of Die1 due to heating of Die4 (°C/W)

R15: Thermal Resistance of Die1 due to heating of Die5 (°C/W)

R21: Thermal Resistance of Die2 due to heating of Die1 (°C/W)

R22: Thermal Resistance of Die2 due to heating of Die2 (°C/W)

R23: Thermal Resistance of Die2 due to heating of Die3 (°C/W)

R24: Thermal Resistance of Die2 due to heating of Die4 (°C/W)

R25: Thermal Resistance of Die2 due to heating of Die5 (°C/W)

R31: Thermal Resistance of Die3 due to heating of Die1 (°C/W)

R32: Thermal Resistance of Die3 due to heating of Die2 (°C/W)

R33: Thermal Resistance of Die3 due to heating of Die3 (°C/W)

R34: Thermal Resistance of Die3 due to heating of Die4 (°C/W)

R35: Thermal Resistance of Die3 due to heating of Die5 (°C/W)

R41: Thermal Resistance of Die4 due to heating of Die1 (°C/W)

R42: Thermal Resistance of Die4 due to heating of Die2 (°C/W)

R43: Thermal Resistance of Die4 due to heating of Die3 (°C/W)

R44: Thermal Resistance of Die4 due to heating of Die4 (°C/W)

R45: Thermal Resistance of Die4 due to heating of Die5 (°C/W)

R51: Thermal Resistance of Die5 due to heating of Die1 (°C/W)

R52: Thermal Resistance of Die5 due to heating of Die2 (°C/W)

R53: Thermal Resistance of Die5 due to heating of Die3 (°C/W)

R54: Thermal Resistance of Die5 due to heating of Die4 (°C/W)

R55: Thermal Resistance of Die5 due to heating of Die5 (°C/W)

P1: Power dissipation of Die1 (W)

P2: Power dissipation of Die2 (W)

P3: Power dissipation of Die3 (W)

P4: Power dissipation of Die4 (W)

P5: Power dissipation of Die5 (W)

T1: Junction temperature of Die1 due to heat from all dice (°C)

T2: Junction temperature of Die2 due to heat from all dice (°C)

T3: Junction temperature of Die3 due to heat from all dice (°C)

T4: Junction temperature of Die4 due to heat from all dice (°C)

T5: Junction temperature of Die5 due to heat from all dice (°C)

T<sub>A</sub>: Ambient temperature (°C)

ΔT1: Temperature difference between Die1 junction and ambient (°C)

ΔT2: Temperature deference between Die2 junction and ambient (°C)

$\Delta T3$ : Temperature difference between Die3 junction and ambient (°C)

$\Delta T4$ : Temperature deference between Die4 junction and ambient (°C)

ΔT5: Temperature deference between Die5 junction and ambient (°C)

#### **Equation 1:**

$T1 = (R11 \times P1 + R12 \times P2 + R13 \times P3 + R14 \times P4 + R15 \times P5) + T_A$

### **Equation 2:**

$$T2 = (R21 \times P1 + R22 \times P2 + R23 \times P3 + R24 \times P4 + R25 \times P5) + T_A$$

### **Equation 3:**

$$T3 = (R31 \times P1 + R32 \times P2 + R33 \times P3 + R34 \times P4 + R35 \times P5) + T_A$$

#### **Equation 4:**

$$T4 = (R41 \times P1 + R42 \times P2 + R43 \times P3 + R44 \times P4 + R45 \times P5) + T_A$$

#### **Equation 5:**

$$T5 = (R51 \times P1 + R52 \times P2 + R53 \times P3 + R54 \times P4 + R55 \times P5) + T_A$$

### **Measurement Data**

Measurement is done on both Low effective thermal conductivity test board (according to JESD51-3) and on High effective thermal conductivity test board (according to JESD51-7).

**Table 1: Test Board Thermal Conductivity Measurement Data**

| Test Board Type                                                        | Test Board<br>Conditions                                                                                                                                                                  | Thermal<br>Resistance                                                                                                                                                                                                                                                                                                                                                                                                  | Power Dissipation Derating Chart                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| High Effective Thermal Conductivity Board  AVGO  ORDINATE BIOL  76.2mm | Four-layer board that embodies two signal layers, a power plane, and a ground plane. Outer layer copper thickness: 2 oz. Inner layers copper thickness: 1 oz. Board size: 76.2mm × 76.2mm | R11: 191.5°C/W<br>R12: 39.3°C/W<br>R13: 38.8°C/W<br>R14: 16.5°C/W<br>R15: 22.3°C/W<br>R21: 40.9°C/W<br>R22: 202.7°C/W<br>R23: 48.5°C/W<br>R24: 23.8°C/W<br>R25: 18.6°C/W<br>R31: 38.8°C/W<br>R32: 48.5°C/W<br>R32: 48.5°C/W<br>R32: 48.5°C/W<br>R33: 46.1°C/W<br>R35: 17.0°C/W<br>R41: 20.5°C/W<br>R42: 29.1°C/W<br>R43: 18.8°C/W<br>R45: 14.3°C/W<br>R52: 21.8°C/W<br>R53: 19.9°C/W<br>R54: 14.3°C/W<br>R55: 56.4°C/W | Figure 10: Power Derating Chart Based on High Effective Thermal Conductivity  Po, Output IC(Die 4 or 5) Pi, Input IC(Die 1,2 and 3) Pi, Input IC(Die 1,2 and 3) Pi output IC De 1,2 and 3)  Ta - AMBIENT TEMPERATURE - °C  NOTE:  Output IC power dissipation is derated linearly 4 mW/°C above 105°C from 400 mW to 320 mW at 125°C.  Input ICs power dissipation is derated linearly 2.5mW/°C above 105°C from 150 mW to 100 mW at 125°C. |  |  |

**Test Board** Thermal **Test Board Type Conditions Power Dissipation Derating Chart** Resistance Low Effective Thermal Single-layer board R11: 224.9°C/W Figure 11: Power Derating Chart Based on Low Effective Thermal Conductivity Board for signal. R12: 73.24°C/W Conductivity R13: 64.15°C/W Outer layer copper R14: 37.9°C/W Po. Output IC(Die 4 or 5) Avago thickness: 2 oz. 450 Pi, Input IC(Die 1,2 and 3) R15: 47.49°C/W Board size: R21: 82.28°C/W 400 76.2mm × 76.2mm R22: 239.8°C/W 350 R23: 64.38°C/W 300 R24: 47.15°C/W DISSIPATION R25: 40.8°C/W 250 R31: 64.15°C/W 200 R32: 64.38°C/W POWER R33: 70.91°C/W 150 R34: 36.56°C/W ŗ. 100 R<sub>35</sub>: 38.56°C/W 50 R<sub>41</sub>: 50.49°C/W R<sub>42</sub>: 60.8°C/W 75 100 125 R<sub>43</sub>: 39.19°C/W Ta - AMBIENT TEMPERATURE - °C R<sub>44</sub>: 91.58°C/W R<sub>45</sub>: 34.8°C/W NOTE: R<sub>51</sub>: 62.22°C/W Output IC power dissipation is derated linearly 8 mW/°C above R<sub>52</sub>: 48.62°C/W 105°C from 400 mW to 240 mW at 125°C. R<sub>53</sub>: 48.38°C/W Input ICs' power dissipation is derated linearly 4 mW/°C above R<sub>54</sub>: 33.75°C/W 105°C from 150 mW to 70 mW at 125°C.

Table 1: Test Board Thermal Conductivity Measurement Data (Continued)

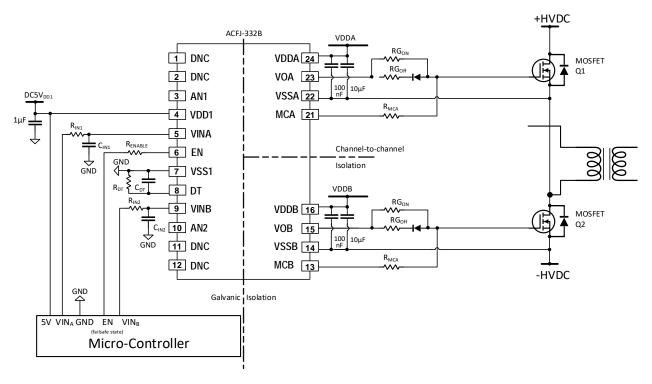

### **Notes on Thermal Calculation**

The application and environmental design for the ACFJ-332B must ensure that the junction temperature of the internal ICs and LEDs within the gate driver's optocoupler do not exceed 150°C. The following examples are based on a typical circuit shown in Figure 31 for estimation of maximum power dissipation and corresponding effect on junction temperatures. This thermal calculation can only be used as a reference for thermal comparison between actual application board layout and PCB board according to JESD51-7. The actual power dissipation achievable will depend on the application environment (PCB layout, airflow, part placement, and so on). The following examples can be used as a reference for thermal performance comparison under the specified PCB layout as shown in Table 1.

### Calculation of Input LED Power Dissipation, P1 and P2

Input LED Power Dissipation (P1) =  ${}^{1}I_{E(I,ED)}$  (Recommended Max.) ×  ${}^{1}V_{E(I,ED,125^{\circ}C)}$  × Duty Cycle

R<sub>55</sub>: 86.64°C/W

#### Example:

P1 = 10 mA × 1.85V × 50% duty cycle = 9 mW  $P2 = P_1 = 9 \text{ mW}$

### Calculation of Input IC Power Dissipation, P3

#### **Example:**

Input IC Power Dissipation, P3 = I<sub>DD1 (Max.)</sub> × V<sub>DD1 (Recommended Max.)</sub>  $= 2.7 \text{ mA} \times 5.5 \text{V}$ = 15 mW

By design.

ACFJ-332B-DS100 Broadcom

### Calculation of Output IC Power Dissipation, P4 or P5

### **Example:**

Output IC Power Dissipation:

$$P_{4,5} = P_{O \text{ (Static)}} + P_{HS} + P_{LS} + P_{MC}$$

- Q<sub>G|21V</sub>: MOSFET gate charge at 21V supply voltage (0.15 µC)

- Q<sub>G|2.5V</sub>: MOSFET gate charge at 2.5V supply voltage (0.04 μC)

- f<sub>PWM</sub>: Input LED switching frequency (150 kHz)

- R<sub>G</sub>: External gate charging resistance (6Ω)

- R<sub>DS,OL(MAX)</sub>: By design, maximum low side output impedance (2Ω)

- R<sub>DS,OH(MAX)</sub>: By design, maximum high side output impedance (2Ω)

- V<sub>THCLAMP(MAX)</sub>: Maximum Clamp Threshold Voltage (2.1V)

- R<sub>DS\_MC(MAX)</sub>: By design, maximum internal clamp resistance (2Ω)

- R<sub>MC</sub>: External clamp resistance (1Ω)

$P_{O\;(Static)}\!\!:$  Static power dissipated by the output IC

- $= I_{VDD} \times V_{DD}$

- = 5.9 mA<sub>(Data Sheet Max.)</sub> × 21V)

- = 124 mW

$P_{\mbox{\scriptsize HS}}\!:$  High Side PMOS Switching Power Dissipation at  $V_{\mbox{\scriptsize O}}$  pin

- =  $(V_{DD} \times Q_{G|21V} \times f_{PWM}) \times R_{DS,OH(MAX)} / (R_{DS,OH(MAX)} + R_G) / 2$

- =  $(21V \times 0.15 \,\mu\text{C} \times 150 \,\text{kHz}) \times 2/(2 + 6) / 2$

- = 59 mW

$P_{LS}\!\!:$  Low Side Switching Power Dissipation at  $V_O$  pin

- =  $(V_{DD} \times Q_{G|21V} \times f_{PWM}) \times R_{DS,OL(MAX)} / (R_{DS,OL(MAX)} + R_G) / 2$

- =  $(21V \times 0.15 \mu C \times 150 \text{ kHz}) \times 2/(2 + 6) / 2$

- = 59 mW

P<sub>MC</sub>: Miller Clamp NMOS Switching Power Dissipation

- =  $(V_{THCLAMP(MAX)} \times Q_{G|2.5V} \times f_{PWM}) \times R_{DS\_MC(MAX)} / (R_{DS\_MC(MAX)} + R_{MC}) / 2$

- =  $(2.1V \times 0.04 \mu C \times 150 \text{ kHz}) \times 2/(2 + 1) / 2$

- = 38 mW

P<sub>4.5</sub>: Output IC Power Dissipation

- $= P_{O (Static)} + P_{HS} + P_{LS} + P_{MC}$

- = 124 mW + 59 mW + 59 mW + 4.2 mW

- = 246 mV

### Junction Temperature Calculation for High Thermal Conductivity Board, $T_A = 125$ °C

#### **Example:**

- Input LED1 Junction Temperature, **T1**

- = (R11 × P1 + R12 × P2 + R13 × P3 + R14 × P4 + R15 × P5) + 125°C

- =  $(191.5^{\circ}\text{C/W} \times 9 \text{ mW}) + (39.3^{\circ}\text{C/W} \times 9 \text{ mW}) + (38.8^{\circ}\text{C/W} \times 15 \text{ mW}) + (16.5^{\circ}\text{C/W} \times 280 \text{ mW}) + (22.3^{\circ}\text{C/W} \times 280 \text{ mW}) + 125^{\circ}\text{C}$ =  $139^{\circ}\text{C} < \text{T}_{.1}$  (absolute max.) of  $150^{\circ}\text{C}$

- Input LED2 Junction Temperature, **T2**

- = (R21 × P1 + R22 × P2 + R23 × P3 + R24 × P4 + R25 × P5) + 125°C

- =  $(40.9^{\circ}\text{C/W} \times 9 \text{ mW}) + (202.7^{\circ}\text{C/W} \times 9 \text{ mW}) + (48.5^{\circ}\text{C/W} \times 15 \text{ mW}) + (23.8^{\circ}\text{C/W} \times 280 \text{ mW}) + (18.6^{\circ}\text{C/W} \times 280 \text{ mW}) + 125^{\circ}\text{C}$ =  $140^{\circ}\text{C} < \text{T}_{J}$  (absolute max.) of  $150^{\circ}\text{C}$

- Input IC Junction Temperature, T3

- = (R21 × P1 + R22 × P2 + R23 × P3 + R24 × P4 + R25 × P5) + 125°C

- =  $(38.8^{\circ}\text{C/W} \times 9 \text{ mW}) + (48.5^{\circ}\text{C/W} \times 9 \text{ mW}) + (46.1^{\circ}\text{C/W} \times 15 \text{ mW}) + (16.2^{\circ}\text{C/W} \times 280 \text{ mW}) + (17^{\circ}\text{C/W} \times 280 \text{ mW}) + 125^{\circ}\text{C}$ =  $136^{\circ}\text{C} < T_{J}$  (absolute max.) of  $150^{\circ}\text{C}$

- Output IC Junction Temperature, **T4**

- = (R41 × P1 + R42 × P2 + R43 × P3 + R44 × P4 + R45 × P5) + 125°C

- =  $(20.5^{\circ}\text{C/W} \times 9 \text{ mW}) + (29.1^{\circ}\text{C/W} \times 9 \text{ mW}) + (18.8^{\circ}\text{C/W} \times 15 \text{ mW}) + (57.1^{\circ}\text{C/W} \times 280 \text{ mW}) + (14.3^{\circ}\text{C/W} \times 280 \text{ mW}) + 125^{\circ}\text{C}$ =  $146^{\circ}\text{C} < T_{\perp}$  (absolute max.) of  $150^{\circ}\text{C}$

- Output IC Junction Temperature, **T5**

- = (R41 × P1 + R42 × P2 + R43 × P3 + R44 × P4 + R45 × P5) + 125°C

- =  $(28.8^{\circ}\text{C/W} \times 9 \text{ mW}) + (21.8^{\circ}\text{C/W} \times 9 \text{ mW}) + (19.9^{\circ}\text{C/W} \times 15 \text{ mW}) + (14.3^{\circ}\text{C/W} \times 280 \text{ mW}) + (56.4^{\circ}\text{C/W} \times 280 \text{ mW}) + 125^{\circ}\text{C}$ =  $146^{\circ}\text{C} < T_{\perp}$  (absolute max.) of  $150^{\circ}\text{C}$

NOTE: Junction temperature of T1, T2, T3, T4, and T5 must not exceed 150°C at any given ambient temperature T<sub>A</sub>.

## **Typical Performance Plots**

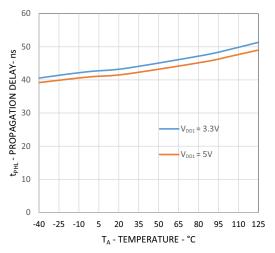

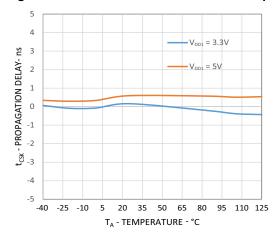

$T_A$  = 25°C,  $VDD_{A,B} - VSS_{A,B}$  = 15V. With capacitance load of 2.2 nF, unless otherwise noted.

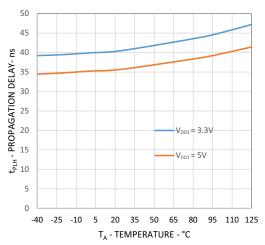

Figure 12: tP<sub>LH</sub> vs Temperature

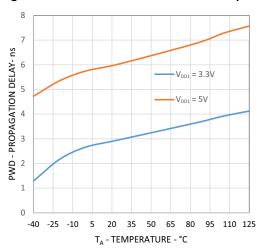

Figure 14: Pulse Width Distortion vs Temperature

Figure 16: UVLO<sub>A,B</sub> Threshold vs Temperature

Figure 13: tP<sub>HL</sub> vs Temperature

Figure 15: Channel-to-Channel Skew vs Temperature

Figure 17: UVLO<sub>A,B</sub> Hysteresis vs Temperature

Figure 18: VIN High Threshold vs Temperature

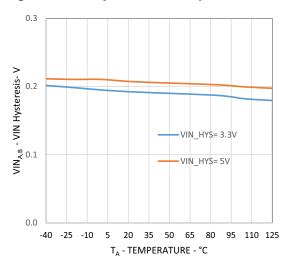

Figure 20: VIN Hysteresis vs Temperature

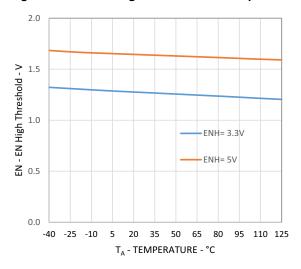

Figure 22: Enable High Threshold vs Temperature

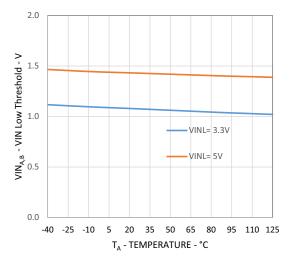

Figure 19: VIN Low Threshold vs Temperature

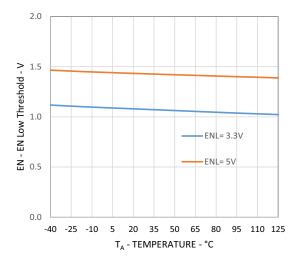

Figure 21: Enable Low Threshold vs Temperature

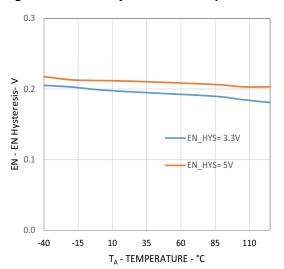

Figure 23: Enable Hysteresis vs Temperature

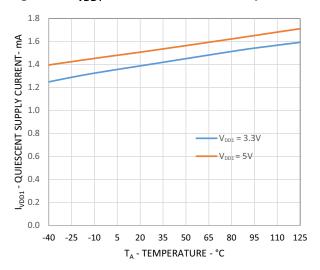

Figure 24: I<sub>VDD1</sub> Quiescent Current vs Temperature

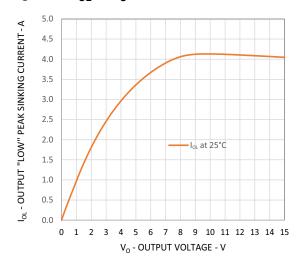

Figure 26: I<sub>OL</sub> vs V<sub>O</sub>

Figure 28: Channel A Dead Time vs. Temperature

Figure 25: I<sub>VDDA,B</sub> Quiescent Current vs Temperature

Figure 27:  $I_{OH}$  vs  $(V_{DD} - V_{O})$

Figure 29: Dead Time Matching vs. Temperature

## **Typical Application Circuit**

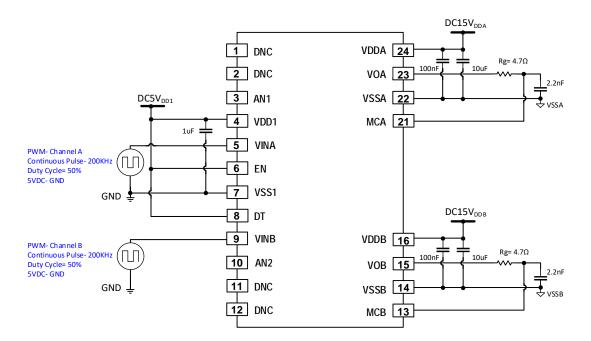

Figure 30: ACFJ-332B Typical Application Circuit

**NOTE:** Component value is subject to change based on applications conditions.

#### VDD1, VDDA, and VDDB Supply Pins

A low ESR 1-µF ceramic capacitor with minimum voltage ratings of 6.5V is recommend for VDD1 to VSS1 decoupling capacitors.

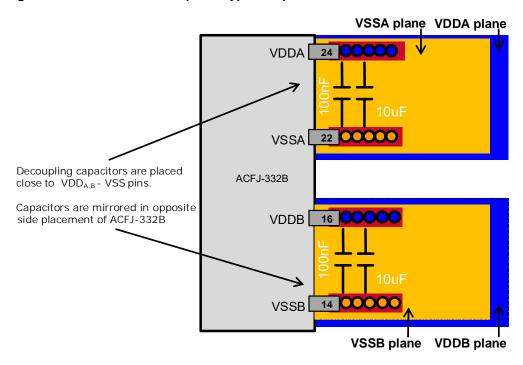

For VDDA to VSSA and VDDB to VSSB, a pair of ceramic decoupling capacitors with low ESR of 100 nF and 10  $\mu$ F are connected in parallel. During the dynamic load switching transition, a large transient charge from ACFJ-332B is drawn from the decoupling capacitors to drive the output capacitive load. Depending on the load gate charge and ripple voltage tolerance during load switching, the minimum capacitance values can be adjusted accordingly.

#### **EN Input Pin**

Direct connection to TTL/CMOS compatible logic level devices or connect with a current-limiting resistor.

#### **DT Pin**

A pair of fixed resistor ( $R_{DT}$ ) and a bypass ceramic capacitor ( $C_{DT}$ ) of 0.1  $\mu F$  are recommended to connect close to the DT and VSS1 pin.

The  $C_{DT}$  is for noise filtering, while the  $R_{DT}$  will insert dead time into the dual output channels, according to the following equation:  $t_{DT}$  in (ns) = (8.9 ×  $R_{DT}$ ) + 18,  $R_{DT}$  in (k $\Omega$ ).

Connect the DT pin to VDD1 if dead time is not in use.

### **VINA and VINB Input Pins**

Direct connection to TTL/CMOS compatible logic level devices to a pair of PWM input. A first-order RC filter between PWM input and VIN, with  $R_{IN_{A,B}}$  in the range of  $0\Omega$  to  $100\Omega$ , and  $C_{INA}$  and  $C_{INB}$  in the range of 33 pF to 100 pF is recommended for noise filtering.

### VOA, VOB, MCA, and MCB Output Pins

External gate resistors are connected to the VO<sub>A,B</sub> pins to limit the peak gate current, skew the GaN/MOSFET rise/fall times, and dissipate the gate driver's output power. The designer should size the external gate resistor so that the output peak current does not exceed the absolute maximum ratings.

#### **Example:**

Given VDDA - VSSA = 12V:

- Assume sourcing –2.5A out from ACFJ-332B.

- Assume sinking 4A into ACFJ-332B.

$R_{OAH} = 1.2\Omega(R_{NMOS})||15\Omega, R_{OAL} = 1.2\Omega$ , wherein  $R_{NMOS}$  is equal to  $R_{OAL}$

- Minimum external gate turn-on resistor =  $(VDDA VSSA)/I_{OAH(PEAK)} R_{OAH} = (12V/2.5A) 1.1\Omega = 3.7\Omega$

- Minimum external gate turn-off resistor =  $(VDDA VSSA)/I_{OAL(PEAK)} R_{OAL} = (12V/4A) 1.2\Omega = 1.8\Omega$

- This example excludes the GaN/MOSFET internal gate resistance.

- Similar calculation applies to channel B.

For MCA and MCB pins, use an external resistor value in the range of  $0.5\Omega$  to less than  $1\Omega$ .

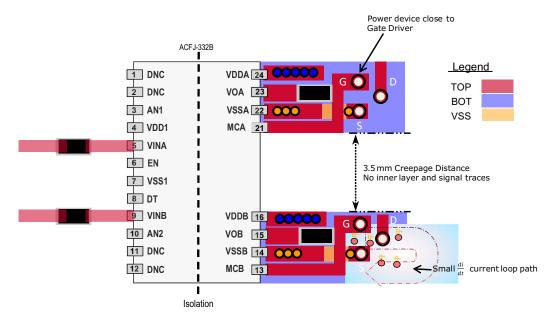

Figure 31: Example ACFJ-332B Gate Driver Circuit with Silicon MOSFET Application Circuit Diagram

**NOTE:** 3.5-mm separation between two live parts of the SO-24 can address functional isolation up to 700 V<sub>RMS</sub> with pollution degree 2.

## **Description of Operations and Functions**

### **Input Control and Output Truth Table**

Table 2 depicts all the possible input state transitions and the resultant outputs.

**NOTE:** x represents do not care state.

**Table 2: Input and Output Control Truth Table**

| Input |      |          |      |      | Output |      | Notes                                                                         |

|-------|------|----------|------|------|--------|------|-------------------------------------------------------------------------------|

| VDD1  | EN   | DT       | VINA | VINB | VOA    | VOB  |                                                                               |

| >2.5V | High | Active   | Low  | Low  | Low    | Low  | Output transition (from Low to High) occurs after internal dead time expires. |

| >2.5V | High | Active   | Low  | High | Low    | High | Output transition (from Low to High) occurs after internal dead time expires. |

| >2.5V | High | Active   | High | Low  | High   | Low  | Output transition (from Low to High) occurs after internal dead time expires. |

| >2.5V | High | Active   | High | High | Low    | Low  | Invalid state. Both outputs are pulled to low state.                          |

| >2.5V | High | Inactive | Low  | Low  | Low    | Low  | Output transition occurs immediately.                                         |

| >2.5V | High | Inactive | Low  | High | Low    | High | Output transition occurs immediately.                                         |

| >2.5V | High | Inactive | High | Low  | High   | Low  | Output transition occurs immediately.                                         |

| >2.5V | High | Inactive | High | High | High   | High | Output transition occurs immediately.                                         |

| >2.5V | Low  | Х        | х    | Х    | Low    | Low  | Driver is disabled. Both outputs are pulled to low state.                     |

| <2.5V | Х    | Х        | х    | Х    | Low    | Low  | VCC1 under-voltage lockout.                                                   |

### **Programmable Dead Time**

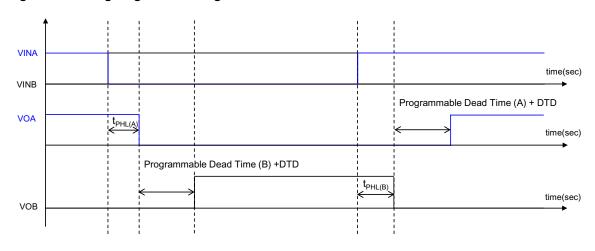

Figure 32: Timing Diagram with Programmable Dead Time

Programmable dead time is set according to the equation  $t_{DT}$  in (ns) =  $(8.9 \times R_{DT}) + 18$ , in (k $\Omega$ ). The measured dead time at both the gate driver outputs  $V_{OA}$  and  $V_{OB}$  are the total of the programmable dead time plus the dead time distortion (DTD).

Dead time distortion (DTD) is defined as  $(t_{PLH} - t_{PHL})$  between any two parts under the same test condition. A negative DTD value will decrease the programmable dead time set by  $R_{DT}$ ; a positive DTD value will add to the programmable dead time set by  $R_{DT}$ .

## Timing Response Enable and VINA.B

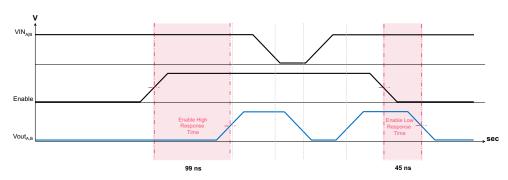

Figure 33: Enable Response Time

Figure 33 shows the response time that the enable function has on the dual-channel outputs. The enable function adds on a 50-ns delay on the rising edge of the output, but not on the falling edge.

The measured propagation delay on the rising edge output is the total of enable 50-ns delay plus the gate driver's propagation delay.

## **Layout Guidelines**

The gate driver's output sinks about 4A(typical), which the return current path of minimum inductance must be implemented during printed circuit board layout design to alleviate the effect of ground bounce.

Adequate spacing must be maintained between the high voltage isolated circuitry and any input reference circuitry. The minimum spacing between two adjacent high-side isolated channels (that is, top and bottom channels) must be taken into consideration as well. Insufficient spacing will reduce the effective isolation and might increase parasitic coupling that will degrade part performance. Figure 34 shows the recommended PCB layout guidelines.

Figure 34: PCB Layout Guidelines

The placement and routing of supply bypass capacitors require special attention. During switching transients, the majority of gate charge is supplied by bypass capacitors. Maintaining short bypass capacitor trace lengths will ensure low supply ripple and clean switching waveforms. It is recommended to connect the bypass capacitors to the power plane and ground plane with multiple via holes. The planes can provide better heat dissipation and, at the same time, serve as a natural decoupling capacitor to the IC. Figure 35 shows the bypass capacitors placement and PCB planes stack-up.

Figure 35: PCB Planes Stack-Up and Bypass Capacitors Placement

| Converget © 2024 Procedure: All Dights Decorated. The term "Procedure" refers to Procedure Inc. and/or its subsidiaries. For                                                                                                                                                                                                                                                                                                                                                                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Copyright © 2024 Broadcom. All Rights Reserved. The term "Broadcom" refers to Broadcom Inc. and/or its subsidiaries. For more information, go to www.broadcom.com. All trademarks, trade names, service marks, and logos referenced herein belong to their respective companies.                                                                                                                                                                                                                 |

| Broadcom reserves the right to make changes without further notice to any products or data herein to improve reliability, function, or design. Information furnished by Broadcom is believed to be accurate and reliable. However, Broadcom does not assume any liability arising out of the application or use of this information, nor the application or use of any product or circuit described herein, neither does it convey any license under its patent rights nor the rights of others. |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| <b>● BROADCOM</b> °                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |