# **BCM88800**

**Traffic Management Architecture**

**Design Guide**

Broadcom, the pulse logo, Connecting everything, Avago Technologies, Avago, the A logo, and BroadSync are among the trademarks of Broadcom and/or its affiliates in the United States, certain other countries, and/or the EU.

Copyright © 2018–2021 Broadcom. All Rights Reserved.

The term "Broadcom" refers to Broadcom Inc. and/or its subsidiaries. For more information, please visit www.broadcom.com.

Broadcom reserves the right to make changes without further notice to any products or data herein to improve reliability, function, or design. Information furnished by Broadcom is believed to be accurate and reliable. However, Broadcom does not assume any liability arising out of the application or use of this information, nor the application or use of any product or circuit described herein, neither does it convey any license under its patent rights nor the rights of others.

# **Table of Contents**

| Chap       | pter 1: Introduction                                                                                                                                                                                                                                                             | 8                    |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 1.1        | Document Organization                                                                                                                                                                                                                                                            | 8                    |

| 1.2        | BCM88800 Applications                                                                                                                                                                                                                                                            | g                    |

| Chap       | pter 2: DNX Traffic Management Architecture                                                                                                                                                                                                                                      | 10                   |

|            | Packet Flow Overview                                                                                                                                                                                                                                                             |                      |

| 2.2        | Unicast Packet Flow                                                                                                                                                                                                                                                              | 12                   |

|            | 2.2.1 Ingress Handling                                                                                                                                                                                                                                                           | 12                   |

|            | 2.2.2 Fabric Handling                                                                                                                                                                                                                                                            | 12                   |

|            | 2.2.3 Egress Handling                                                                                                                                                                                                                                                            | 13                   |

|            | 2.2.4 Configuring a Unicast Flow                                                                                                                                                                                                                                                 | 13                   |

| 2.3        | Multicast Packet Flow                                                                                                                                                                                                                                                            | 14                   |

|            | 2.3.1 Multicast Mechanisms                                                                                                                                                                                                                                                       | 14                   |

|            | 2.3.2 Ingress Replication                                                                                                                                                                                                                                                        | 14                   |

|            | 2.3.3 Fabric Replication                                                                                                                                                                                                                                                         | 15                   |

|            | 2.3.4 Egress Replication                                                                                                                                                                                                                                                         | 16                   |

|            | 2.3.5 Mesh Replication                                                                                                                                                                                                                                                           | 16                   |

| Chap       | pter 3: Functional Overview                                                                                                                                                                                                                                                      | 17                   |

| Chap       | oter 4: Core Overview                                                                                                                                                                                                                                                            | 20                   |

| Chap       | pter 5: Ingress Traffic Management                                                                                                                                                                                                                                               | 22                   |

|            | Ingress Traffic Manager Overview                                                                                                                                                                                                                                                 |                      |

| 5.2        | Ingress Interfaces                                                                                                                                                                                                                                                               | 23                   |

| 5.3        | Network Interfaces (NIF) Oversubscription Management                                                                                                                                                                                                                             | 25                   |

|            | 5.3.1 NIF Priority Assignment                                                                                                                                                                                                                                                    | 26                   |

| 5.4        |                                                                                                                                                                                                                                                                                  |                      |

|            | ITM-Ports and Packet Reassembly                                                                                                                                                                                                                                                  |                      |

| 5.5        | Firm-Ports and Packet Reassembly                                                                                                                                                                                                                                                 | 27                   |

|            | •                                                                                                                                                                                                                                                                                | 27<br>28             |

| 5.6        | Packet Memory                                                                                                                                                                                                                                                                    | 27<br>28<br>28       |

| 5.6        | Packet Memory                                                                                                                                                                                                                                                                    | 27<br>28<br>28       |

| 5.6        | Packet Memory SRAM Packet Memory DRAM Packet Memory                                                                                                                                                                                                                              | 27<br>28<br>28<br>28 |

| 5.6        | Packet Memory  SRAM Packet Memory  DRAM Packet Memory  5.7.1 Data Integrity of Packet Memory                                                                                                                                                                                     | 27282828             |

| 5.6        | Packet Memory  SRAM Packet Memory  DRAM Packet Memory  5.7.1 Data Integrity of Packet Memory  5.7.1.1 SRAM-Packet-CRC                                                                                                                                                            | 2728282829           |

| 5.6        | Packet Memory  SRAM Packet Memory  DRAM Packet Memory  5.7.1 Data Integrity of Packet Memory  5.7.1.1 SRAM-Packet-CRC  5.7.1.2 DRAM-Packet-CRC                                                                                                                                   | 272828292929         |

| 5.6        | Packet Memory  SRAM Packet Memory  DRAM Packet Memory  5.7.1 Data Integrity of Packet Memory  5.7.1.1 SRAM-Packet-CRC  5.7.1.2 DRAM-Packet-CRC  5.7.1.3 DRAM-CUD CRC                                                                                                             | 272828292929         |

| 5.6        | Packet Memory  SRAM Packet Memory  DRAM Packet Memory  5.7.1 Data Integrity of Packet Memory  5.7.1.1 SRAM-Packet-CRC  5.7.1.2 DRAM-Packet-CRC  5.7.1.3 DRAM-CUD CRC  5.7.1.4 DRAM-ECC                                                                                           | 27282929292929       |

| 5.6<br>5.7 | Packet Memory  DRAM Packet Memory  5.7.1 Data Integrity of Packet Memory  5.7.1.1 SRAM-Packet-CRC  5.7.1.2 DRAM-Packet-CRC  5.7.1.3 DRAM-CUD CRC  5.7.1.4 DRAM-ECC  5.7.1.5 DRAM-Opportunistic Last Buffer CRC-16                                                                | 2728282929292929     |

| 5.6<br>5.7 | Packet Memory  SRAM Packet Memory  DRAM Packet Memory  5.7.1 Data Integrity of Packet Memory  5.7.1.1 SRAM-Packet-CRC  5.7.1.2 DRAM-Packet-CRC  5.7.1.3 DRAM-CUD CRC  5.7.1.4 DRAM-ECC  5.7.1.5 DRAM-Opportunistic Last Buffer CRC-16  5.7.1.6 Erroneous DRAM Buffer Reclamation | 272828292929292930   |

| 5.8.3 DRAM Enqueue and Dequeue Walkthrough                               | 32 |

|--------------------------------------------------------------------------|----|

| 5.9 Destination Resolution                                               | 33 |

| 5.9.1 DSP Queue Resolution                                               | 33 |

| 5.9.2 Flow to Queue Resolution                                           | 34 |

| 5.9.3 Multi-TM Domain DSP to Queue Resolution                            | 36 |

| 5.9.4 LAG Forwarding and LAG Resolution                                  | 36 |

| 5.10 Ingress Transmit Packet Processing                                  | 39 |

| 5.11 TM Action Resolution and Multicast Replication                      |    |

| 5.12 Congestion Management                                               |    |

| 5.12.1 Overview                                                          | 41 |

| 5.12.2 Virtual Statistics Queues                                         | 42 |

| 5.12.3 Fair Adaptive Dynamic Threshold                                   | 44 |

| 5.12.4 WRED Admission                                                    | 45 |

| 5.12.5 Congestion Management Model                                       | 46 |

| 5.12.6 Resource Partitioning and Allocation                              | 49 |

| 5.12.6.1 Source Minimal Guaranteed Segment                               | 50 |

| 5.12.6.2 Shared-Resources Segment                                        | 51 |

| 5.12.6.3 Headroom Segment                                                | 51 |

| 5.12.6.4 VOQ Guaranteed Resources Segment                                | 52 |

| 5.12.7 Admission Logic                                                   | 55 |

| 5.12.7.1 Lossless Traffic                                                | 56 |

| 5.12.7.2 Global Resource Protection                                      | 56 |

| 5.12.7.3 SRAM-PD Protection                                              | 56 |

| 5.12.7.4 Global-VOQ Based Accounting and Admission Criteria              |    |

| 5.12.7.5 VOQ Admission Criteria                                          | 58 |

| 5.12.7.6 Queue-Groups and Generic VSQs Admission Criteria and Accounting | 58 |

| 5.12.7.7 Source-Based Admission Tests                                    | 59 |

| 5.12.8 Drop Reason                                                       | 60 |

| 5.12.9 Flow Control Generation                                           | 61 |

| 5.12.10 Explicit Congestion Notification                                 | 62 |

| 5.12.10.1 ECN Processing                                                 | 63 |

| 5.12.10.2 Packet Dequeue ECN Marking Decision                            | 63 |

| 5.12.10.3 Queue Size Marking                                             | 63 |

| 5.12.10.4 Ingress Latency Marking                                        | 63 |

| 5.12.10.5 Marking ECN into the Packet                                    | 64 |

| 5.12.11 Mirror-on-Drop                                                   | 64 |

| 5.12.12 Congestion Indicators                                            | 64 |

| 5.12.13 Instrumentation Congestion Management Counters                   | 65 |

| 5.12.14 NIF Oversubscription Counters                                    | 66 |

| 5.12.14.1 Congestion Interrupts                                          | 66 |

| 5.13                      | 3 Ingress Scheduling                                     | 67 |

|---------------------------|----------------------------------------------------------|----|

|                           | 5.13.1 High-Priority Class                               | 67 |

|                           | 5.13.2 Ingress Credit Scheduler                          | 68 |

|                           | 5.13.3 Fabric Multicast Queues Credit Scheduling         | 68 |

|                           | 5.13.4 Scheduler Packet Size Adjustment                  | 69 |

| 5.14                      | 4 Counter Command Generation                             | 71 |

| 5.15                      | 5 Ingress Meters                                         | 71 |

| 5.16                      | 6 Statistics Interface                                   | 71 |

| Chapter 6: Fabric Adapter |                                                          | 72 |

| 6.1                       | Cell Formats                                             | 72 |

| 6.2                       | Fabric Pipes                                             | 72 |

| 6.3                       | Fabric Transmit Adapter                                  | 72 |

|                           | 6.3.1 Mapping Dequeue Context to Fabric Adapter Contexts | 72 |

|                           | 6.3.2 Cell Priority                                      | 73 |

|                           | 6.3.3 Unicast Fabric Routing Table                       | 73 |

|                           | 6.3.4 Multicast Fabric Routing Bitmap                    | 73 |

|                           | 6.3.5 Reachability Cell Generation                       | 73 |

| 6.4                       | Fabric Receive Adapter                                   | 74 |

| Chap                      | oter 7: Egress Traffic Manager                           | 75 |

|                           | Egress Traffic Manager Overview                          |    |

| 7.2                       | ETM Resources and Queues                                 | 76 |

| 7.3                       | OTM Ports                                                | 77 |

| 7.4                       | ETM Enqueue Request                                      | 77 |

| 7.5                       | Multicast Replication                                    | 78 |

| 7.6                       | Port and CoS Mapping                                     | 79 |

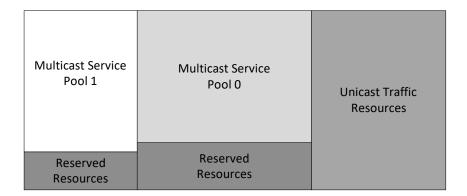

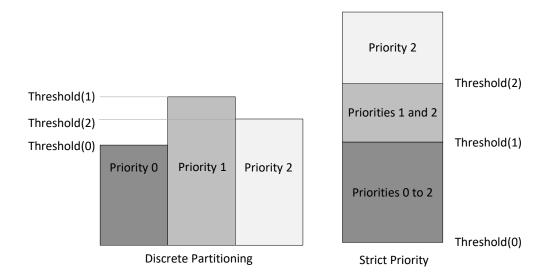

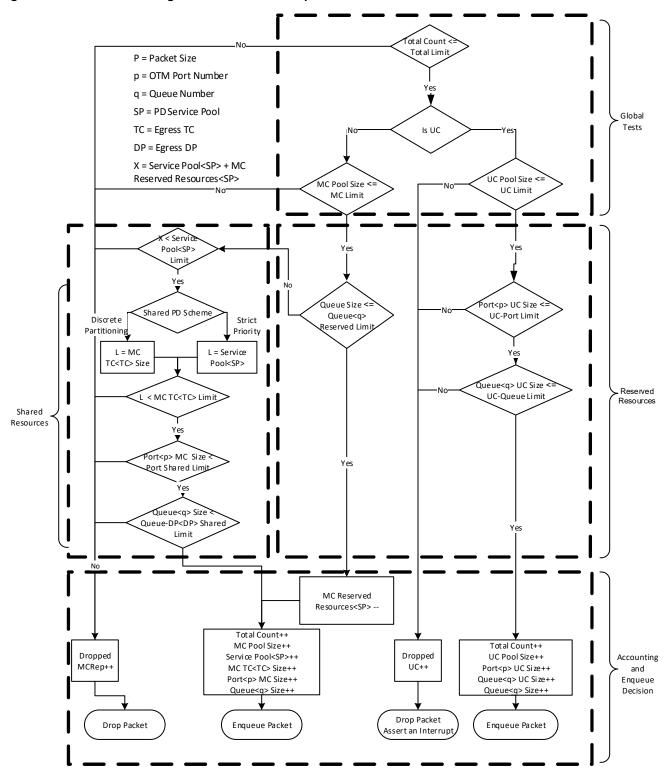

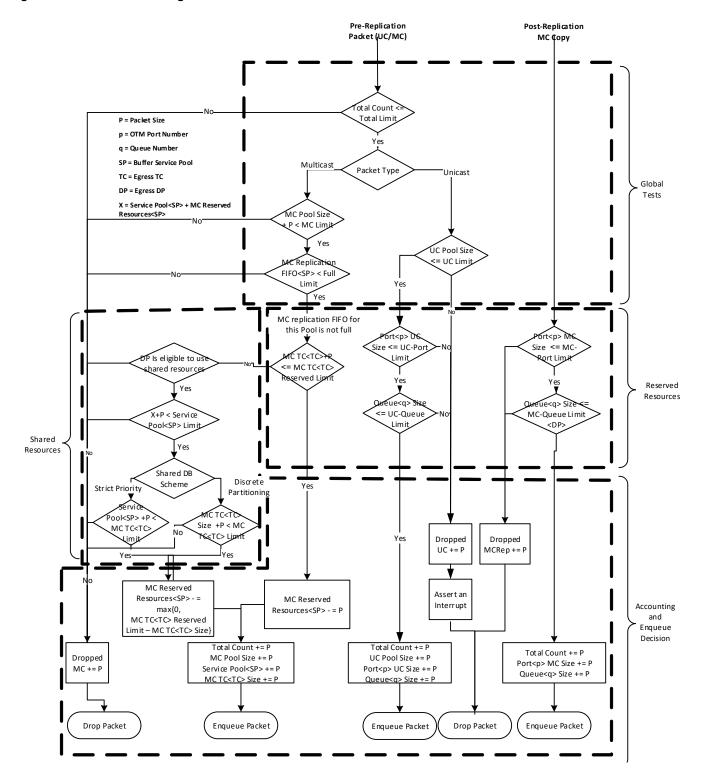

| 7.7                       | Congestion Management                                    | 81 |

|                           | 7.7.1 Overview                                           | 81 |

|                           | 7.7.2 Unicast Traffic Resources Management               | 83 |

|                           | 7.7.3 Multicast Traffic Resources Management             | 83 |

|                           | 7.7.3.1 Multicast Packet Descriptor Management           | 84 |

|                           | 7.7.3.2 Multicast Data Buffers Management                | 84 |

|                           | 7.7.4 Queue Size Limit                                   | 85 |

|                           | 7.7.5 Flow-Control to the Egress Credit Scheduler        | 85 |

|                           | 7.7.6 Admission Test Algorithms                          | 88 |

| 7.8                       | Congestion Statistics Records                            | 91 |

|                           | 7.8.1 Instantaneous Statistic Records                    | 91 |

|                           | 7.8.2 Congestion Tracking Record                         | 91 |

| 7.9                       | Counter Command Generation                               | 91 |

| 7 10                      | 0. Foress Transmit Scheduler                             | 92 |

|      | 7.10.1 Egress Packet Size                           | 95  |

|------|-----------------------------------------------------|-----|

|      | 7.10.2 Shaping                                      | 95  |

|      | 7.10.3 Interface Scheduler and Priority Propagation | 96  |

|      | 7.10.4 Channelized Interface Scheduler              | 97  |

|      | 7.10.5 OTM Port Scheduler                           | 98  |

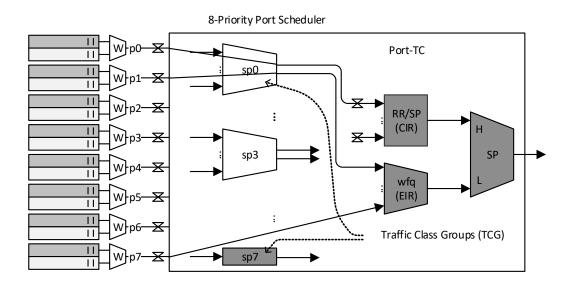

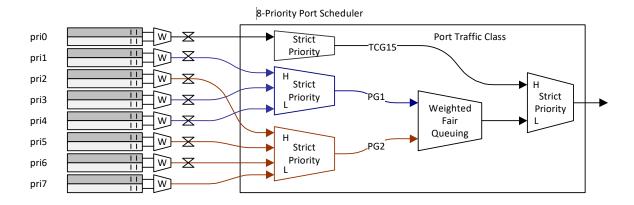

|      | 7.10.5.1 Eight-Priority Port Scheduler              | 98  |

|      | 7.10.5.2 Enhanced Transmission Selection Scheme     | 99  |

|      | 7.10.5.3 Four-Priority Port Scheduler               | 99  |

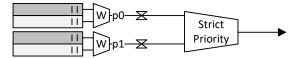

|      | 7.10.5.4 Two-Priority Port Scheduler                | 100 |

|      | 7.10.6 Queue-Pair Scheduler                         | 100 |

|      | 7.10.7 Port Utilization and Phantom Queues          | 101 |

|      | 7.10.8 Recycling Interfaces                         | 101 |

|      | 7.10.9 Egress Transmit Queues                       | 102 |

|      | 7.10.10 Egress Port Mirroring                       | 103 |

| Chap | pter 8: Egress Credit Scheduler                     | 104 |

| 8.1  | Egress Credit Scheduler                             | 104 |

| 8.2  | 2 Scheduler Features                                | 104 |

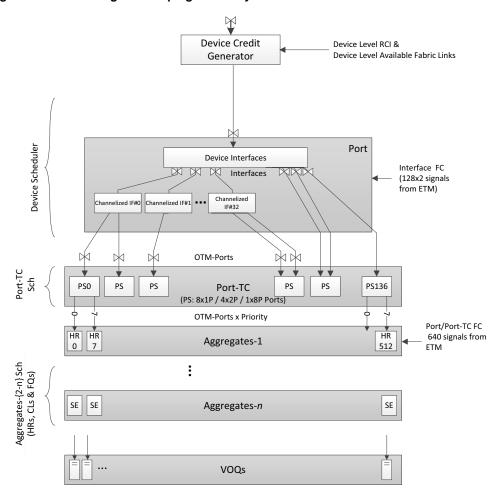

| 8.3  | Scheduling Hierarchy                                | 105 |

| 8.4  | Hierarchy Scheduling Programming                    | 108 |

| 8.5  | 5 Determining Credit Size                           | 108 |

| 8.6  | S Egress Replication Ports Scheduler                | 108 |

| 8.7  | 7 Flow Control                                      | 109 |

|      | B LAG-Based Credit Scheduling and Flow Control      |     |

| 8.9  | Scheduling Elements                                 | 110 |

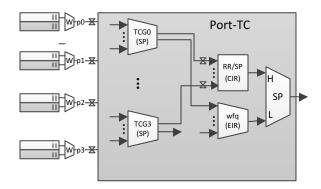

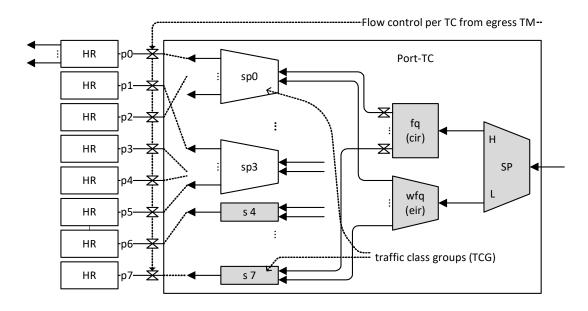

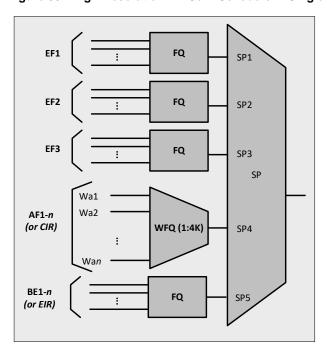

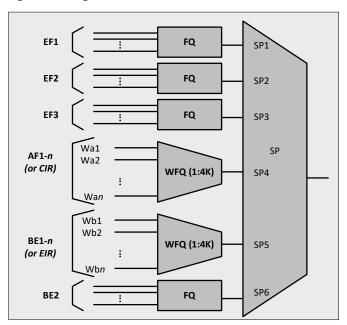

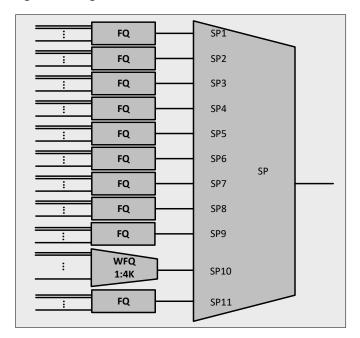

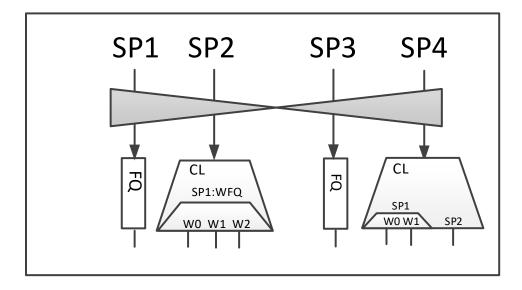

|      | 8.9.1 Type-0: Port-TC Scheduler Element             | 110 |

|      | 8.9.2 Type-1: HR Scheduler Element                  | 112 |

|      | 8.9.3 Type-2: CL Scheduler Element                  | 114 |

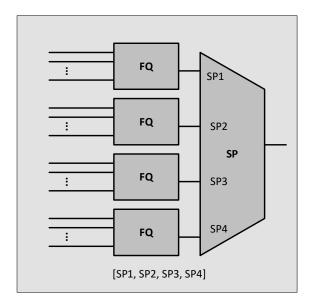

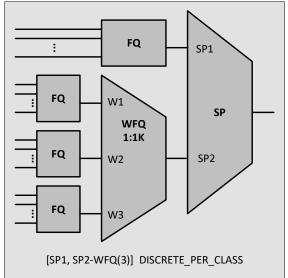

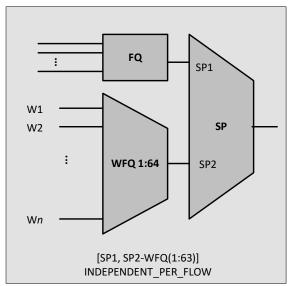

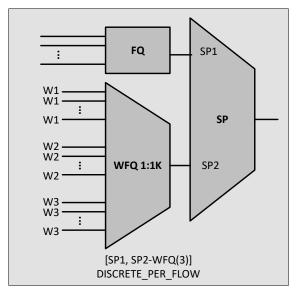

|      | 8.9.3.1 Basic CL Modes                              | 114 |

|      | 8.9.3.2 WFQ Modes                                   | 114 |

|      | 8.9.3.3 CL Enhanced Mode                            |     |

|      | 8.9.4 Type-3: Fair-Queuing Scheduler Element        |     |

| 8.1  | 0 Scheduler Flows                                   | 117 |

|      | 8.10.1 Scheduler Flow Attributes                    | 117 |

|      | 8.10.2 Scheduler Flow Rate                          | 117 |

|      | 8.10.3 Low Rate Flows                               |     |

|      | 8.10.4 Composite Flow                               |     |

|      | 8.10.5 Dual Flow                                    |     |

|      | 8.10.6 Flow Status                                  | 120 |

|      | 8.10.7 SEs Grouping and SE-to-Flow Mapping          | 121 |

|      | 8.10.8 Scheduler Flow to Queue Mapping              | 122 |

| 8.10.9 Constant Bit Rate Flows                            | 124 |

|-----------------------------------------------------------|-----|

| 8.10.10 Virtual Flows                                     | 124 |

| 8.10.11 Priority Propagation                              | 125 |

| 8.10.11.1 Credit Scheduler Hierarchy Priority Propagation | 125 |

| 8.10.12 Credit Scheduler Flow Control Mechanisms          | 127 |

| 8.10.13 System-Level Color Awareness (System-RED)         | 128 |

| 8.10.13.1 System-RED Mechanism                            | 128 |

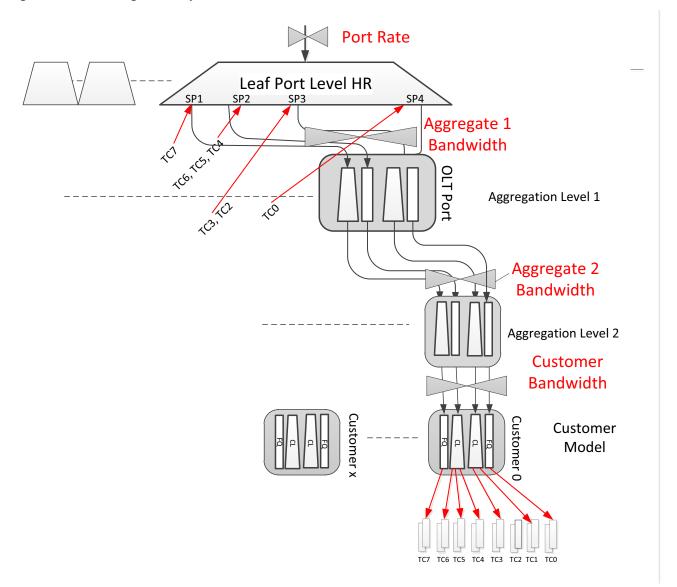

| 8.11 Typical Subscriber Edge Application and Hierarchy    | 128 |

| Chapter 9: CBR Application and CBR Bypass                 | 131 |

| 9.1 CBR Bypass Packet Flow                                | 131 |

| 9.1.1 CBR Ingress Processing                              | 131 |

| 9.1.2 CBR Egress Processing                               | 132 |

| 9.1.3 Packetized CBR Ingress                              | 134 |

| 9.2 CBR Classification and Editing                        | 135 |

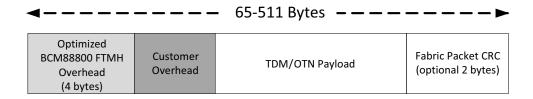

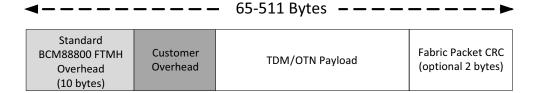

| 9.2.1 CBR Bypass Packet Format                            | 136 |

| 9.2.2 CBR BCM88800 Optimized FTMH Header                  | 136 |

| 9.2.3 CBR BCM88800 Standard FTMH Header                   | 137 |

| 9.3 Backward Compatibility                                | 138 |

| 9.4 Directed Routing through the Bypass Path              | 139 |

| 9.5 Connectivity to Framers and SAR Devices               | 139 |

| 9.5.1 Incoming Rate from Framer to Bypass Path            | 139 |

| 9.6 CBR Bypass Multicast Replication                      | 140 |

| 9.7 Fabric Considerations                                 | 140 |

| 9.8 Delay through Fabric                                  | 140 |

| Chapter 10: Latency Measurements and ECN Marking          | 142 |

| 10.1 Ingress Packet Latency                               | 142 |

| 10.2 End-to-End Latency Measurement                       | 143 |

| 10.3 System Point-to-Point Latency Measurement            | 144 |

| Related Documents                                         |     |

| Glossary                                                  |     |

| · · · · · · · · · · · · · · · · · · ·                     |     |

# **Chapter 1: Introduction**

This document describes the BCM88800 traffic management architecture and fabric adapter. It is intended for system architects and anyone else seeking an understanding of the features and capabilities that the BCM88800 traffic management architecture provides.

**NOTE:** All references to the *device* are references to the BCM88800.

# 1.1 Document Organization

This document includes the following sections:

- Chapter 2, DNX Traffic Management Architecture, describes the DNX traffic management and switching architecture.

- Chapter 3, Functional Overview, describes the main functional blocks in the device and their relationships with one another.

- Chapter 4, Core Overview, gives an overview of the BCM88800 core architecture.

- Chapter 5, Ingress Traffic Management, describes the ingress traffic manager, which is responsible for queuing and replicating packets in DRAM/OCB.

- Chapter 6, Fabric Adapter, describes the fabric interface.

- Chapter 7, Egress Traffic Manager, describes the egress traffic manager (ETM), which is responsible for queuing and replicating packets in on-chip rate adaptation buffers.

- Chapter 8, Egress Credit Scheduler, describes the scheduler responsible for issuing credits to virtual output queues and multicast queues.

- Chapter 9, CBR Application and CBR Bypass, describes how the device may be used for TDM or OTN applications.

- Chapter 10, Latency Measurements and ECN Marking, describes how the device measures the latency of packets flowing through the system.

# 1.2 BCM88800 Applications

The BCM88800 is designed for the following applications:

- Carrier Ethernet core, metro/edge switches, and routers

- Data center switch/router

- Data center interconnect (DCI) router

- Packet transport switches

- Mobile back haul switch/router

- Carrier access aggregation

# **Chapter 2: DNX Traffic Management Architecture**

This section describes the scalable architecture for the traffic management and switching architecture of the BCM88800 network device.

This document focuses on the traffic management and fabric interface of the device. Refer to the *BCM88800 Data Sheet* (see Related Documents) for packet processing and network interface details.

Specifically, descriptions include:

- How unicast and multicast packets are handled by the switching and traffic management system.

- How Fabric Access Processor (FAP) and Fabric Element (FE) switches and forwarding actions are controlled by the embedded packet processor.

- General paradigms for managing multicast traffic within the fabric.

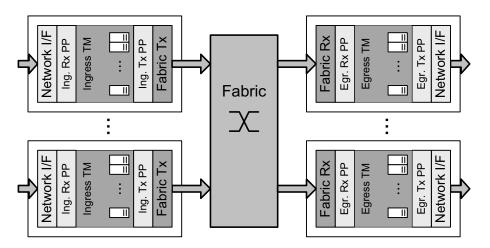

Figure 1: DNX Traffic Management and Switching Architecture

#### Legend:

- · Ing. Rx PP: Ingress Receive Packet Processor

- · Ing. Tx PP: Ingress Transmit Packet Processor

- · Egr. Rx PP: Egress Receive Packet Processor

- Egr. Tx PP: Egress Transmit Packet Processor

- · TM: Traffic Manager

Referring to Figure 1, in the DNX architecture, the device functions include:

- A network interface for transmission and reception (NIF)

- Ingress receive packet processing (IRPP)

- Ingress traffic management (ITM)

- Ingress transmit packet processing (ITPP)

- Fabric transmission and reception (FDRC)

- Egress receive packet processing (ERPP)

- Egress traffic management (ETM)

- Egress transmit packet processing (ETPP)

The device can be directly connected to other devices in a mesh configuration without any fabric. If unicast and ingress multicast is used, the devices can be connected to three peer devices (see Section 2.3.2, Ingress Replication). If mesh multicast is used, the devices can be connected to only two peer devices (see Section 2.3.5, Mesh Replication).

#### 2.1 Packet Flow Overview

This section includes an abridged description of the packet flow.

Packets enter the DNX-based switch through a FAP interface and channel. The incoming interface and channel are used to assign the packet to a reassembly context (ITM-Port) and to select and apply an ingress packet processing procedure that associates the packet to an IPP-Port. The first 144B are sent to the Ingress Receive Packet Processor (IRPP)<sup>1</sup>.

According to the IPP-Port, the IRPP processes the packet headers and generates one or more enqueue requests per packet to the Ingress Traffic Manager (ITM). The ingress packet processor also edits the incoming packet. Packet editing includes appending an internal Fabric Traffic Management Header (FTMH) to facilitate packet handling by the egress device and appending an additional Packet Processor Header (PPH) to facilitate egress packet processing.

The ingress traffic management queues are used as:

- Virtual Output Queues (VOQs) that point to an Output Traffic Management (OTM) port. There is no limit on the number of VOQs assigned to an outgoing port. This enables different QoS models, such as class-based VOQ or flow-based VOQ (for example, a VOQ per customer, tunnel, or PWE) on the same port.

- VOQs to the FAP device level (in the per-FAP egress replication multicast paradigm).

- Fabric Multicast Queues (FMQs) that hold multicast packets that are replicated in the fabric, with no single FAP destination.

Upon dequeue, the Ingress Transmit Packet Processor (ITPP) uses packet information from the packet's Copy-Unique-Data (CUD) to edit the FTMH. Packets arriving at the egress through the fabric are mapped to egress traffic management queues by the egress receive packet processor (ERPP). The ETM maintains up to eight queue-pairs for unicast and multicast traffic per OTM port.

The ERPP uses packet header information, including the FTMH, to generate one or more enqueue requests per packet to the ETM and to filter packets based on egress criteria. The Egress Transmit Packet Processor (ETPP) edits outgoing packets according to packet headers and the OTM port configuration.

<sup>1.</sup> This can be extended by an additional 16B of the segment array in the IP segment routing application. Refer to the *Packet Processing Architecture Specification* (see Related Documents).

### 2.2 Unicast Packet Flow

This section describes the typical ingress-to-egress flow of a unicast packet in the system<sup>2</sup> and the main configurations supporting such a flow.

#### 2.2.1 Ingress Handling

A packet entering the FAP is classified as system unicast (or just unicast) if it is to be forwarded according to a destination system port or a flow ID. The IRPP determines how to forward a packet based on the network header stack. It is also possible to present a packet with an explicit Incoming Traffic Management Header (ITMH) system-header by passing the networking protocol (for example, Ethernet, IP, and so on). This is useful when a CPU injects a packet into the device. The IRPP generates up to four traffic management actions (forwarding, copy-1, copy-2, and copy-3), any of which can be unicast or multicast.

The destination may be a LAG port, in that case, the packet undergoes an additional process of LAG resolution that selects one of the LAG members as the actual destination based on a load-balancing key set by the IRPP. The destination system port or a flow ID, together with the traffic class, determines how a packet is mapped to an ingress Virtual Output Queue (VOQ).

In the DNX architecture, each ingress queue that is used as a VOQ is preassigned to a FAP device in the system and to an Outgoing Traffic Manager port (OTM port) in that same FAP device.<sup>3</sup> An OTM port is typically mapped to a physical network port supported by a FAP in the system.

Prior to storing a packet in On-Chip SRAM Buffer (OCB), the Ingress Receive Packet Processor (IRPP) edits the packet by removing the networking or ITMH headers and appending an FTMH. After reading a packet from OCB/DRAM, the Ingress Transmit Packet Processing (ITPP) stamps the OTM-PORT field in the FTMH according to the queue mapping.

The VOQ requests credits from the OTM port to which it is mapped. The credit request is sent in a Flow-Status message. A VOQ credit request state may be OFF, SLOW, or NORMAL. The state is determined based on the VOQ size and the VOQ credit balance. The Flow-Status message contains a scheduler flow ID that is unique to the receiving egress credit scheduler (see Chapter 8, Egress Credit Scheduler). In other words, at the egress, the scheduler flow ID uniquely identifies an ingress VOQ in the system that is mapped to the credit scheduler.

The OTM port credit scheduler records the request state of each flow. The scheduler grants credits to competing flows in a manner consistent with the port's rate and the scheduling and shaping attributes that the user configures for the flow.

Credits are assigned to VOQs via a credit message sent from the credit scheduler. The credit message identifies the ingress queue to which it is destined.

Upon receipt of credits, the indicated VOQ's credit balance is increased by Credit-Worth. As long as the credit balance is positive, the queue discharges packets. Discharged packets packed or fragmented into fabric cells that are sent to the fabric. For each discharged packet, the credit balance is decreased by the packet size in bytes.

## 2.2.2 Fabric Handling

The fabric simply routes each cell to the destination device indicated in the cell header, as produced by the fabric transmit function.

2. This description assumes that the system has a single traffic management domain (no stacking ports).

Except for VOQs that contain packets that are to be egress replicated. In this case, the VOQ is mapped to an output port of the device, called the Egress Replication Port (output port 255).

#### 2.2.3 Egress Handling

At the egress, the packet is reassembled from the fabric cells and is mapped by the ERPP to an OTM port output queue and traffic class as indicated in the FTMH.

Packets are scheduled out of the egress output queues in a way consistent with the scheduling and shaping attributes set by the user for this queue, OTM port, and interface. Upon reading the packet, the Egress Transmit Packet Processor (ETPP) edits the packet.

## 2.2.4 Configuring a Unicast Flow

To open a unicast flow from a source FAP to a destination FAP and OTM port:

- 1. Allocate a queue (VOQ) at the source FAP and a scheduler flow at the destination FAP.

- 2. Set up the queue parameters.

- 3. Set up the scheduler flow parameters, including scheduler element mapping, priority, weight, shaping rate, and burst.

- 4. Cross-connect the VOQ with the scheduler flow by configuring the queue lookup table at the ingress traffic manager, and the flow lookup table at the egress credit scheduler.

- 5. Configure the ingress packet processor to map packets to the VOQ (according to the value of a destination system port and traffic class or flow ID).

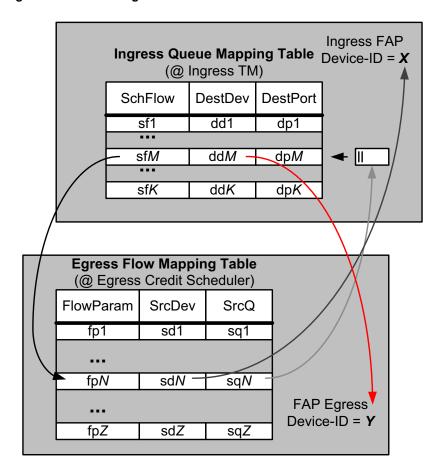

Figure 2: Cross-linking Queue and Scheduler Flow

Figure 2 is an example of a unicast flow from FAP X to FAP Y. At the source FAP, this flow uses queue M (pointed to by sqN in the Egress Flow Mapping Table), and at the destination FAP, this flow is identified by Scheduler Flow N (pointed to by sfM in the Ingress Queue Mapping Table). The OTM port of the flow is defined in the Ingress Queue Mapping Table at the source FAP.

**NOTE:** Figure 2 shows a simplification of the Ingress Queue Mapping Table and the Egress Flow Mapping Table. In the actual implementation, the Ingress Queue Mapping Table has an additional indirection, and queues/flows are mapped in groups. See Section 8.10.7, SEs Grouping and SE-to-Flow Mapping for details on the egress flows to the Queue Mapping Table.

#### 2.3 Multicast Packet Flow

This section describes system multicast packet handling and the configurations needed to support it. Multicasting is the ability to send a packet to a set of OTM ports located on different egress FAP devices or even within the local FAP device. In addition, a packet can be sent several times out of the same OTM port—an operation known as *logical multicast*. In general, each packet copy is tagged with configurable Copy-Unique-Data (CUD), typically used by egress processing logic to uniquely process each packet copy.

#### 2.3.1 Multicast Mechanisms

There are four basic mechanisms in a DNX fabric that enable packet replication:

- Ingress replication

- Fabric replication

- Egress replication

- Mesh replication

These basic mechanisms may be combined on a per multicast-ID basis to support various multicast paradigms.

The multicast replication table has 256K entries. A multicast group may consume several entries according to the number of replications and their encoding.

The 256K-entry multicast replication table is shared both for ingress replication and for egress replication, which can use its entire range

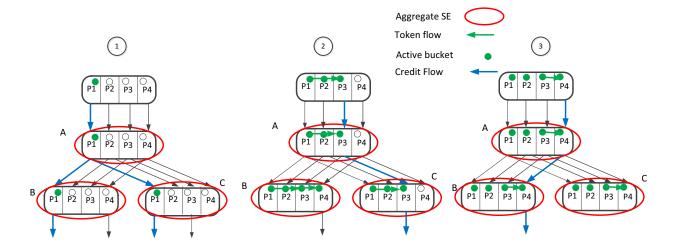

## 2.3.2 Ingress Replication

The device may replicate multicast packets at the ingress.

A packet entering the FAP is classified as system multicast<sup>4</sup> (or just multicast) if it is to be forwarded according to a multicast-ID. Ingress receive packet processing determines that the packet destination is a multicast group.

Ingress replication is configured per multicast ID. The device supports 256K ingress multicast groups. If selected, a packet is mapped by the IRPP to a set of input queues by accessing the multicast table and traversing a linked list of MC-CUDs.

- Egress MC-Rep-ID

- 4. By classifying a packet as system multicast, the packet's destination is specified by a multicast-ID; thus it may be sent out of the system more than once. A system multicast classification does not indicate how a packet is replicated at the ingress, through the fabric, or at the egress. For example, a system multicast packet may be replicated at the ingress to all member FAP devices. In this case, it will perform ingress multicast, fabric unicast, and possibly egress multicast.

The destination of each copy is resolved to a queue, and a packet is enqueued with the corresponding CUD. Ingress replication and enqueue are performed at a rate of a copy per one clock. The queue may point to a remote or local FAP and Destination-System-Port. The special case of Destination-System-Port = 255 stands for the egress replication port. That is, the packet is to be egress replicated, and the VOQs whose destination is no more specific than the egress device.

Ingress-replicated multicast packets are stored only once in the OCB SRAM, with multiple pointers from the VOQ's linked list. However, if stored within the DRAM, each copy is stored separately.

Prior to storing the packet in the OCB, the Ingress Receive Packet Processor (IRPP) removes the networking or ITMH headers and appends an FTMH. After reading the packet from the OCB (or DRAM towards the fabric), if the packet is ingress replicated the Ingress Transmit Packet Processor (ITPP) edits the FTMH by writing the DEST\_PORT field and the CUD. The CUD can be the local multicast-ID at the egress device for egress replication, or it may include one or two Out-LIFs for the egress packet processing.

#### 2.3.3 Fabric Replication

The device may transmit multicast packets to be replicated by the fabric.

Fabric replication is performed on packets residing in Fabric Multicast Queues (FMQs). Queues 0–3 are the default FMQs. All other queues can also be defined as FMQs.

A packet that is classified as system multicast at the ingress, and for which ingress replication (see Section 2.3.2, Ingress Replication) is not specified, is mapped to a fabric multicast queue. Packets may be directed to fabric multicast queues either according to traffic class only or according to traffic class and multicast ID. The device has four dedicated FMQs for class-based queuing. Additional gueues can be allocated as needed.

Packets transmitted from FMQs are replicated by the fabric, typically to all the FAP devices that have ports that are members of the group, as specified by the packet multicast ID. Fabric-replicated packets are fragmented to a fabric cell and are appended with a multicast fabric cell header that includes the multicast ID.

The source FAP sends multicast cells on any of the links that are eligible for fabric multicasting. The list of eligible links is automatically maintained by the FAP, based on the criteria that all known (active) FAPs are reachable through a link. In the FE1 (first stage in a multistage fabric), a list of multicast-eligible links is also automatically maintained (similar to the FAP). The FE1 selects one of the allowed links to transmit a single copy of the cell to the next level of the fabric. In the FE2 (middle stage) and FE3 (last stage of multistage fabric), the fabric multicast ID is used as an index to a multicast replication table that determines the links to which the cell should be replicated (refer to the BCM88790 Data Sheet for details). Thus, cells are replicated within the fabric and are reassembled into packets at several egress FAPs. The multicast replication table for the FEs is set up so that each FAP device with a port that is a group member receives one copy. In the BCM88800, it is possible to use fabric replication for back-to-back systems consisting of two BCM88XXX devices in a back-to-back connection. Fabric replication per destination FAP is performed per cell according to the cell multicast ID. The replication is done in the fabric transmit block in the FAP.

A specified FAP may be excluded from consideration, thus supporting configurations with FAPs that are connected to a subset of the fabric by design.

### 2.3.4 Egress Replication

When a multicast packet is received at the egress FAP by the ERPP, it has an FTMH with a PP-DSP field, and possibly a CUD field. The BCM88800 constructs the PP-DSP from Map[Cell-Header.Dest-FAP[11:0] (2), FTMH.PP-DSP[7:0]}. The ERPP generates one or more enqueue requests to the ETM, according to fields in the FTMH.<sup>6</sup>

If the PP-DSP field in the FTMH is not 255, it indicates egress unicast. In this case, the packet default handling is to enqueue it in a unicast output gueue of the OTM port (mapped from the PP-DSP in the FTMH), as indicated by the OTM-PORT.

If PP-DSP is equal to 255, which indicates egress multicast, the packet is enqueued one or more times in multicast output queues, either by retrieving and traversing an egress multicast linked list and/or by retrieving a multicast bitmap.

Each egress multicast bitmap entry contains an OTM port flag, indicating if the port is a member of the group. The ERPP generates an enqueue request to a multicast output queue<sup>7</sup> of each OTM port indicated in the bitmap.

The CUD associated with each packet may comprise of a single OutLIF, or two OutLIFs (OutLIF and OutRIF). The CUD is extracted from the following:

- The packet FTMH.Multicast-ID-or-MC-Rep-IDX-or-OutLIF[0] field.

- The Egress Multicast-Table linked list pointed by the packet FTMH.Multicast-ID-or-MC-REP-IDX-or-OutLIF[0] field.

- Modular-Data-Base (MDB) Multicast-Replication exact-match data base entry that expands the CUD to two OutLIFs.

If an entry is found in the Multicast-Replication exact-match database, then its entry is taken as the (two OutLIFs) CUD. Otherwise the CUD value in the FTMH or the linked list is taken.

The device supports a configured maximum of egress multicast groups. Refer to the *Packet Processing Architecture Specification* (see Related Documents) for details on the replication tables, the CUD structure, and their exact usage and configuration.

Packets are scheduled out of the output queues. Upon reading, the egress transmit packet processor strips the FTMH, and possibly appends an OTMH.

## 2.3.5 Mesh Replication

In a mesh configuration, the device is directly connected to up to three devices if unicast is supported or two devices if mesh multicast is supported.

Because there is no fabric, the fabric data transmit must perform up to three replications to the local core and two peer devices, according to the multicast ID.

If each fabric Port-Macro is connected to a single peer device, then all mesh replications are performed concurrently in a single clock. Otherwise, only a single mesh replication copy can be generated per clock.

Broadcom 88800-DG108-PUB

16

<sup>6.</sup> When configured to do link layer and network layer packet processing, a PPH is also present. The PPH contains additional fields used by the ERPP.

<sup>7.</sup> Selection between the multicast queues of an OTM port is according to the traffic class and drop eligibility of the packet.

# **Chapter 3: Functional Overview**

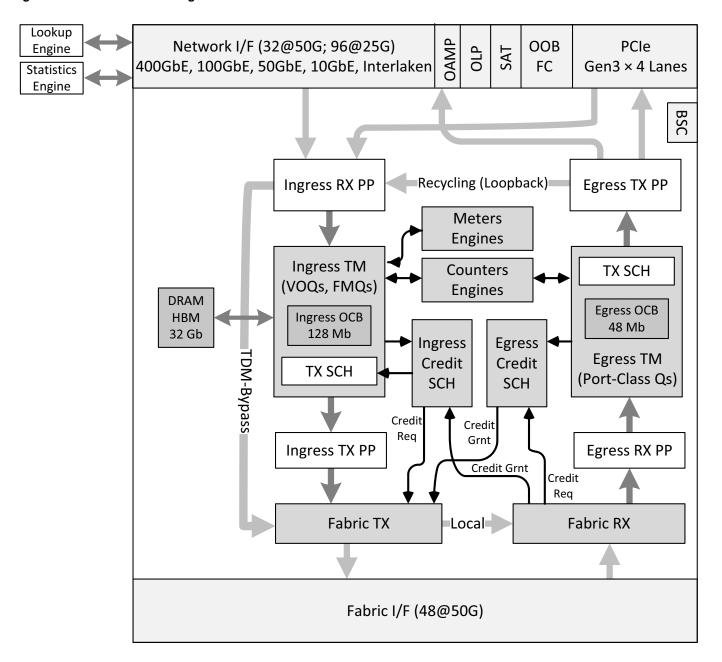

The following figure is a high-level functional block diagram of the device.

Figure 3: Functional Block Diagram

In Figure 3, the main blocks are as follows:

- Network interface (NIF)

- Mix of 10GbE, 25GbE, 40GbE, 50GbE, 100GbE, 200GbE, 400GbE, and Interlaken interfaces

- PCIe CPU interface

- Four-lane Gen 3 interface at a maximum of 8 Gb/s

- Configuration and status access

- Send/receive packets using a built-in DMA engine

- Broadcom Serial Control (BSC) 2-line interface. (BSC is Phillips I<sup>2</sup>C-compatible.)

- Basic device configurations

- Out-of-band flow control interfaces

- Send and receive flow-control indicators

- Ingress receive/transmit packet processor and ELK interface

- Mapping packets to ingress traffic manager queues

- Editing each packet copy

- ELK interface for expanding internal packet processor databases using Broadcom knowledge-based processor (KBP) device

- Ingress traffic manager (see Chapter 5, Ingress Traffic Management)

- Storing packets in internal memory (OCB), packing and storing packets in external DRAM

- Ingress queuing and related packet reassembly

- Managing ingress, VOQs, FMQs, and egress flow queues using internal memory

- Congestion management

- Scheduling towards the fabric

- Ingress credit scheduler (see Section 5.13.2, Ingress Credit Scheduler)

- Track status of queues managed by the ingress traffic manager

- Communicate with egress credit schedulers to obtain credit

- Maintain credits for queues and issue dequeue requests toward fabric from OCB and DRAM and toward DRAM from OCB

- Fabric transmit/receive and fabric interface

- Segment packet to cells

- Send and receive data and control cells

- Fabric routing and redundancy

- Received cells resequencing

- Supporting stand-alone, back-to-back, and Clos-Fabric configurations

- Egress receive/transmit packet processing

- Performs egress replication

- Mapping packets to ETM queues

- Editing each packet copy

- Egress traffic manager (see Chapter 7, Egress Traffic Manager)

- Maintain unicast and multicast queues per OTM port

- Reassemble packets from the fabric

- Schedule transmission from queues to interfaces

- Egress credit scheduler (see Chapter 8, Egress Credit Scheduler)

- Track status of competing VOQs

- Issue credits to VOQs in accordance with configured criteria

- Statistics interface (see Section 7.8, Congestion Statistics Records).

- Push statistics records from Ingress and ETMs

- Counters engines Counters pool

- Meters engines TrTCM meters pool.

**NOTE:** Interfaces, including the NIF, are described in the *BCM88800 Data Sheet* (see Related Documents).

# **Chapter 4: Core Overview**

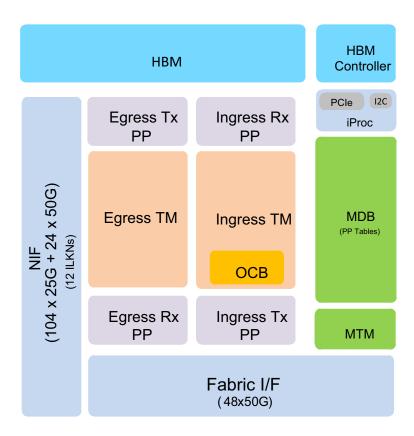

As Figure 4 shows, the BCM88800 is built internally from a single FAP core and some shared blocks, such as the HBM, the multicast table management (MTM), the fabric interfaces, and the packet processing modular database (MDB). This section gives an overview of the core architecture.

Figure 4: Core Architecture

The FAP core is identified by the system with a unique FAP-ID. The FAP core includes an ingress TM and ingress PP as well as an ETM and egress PP.

The following list describes some of the blocks and functions supported by the BCM88800 architecture:

- Network interface (NIF)

- Fabric interface: Ingress packets transmitted from the FAP core toward the fabric interface are segmented to cells, and the cells are load balanced among all active fabric links (and according to the destination's reachability).

- An egress cell received from the fabric interface has to be routed toward the correct egress FAP core. Unicast cells received from the fabric are routed to the egress FAP core according to their destination FAP-ID. Multicast cells are replicated in the fabric, and a single copy is generated per BCM88800 device. The multicast cell received by the

BCM88800 fabric interface has to go through an additional replication stage to create the necessary copies per egress FAP core. For this purpose, the fabric interface includes a multicast replication table per Multicast-ID, indicating which egress FAP core requires a copy of the cell.

- Local switching: The FAP core can locally switch local traffic by switching ingress packets to the egress without going through the fabric links.

- Recycling: Each FAP core can recycle egress traffic back to its ingress. It is not possible to recycle packets between cores.

- OTN circuit switching: OTN packets have a separate path on ingress, which bypasses the ingress portion of the FAP core. A network interface can map Ethernet ports toward the OTN ingress bypass, instead of going through the ingress data pipe. An Interlaken interface can map some Interlaken channels to go through the ingress data pipe, and some to go through the OTN bypass.

# **Chapter 5: Ingress Traffic Management**

## 5.1 Ingress Traffic Manager Overview

The ingress traffic manager has the following features and functionality:

- Reassembly contexts—A maximum of 512 contexts.

- Pool of queues—Categorized as VOQs, FMQs, or Egress Flow Queues (EFQs); a maximum of 128K queues.

- The Ingress TM can process a maximum of 1G packet enqueues and a maximum of 1G packet dequeues per second.

- OCB (SRAM) and DRAM packet memories:

- OCB packet memory 128-Mb memory for a maximum of 64K buffer descriptors (BDs) and 128K packet descriptors (PDs).

- DRAM packet memory Maximum of 32-Gb memory for a maximum of 1M buffer descriptors.

- Multicast Packet replication of a maximum of 4K copies for each stored packet.

- Congestion management:

- Maintain resource consumption statistics per queue.

- Maintain resource consumption statistics according to queue sets (VSQs).

- Maintain resource consumption statistics according to statistics tag, source port, and traffic class.

- Hierarchical Weighted Early Random Discard (WRED), tail drop.

- Link-level flow control 802.3x and priority flow control (for example, PFC 802.1Qbb).

- Configurable flow control generation using a statistics matrix.

- Maintain OCB resources consumption and off-load backlogged traffic from OCB to DRAM.

# 5.2 Ingress Interfaces

The incoming ingress interfaces are as follows:

- Network interfaces (NIFs):

- Support a maximum of 128 ports.

- Support a maximum of 128 Ethernet ports and up to 12 Interlaken interfaces.

- Include a shaper that moderates the total bandwidth that the NIF interfaces.

- Contain indications on whether a packet is TDM (per port).

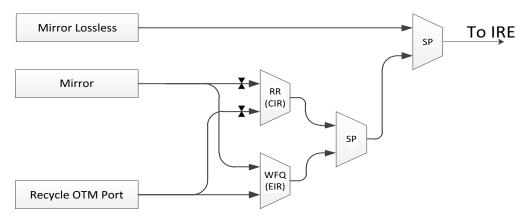

- Recycle interfaces:

- Support up to 256 channels

- 512B width

- Four source contexts:

- Recycling-Port-0

- Recycling-Port-1

- Lossless-Egress-Mirror

- Lossy-Egress-Mirror

- Segments from Recycling-Port-0 and Recycling-Port-1 are interleaved requiring at least two reassembly contexts.

- Segments from Lossless-Mirror and Lossy-Mirror sources are interleaved. (See Section 7.10.8, Recycling Interfaces and Section 5.4, ITM-Ports and Packet Reassembly.)

- A shaper guarantees minimum bandwidth to the Lossy-Mirror source, while excess bandwidth has a lower priority.

- CPU interface

- Internal interface.

- A maximum of 64 non-interleaved channels.

- A shaper guarantees minimum bandwidth to the CPU interface, while excess bandwidth has a lower priority.

- Contains indications on whether a packet is TDM.

- Operation and Maintenance Processor (OAMP) interface

- Internal interface.

- A shaper guarantees minimum bandwidth to the OAMP interface, while excess bandwidth has a lower priority.

- Service Availability Testing (SAT) interface

- Internal interface.

- A maximum of 16 non-interleaved channels (in the range [0 to 255]).

- Offload Processor (OLP)

- Internal interface.

- A shaper guarantees minimum bandwidth to the OLP interface, while excess bandwidth has lower priority.

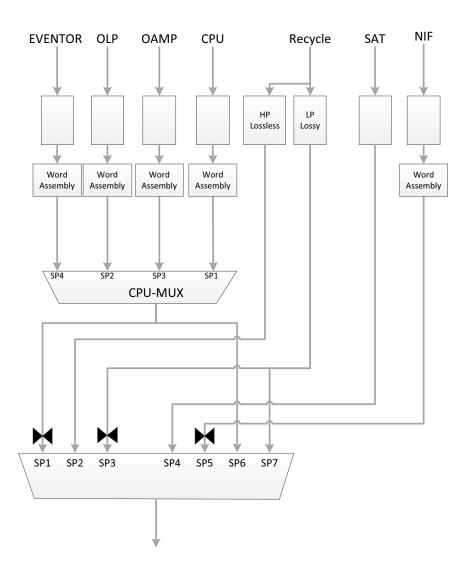

Figure 5: Ingress Interface Arbitration Logic

The arbitration priority between the interfaces is as follows:

- Guaranteed CPU data

- Guaranteed OLP data

- Guaranteed OAMP data

- Guaranteed Eventor data.

- Lossless recycle data

- Guarantees lossy recycle data

- SAT

- Non-TDM NIF data (within shaper limits)

The NIF-port macro can be configured as either a High-Priority or Low-Priority port macro, with a strict priority of retrieving data from the High-Priority port macro. Thus if NIF oversubscription occurs, the packet is dropped first from the Low-Priority Quads.

- Excess (above shaping bandwidth) CPU data

- Excess (above shaping bandwidth) OLP data

- Excess (above shaping bandwidth) OAMP data

- Excess (above shaping bandwidth) recycle data

The network interfaces are organized into three unit types:

- CDU made up of eight 50G SerDes supporting one to eight ports with a maximum port rate of 400G.

- CLU made up of sixteen 25G SerDes supporting one to sixteen ports with maximum port rate of 100G

- ILU supporting one or two Interlaken interfaces, with a rate of 600G or 2 × 300G

Each Ethernet port is allocated FIFOs, and the FIFOs are designated as TDM, HP, or LP.

Each ILKN port has dedicated FIFOs for TDM and data. The data FIFO can be declared as either HP or LP.

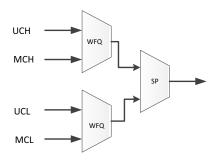

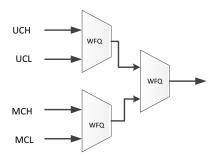

The IRE arbitrates hierarchically between the interfaces as follows:

- SP between TDM, HP and LP.

- RR on the units containing the highest priority

- RR on up to ports containing the highest priority within a selected unit

- On the LP hierarchy: WFQ on units holding LP data. The WFQ weights are configured according to the total bandwidth

of the unit ports

- WFQ on up to eight ports within the selected units that have LP data per 512B segment. The WFQ weights are in the range of 1 to 4, according to the port rates

# 5.3 Network Interfaces (NIF) Oversubscription Management

The overall packet rate and data rate coming from the network interfaces may exceed the device ingress processing performance. If this happens, the IRE asserts flow control toward the network interfaces. The interfaces employ oversubscription management policies using their internal buffers.

The NIF ports are organized into units (CDU, CLU or ILU).

- The CDU unit has a 512KB RX buffer allocation that is partitioned up to 16 FIFO, and up to 8 ports, with a maximum of 3 FIFO per ports.

- The CLU unit has a 512KB RX buffer allocation that is partitioned up to 16 FIFO, and up to 16 ports, with maximum of 3 FIFO per ports.

- The ILU unit has a 256KB RX buffer allocation that is partitioned up to 4 FIFO, and up to 2 ports, with 2 FIFO per ports: one for TDM and one for data.

Thus, the FIFOs per port are as follows:

- An Ethernet unit with one port can have one to three FIFOs per port

- An Ethernet unit with two ports can have one to three FIFOs per port

- An Ethernet unit with four ports can have one to three FIFOs per port

- An Ethernet unit with eight ports can have one or two FIFOs per port

- An Ethernet unit with sixteen ports have one FIFO per port.

The port's total RX buffer can be partitioned into one to three FIFOs with configurable sizes. The FIFOs are designated as either

- TDM RX FIFO (TDM-RX FIFO)

- High-priority RX FIFO (HP-RX FIFO)

- Low-priority RX FIFO (LP1-RX FIFO)

The high-priority RX FIFOs have strict priority for sending data towards the IRE. Incoming packets are classified into four NIF priorities (see Section 5.3.1, NIF Priority Assignment). Each NIF priority is mapped to one of the RX FIFOs.

Four thresholds are defined on the RX FIFO level: one threshold per NIF-Priority. If the FIFO level at SOP is higher than its priority threshold, the packet is dropped, and a NIF-drop counter per FIFO is incremented.

A packet may be admitted at SOP, but there may be no room to receive the full packet. In that case, the packet is sent to IRE with an error indication and is counted by an IRE-Drop counter per reassembly context.

The lowest NIF-Priority has the lowest drop threshold, and the highest NIF-Priority has the highest drop threshold. If NIF oversubscription occurs, the FIFO level rises, and the lower NIF-priorities packets are discarded first.

#### **5.3.1 NIF Priority Assignment**

For ports receiving traffic with ITMH system headers (TM ports), the Traffic-Class (3) and Drop-Precedence (2) fields are mapped to 2b NIF-priority and a 1b TDM indication.

The BCM88800 employs an elaborate parsing and NIF-Priority resolution algorithm. When an Ethernet packet is received, the first 128B of the packet are parsed, yielding a 2b NIF priority and a TDM indication that determines the RX FIFO and its threshold.

For Ethernet ports, the parser parses the packet networking header stack, identifying:

- Ethernet header with up to two VLANs + EtherType (outer-tag size may be 4B, 6B, or 8B)

- Up to eight MPLS labels, searching for labels indicating control traffic

- IPv4/IPv6 header

A configuration per port, the NIF-priority is mapped from:

- IPv4/IPv6 DSCP (if it exists)

- MPLS EXP (if it exists)

- Inner VLAN PCP/DEI (if it exists)

- Outer VLAN UP (if it exists)

- Port default

Additionally, packets identified as control-plane protocol packets are assigned a highest priority (overriding a previously assigned priority). The supported control protocols include:

- ARP request/reply

- IEEE slow protocols, CFM, MRP, STP

- IGMP

- DHCP

- BFD

- Geneve/VxLAN OAM

The control packets are identified by two mechanisms:

- MAC DA and EtherType match:

- A 4b EtherType-Code is derived by matching the packet EtherType to 16 values of EtherType.

- Matching one of four configurations of (MAC-DA value and MAC-DA-Mask), EtherType-Code & (EtherType-Mask).

MAC-DA-Mask is configured at bytes resolution, EtherType-Mask is configured at bit resolution. Matched packets are assigned priority 3 (highest).

- Flexible TCAM match:

- Per EtherType-Code, 4 bytes at byte resolution from the packet header are selected. These bytes may be selected

relative to the start of the packet, to the end of the Ethernet header, or to the end of the header after the Ethernet

header.

A 36b key is constructed by selecting {EtherType, Byte-0, Byte-1, Byte-2, Byte-3} and is looked up at 36b wide

TCAM with 32 entries. If there is a match, the packet is assigned NIF-Priority according to the TCAM result.

## 5.4 ITM-Ports and Packet Reassembly

The ingress traffic manager maintains up to two packet reassembly contexts per ITM-Port. Interleaved packet fragments from different interfaces and channels are reassembled into full packets. Each NIF port may maintain three FIFOs: TDM, LP-Data, and HP-Data. TDM FIFO is not used in the device. The LP-Data and HP-Data FIFO may be mapped to two different reassembly contexts per ingress interface. The reassembly context is mapped to the In-TM-Port that is used for LLFC-VSQ and PG-VSQ and for In-TM-Port packet size compensation.

The ingress traffic manager supports 512 reassembly contexts from the following input interfaces:

- NIF: 48 ports that may be a mix of XAUI/XLAUI/CAUI/MAUI or Interlaken interfaces, and may be channelized.

- Recycle: There are two recycling interfaces to the ingress path. The recycling OTM-Ports (channels) are partitioned into two reassembly contexts. (Even if it is not channelized, the recycling interface needs to be partitioned to two contexts.)

- Every occurrence of egress port or [port × VLAN] mirroring requires a separate reassembly context on the recycling interface since the mirrored packets from different egress OTM-Ports are interleaved.

- Every OAM session requires a separate reassembly context on the recycling interface since the OAM packets are interleaved. If OAM/trap packets are smaller than a 256B segment, the restriction can be waived.

- Interlaken interface: Because the Interlaken interface does not support channel interleaving, it uses only a single context. However, in special cases, it can allocate a reassembly context per channel (for example, when a specific channel requires a different per In-TM-Port size compensation.

- CPU: May be channelized.

- Off-Load Processor (OLP).

- Operation And Maintenance Processor (OAMP).

- Service Availability Test (SAT) module.

- Eventor.

The large number of reassembly contexts enables interleaving packets from different network ports and enables interleaving packets over the internal recycling and CPU interfaces.

## 5.5 Packet Memory

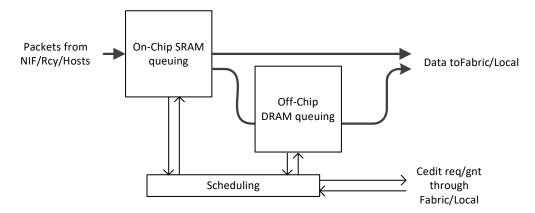

At the heart of the device ingress data path architecture is the combination of the on-chip buffering (OCB) followed by DRAM buffering, as the following figure shows. The DRAM is implemented by two High Bandwidth Memory (HBM) modules.

Figure 6: Ingress Memory Subsystems

Incoming packets are always assembled and written into the on-chip buffers that are added to the VOQ's SRAM portion. However subsequently, VOQ packets may be read from the on-chip memory and then packed into a packet-bundle that is written to the DRAM, then re-enqueued to the VOQ's DRAM portion.

## 5.6 SRAM Packet Memory

The SRAM packet memory is 128 Mb of on-chip buffering. A packet is stored in multiple buffers and consists of a linked list of a maximum of 64 SRAM buffers. An SRAM buffer contains data of only one packet. The VOQ consists of a linked list of packets, and each packet has a Packet-Descriptor (PD). There are 128K PDs. There are 128K VOQs.

Ingress multicast packets and snooped/mirrored unicast packets are stored only once in the SRAM memory. The packet is linked to multiple VOQs, each with its own CUD. All SRAM buffers can support multicast packets. Each SRAM buffer has a User-Count that is updated whenever the packet is linked/unlinked to a VOQ. User-Count = 0 indicates the last reference to the packet has been dequeued and that the buffers can be freed.

## 5.7 DRAM Packet Memory

The DRAM is used as an oversubscription buffer for storing oversubscribed traffic.

The DRAM packet memory consists of one HBM modules. Each HBM module is capable of buffering 4 GB. The DRAM memory space is partitioned into 1M DRAM buffers of 4 KB, encompassing a maximum of 4 GB. Packets are stored within the DRAM in DRAM bundles. The benefits of packing multiple packets into a large DRAM buffer is that the capacity of the DRAM buffer is unaffected by packet size.

The overall DRAM bandwidth (~4 Tb/s) is lower than the input bandwidth (~4.8 Tb/s) because it serves only to store oversubscribed traffic, providing at least ~16 ms of buffering (for 2 Tb/s input bandwidth).

When SRAM resources become scarce, packets are moved from the on-chip SRAM to the DRAM from VOQs that are congested. Multiple packets from the same VOQ are consecutively dequeued from SRAM to optimize an effectively full DRAM bundle and are packed into DRAM buffers. For ingress multicast copies and unicast snoop/mirror copies, the DRAM has separate storage for each packet copy (with its CUD).

#### 5.7.1 Data Integrity of Packet Memory

The following sections describe the data integrity of the packet memory.

#### 5.7.1.1 SRAM-Packet-CRC

By configuration, CRC16 is calculated per packet, and 2B are appended to the end of the packet.

When the packet is read from SRAM, the CRC is verified. If an error is found, the calculated CRC is flipped (to indicate the SRAM is the source of the error), but it is still sent through the fabric to the egress device to be discarded at the egress device.

#### 5.7.1.2 DRAM-Packet-CRC

For every packet written to the DRAM, CRC16 is computed on the packet and on the FTMH. The CRC is checked for each packet when it is read from DRAM. If a CRC error occurs, the packet is still sent. There are two counters for CRC errors:

- Flipped CRC—Indicates that the error did not originate within the DRAM system; it originated in the SRAM.

- Other error—Indicates an error in the DRAM system.

The CNI bit in the FTMH may be set after a DRAM dequeue; then the CRC is updated before the packet is sent to the fabric.

At the egress device, the packet CRC is rechecked. If the CRC within the packet is the flipped CRC, this indicates that the error originated within the ingress device; otherwise, it indicates that the error occurred within the fabric.

#### **5.7.1.3 DRAM-CUD CRC**

A 16b CRC is computed on TC[3], Packet-Size[14], and Copy-Data[47:23] (excluding ECC).

#### 5.7.1.4 DRAM-ECC

ECC7 is used to cover TC[3], Packet-Size[14], and Copy-Data [31:7] (including the CUD CRC). ECC is 1b error repair and 2b error detect. If an unrepairable packet ECC error occurs, the rest of the bundle is discarded.

#### 5.7.1.5 DRAM-Opportunistic Last Buffer CRC-16

Bundles are written to the DRAM using several DRAM channels, where each channel writes and reads 64B segments. Each segment is written to a different DRAM bank in 32B bursts.

CRC16 is used to opportunistically identify defective buffers. Opportunistic-Buffer-CRC is added when the number of valid bytes in the last buffer of the bundle is less than 4 KB - 2. Additionally, the Opportunistic-Buffer-CRC is added if there is a space in the last 32B DRAM word or if the number of valid bytes in the last buffer is above a configurable threshold.

Upon DRAM read, if present, the Opportunistic-Buffer-CRC is calculated and compared to the received CRC. If there is a mismatch, the erroneous buffer is not freed to the Free-Buffer-List. The erroneous buffer and the CRC banks are placed in a quarantined buffer list and may be freed only by software. An error counter is increased, an interrupt is sent to the CPU, and the extracted packets are eventually dropped at the egress device. Marking both the faulty buffer and the DRAM bank number enables the system manager to track corrupted banks and pinpoint the problem faster.

#### 5.7.1.6 Erroneous DRAM Buffer Reclamation

Buffers associated with erroneous packets are not reclaimed (that is, not returned to the list of empty buffers) and are conveyed to the CPU through an interrupt assertion. The CPU can then test the buffer by writing to and reading from it, or by collecting statistics about it. The CPU can either decide to reclaim the buffer or not. Buffer reclamation by the CPU is accomplished by writing the buffer number to a dedicated register and triggering a buffer reclamation action to be performed by the device.

## 5.8 Packet Ingress Walkthroughs

This section contains packet ingress walkthroughs for the following:

- Packet enqueue to OCB SRAM

- Packet dequeue from OCB SRAM to fabric

- Packet transmit from OCB SRAM to DRAM and packet dequeued from DRAM to fabric

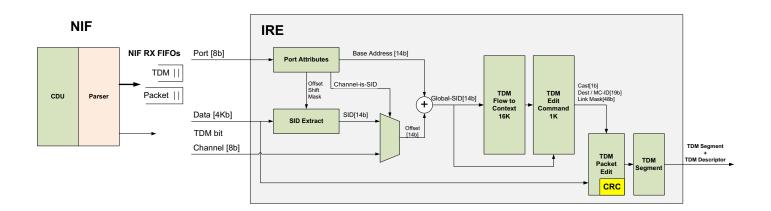

#### 5.8.1 Ingress Enqueue Walkthrough

Packets arrive from the eight packet interfaces (NIF, Egress-Recycling-0, Egress-Recycling-1, CPU, OLP, OAMP, Eventor, and SAT). The packets are assembled in 256 contexts in the Ingress Receive Editor (IRE). The NIF and Recycling interface channels operate in either full-packet mode or in segment-interleaved mode. In segment-interleaved mode, a packet belonging to different channels with the same interface arrives interleaved at 512B segments. When a packet is presented, it is sent to the Ingress Receive Packet Processor (IRPP) with the Port-Termination-Context (PTC). The packet rate presented to the IRPP may be shaped to avoid oversubscription of the External Lookup device (ELK) interface. The IRPP processes the packet headers, and returns:

- Edit information

- TM command

The editing command is performed, and the packet is sent to the SRAM-Packet-Buffer (SPB) for reassembly. The SPB processes 512B every clock. The SPB allocates SRAM buffers for the packet, writes the packet in them, and a TM-Command is send to the Congestion-Management (CGM) module.

The SPB tracks the number of available buffers. According to configurable thresholds on the level of free buffers, it asserts state AF1 (Almost-Full-1), AF2, or AF3:

- AF1—Stop reassembly of new packets from configurable TC and interfaces.

- AF2—Stop reassembly of new packets from all sources.

- AF3—Stop allocating new buffers and discard even partially assembled packets.

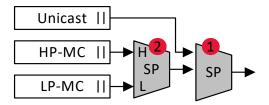

The CGM receives the TM-Command and sends it to the Metering-Processor, returning an updated Ingress-DP and Egress-DP. The TM-Command is classified into one of three TM-Actions FIFOs based on unicast/multicast, TC and DP. The TM-Action FIFOs are: Unicast, HP-Multicast, and LP-Multicast.

The meter processor resolves the DP of the packet. The packet is placed into one of three TM-action queues. Multicast packets are mapped to either HP-MC or to LP-MC according to a configurable mapping of the packet TC.

The TAR resolves TM-Action Destination, TC, DP, Copy-Action-0, Copy-Action-1, Copy-Action-2, and LAG-LB variables, to per-copy enqueue requests, specifically:

- Replication of Ingress Multicast copies: as described in Section 2.3.2, Ingress Replication for multicast packet flows.

- Resolving destinations to queues, including.

- Unicast resolution of Destination-Port and TC as described in Section 2.2.1, Ingress Handling.

- Unicast LAG resolution

- Copy-Action-0 1, and 2 command processing:

- Resolving destination

- Probabilistic sampling

- Prefix cropping

- Overriding DP and TC

- Overriding or retaining statistics object

- Updating the packet engueue associated information (for example, Out-LIF, DP, and TC for Snoop/Mirror copy).

The TAR returns to the CGM Packet-Enqueue-Request that is evaluated for admission by the CGM based on available resources, queue-size, and queue parameters, resulting in an admit/drop decision. If the packet is admitted, the queue number and start-SRAM buffer, along with additional packet information, are passed to the SRAM-Queue-Manager (SQM). Otherwise, the packet copy is discarded. If all packet copies have been discarded, then the packet's Start-Buffers are sent to the SPB to be freed. The SQM allocates a Packet-Descriptor (PD) and links it to the queue.

Upon SRAM enqueue, the queue size is evaluated (including a possible portion in the DRAM). Flow-Status messages are sent to the egress scheduler.

### 5.8.2 SRAM to Fabric Dequeue Walkthrough

Credits are received from the egress end-to-end credit scheduler over the interface. The credit is associated with a VOQ which is configured with 3b IPS-priority, and as either high or low priority. Incoming credits are organized in several contexts according to a 3b IPS-Priority and unicast or multicast. According to a scheduling policy among the credit contexts, credits are retrieved; the credit is added to the queue's credit balance. When credit balance is positive, a Dequeue-Command with Dequeue-Command-Bytes is issued to the SRAM queue manager. The SRAM queue manager traverses the queue, dequeuing several packets.

- Until the queue becomes empty

- OR until the Dequeue-Command-Bytes are exhausted

- OR an amount of packets optimized for efficient packing the dequeued packets into fabric cells.

Each packet issues Dequeue-Transmit commands to the SRAM buffer manager. SRAM Dequeue-Transmit commands are managed in multiple queues and are organized according to priority (HP/LP), unicast/multicast, and destination (local interface, or fabric, or mesh peer). The processing of the Dequeue-Transmit commands is controlled by a scheduling hierarchy, and is shaped according to the amount of fabric links. Queue sizes are updated, and corresponding Flow-State messages may be sent.

The SRAM buffer manager reads the packet, updates the SRAM buffer user-count, and frees the buffer. The packet data is read and sent to the Ingress Transmit Packet Processor (ITPP) and then to the Fabric Transmit queues that have multiple contexts according to the source (SRAM/DRAM), destination (fabric/local), and priority (HP/LP). Multiple packets may be dequeued until the queue's credit balance is exhausted or until the queue is emptied. The packets are dequeued in multiple bundles of packets whose cumulative size is optimized for fabric cell packing. The packets are stored in fabric or local transmit-queues. From a transmit-queue toward the fabric, an entire bundle of packets is presented to the fabric to be packed into fabric cells. From a transmit-queue toward the local interface, packets are presented one by one. A scheduling hierarchy determines from which context to extract data toward the fabric/local interface.

## 5.8.3 DRAM Enqueue and Dequeue Walkthrough

Upon each packet SRAM enqueue/dequeue, the Congestion Manager (CGM) informs the Ingress Packet Scheduler (IPS) whether the queue's data needs to be evacuated to the DRAM (a state also referred to as DRAM-Bound). The decision is based on the amount of SRAM resources and the queue attributes, that is, low-priority queues are evacuated first. If the queue is DRAM-Bound, an SRAM-to-DRAM credit is issued and stored in SRAM-to-DRAM credit dequeue context.

When the SRAM-Queue-Manager receives a DRAM-Transmit-Command, it dequeues a bundle of packets from the VOQ that can pack efficiently into a maximum of three 4 KB DRAM buffers.

The Packet-Transmit commands are stored in a DRAM-Dequeue-FIFO toward the SRAM buffers. Packet-Transmit commands are processed by the Packet Transmit-Scheduler at prescribed shaping rates and are a lower priority than SRAM dequeues towards the fabric. The bundle's packets are dequeued from the OCB SRAM and are sent to the Ingress-Transmit-Processor (ITPP) and then to the DRAM-Packet-Buffer. The packets are packed into a bundle.

Subsequent credits arriving to the queue are handled by the ingress packet scheduler; once the credit balance is positive, it issues a Bundle-Dequeue-Command to the DQM. The bundle's DRAM buffers are read and reassembled from the DRAM channels. The bundle is reassembled and checked for integrity errors. Then, the bundle is parsed to its component packets. The packets within the bundles are partitioned into *fabric bundles* that are optimized for fabric cell packing and are sent to the fabric Transmit-Queues to a FIFO corresponding to the packet's destination (local/fabric/mesh), packet's priority (HP/LP), sources (DRAM), and cast (UC/MC).

### 5.9 Destination Resolution

Packet copy destinations are resolved to queues. The destination is defined by one of the following scenarios:

- The destination is a non-LAG Destination System-Port (DSP).

- The destination is the DSP, and the DSP is LAG.

- The destination is a flow-ID within a non-LAG DSP.

- The destination is a flow-ID within a LAG DSP (also known as an aggregate-flow-ID).

- The destination is a DSP in another TM domain that is accessible through a single DSP (either a LAG or a singleton).

- The destination is a DSP in another TM domain that is accessible through DSPs (either a LAG or a singleton).

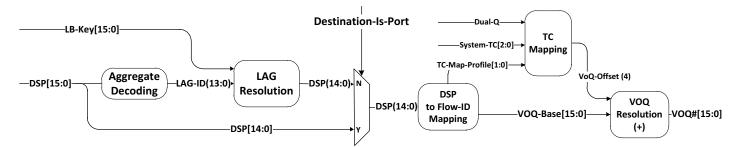

#### 5.9.1 DSP Queue Resolution

If the DSP is a LAG, then a single member is elected according to the LAG-member procedure.

For each DSP, there is a block of one, two, four, or eight VOQs facing towards the DSP according to its System-TC. The number of VOQs and their TCs is determined by the TC-Mapping-Profile of the DSP. The DSP is mapped to VOQ-Base and TC-Mapping-Profile.

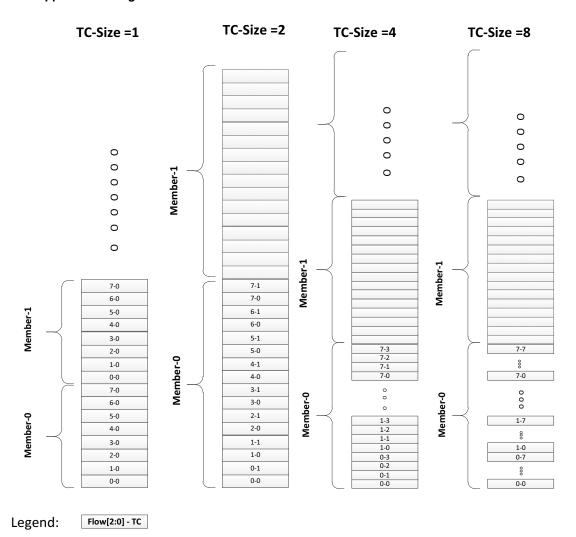

The following figure describes the resolution process.

Figure 7: DSP to VOQ Resolution

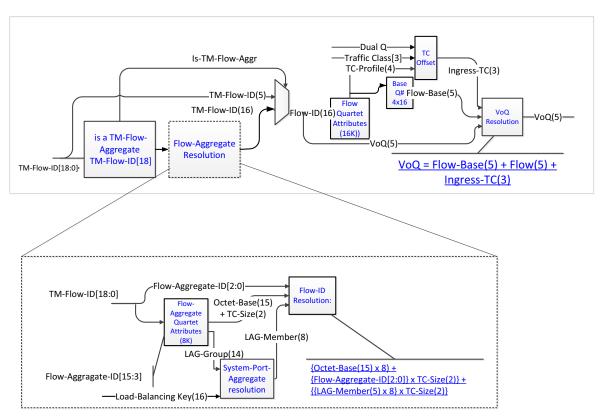

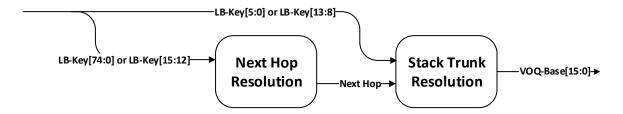

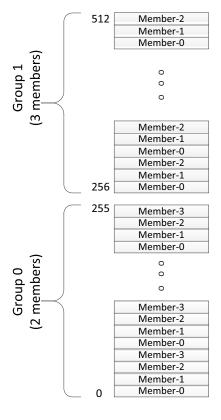

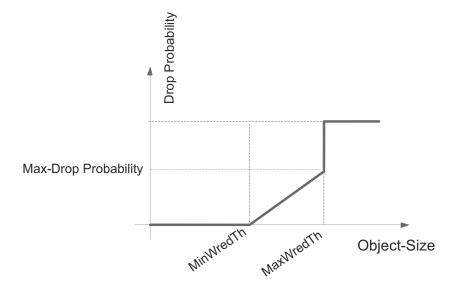

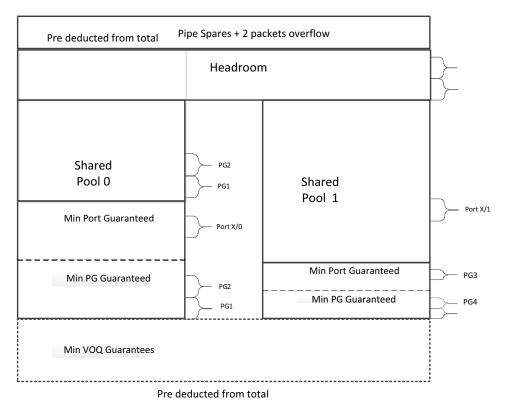

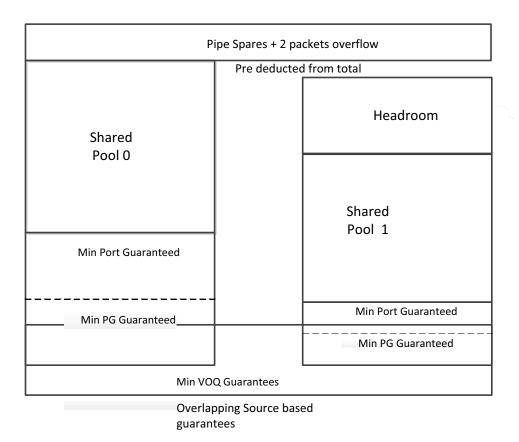

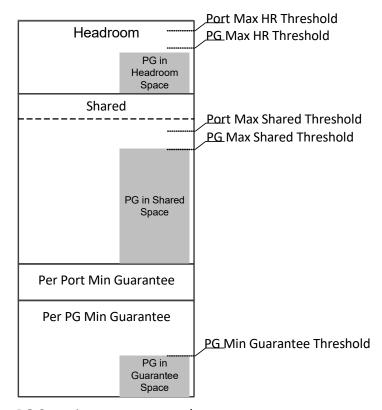

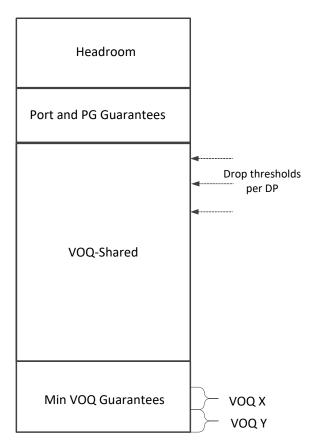

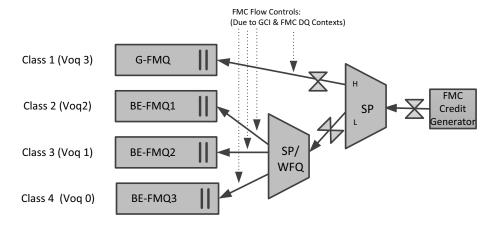

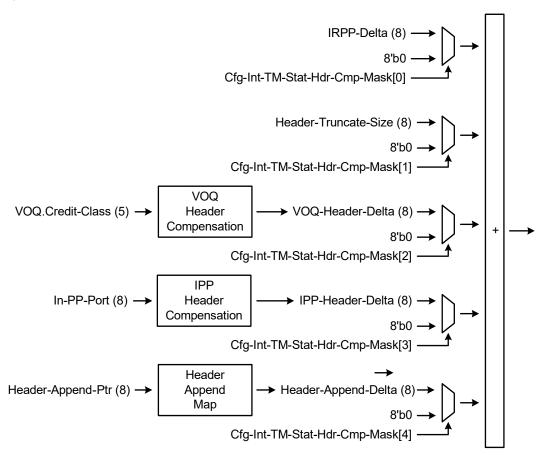

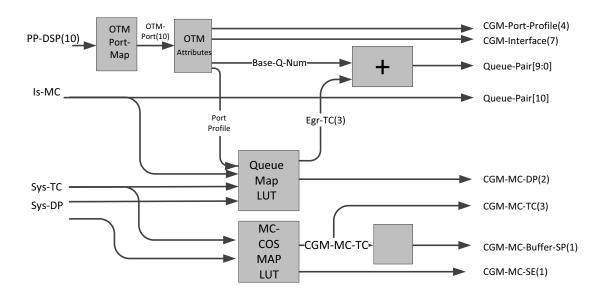

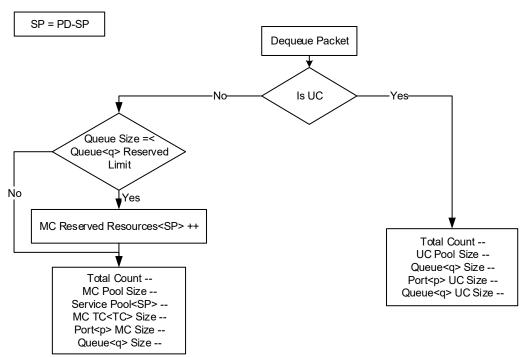

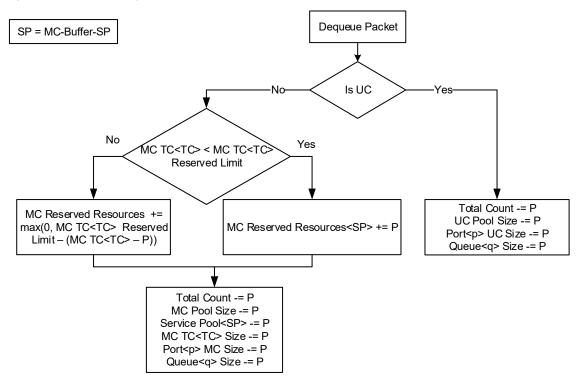

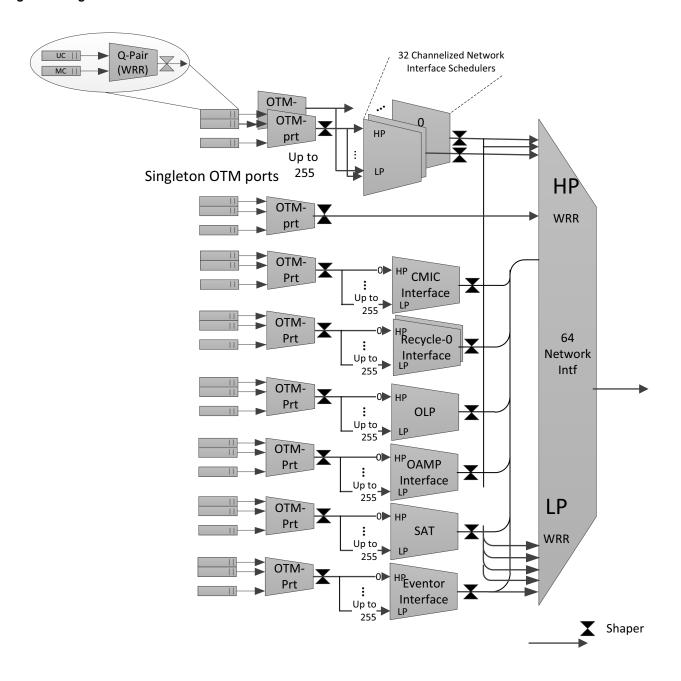

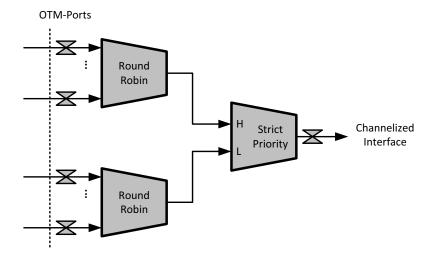

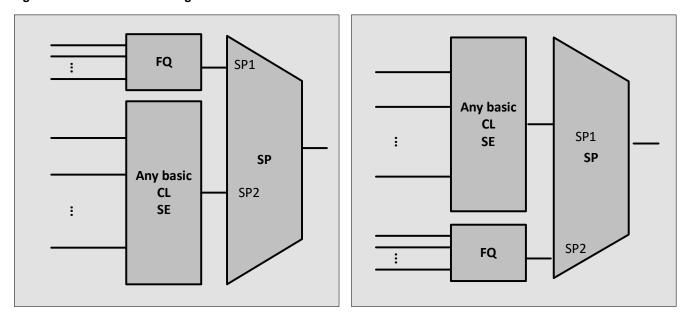

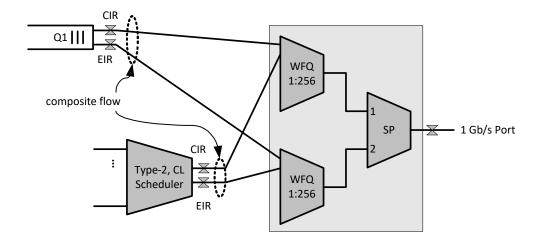

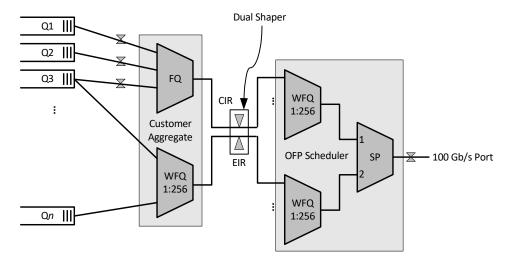

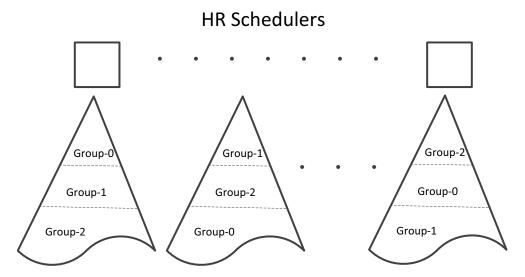

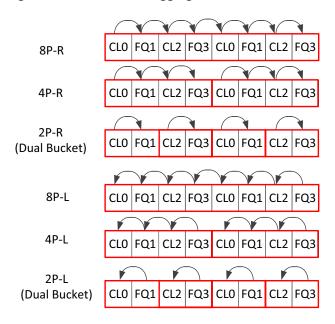

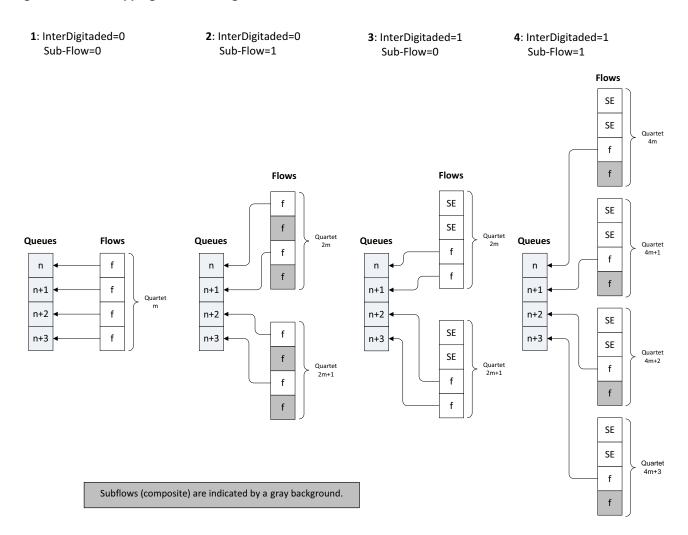

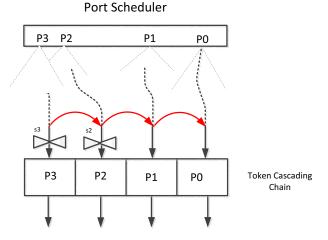

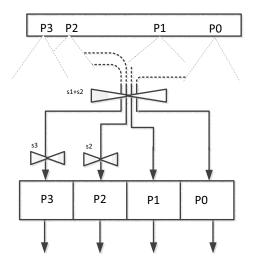

#### 5.9.2 Flow to Queue Resolution