# **BCM88480**

# 800-Gb/s Integrated Packet Processor and Traffic Manager Single-Chip Device

#### Overview

The Broadcom<sup>®</sup> BCM88480 series is an optimized switching solution for fifth generation (5G) mobile backhaul, cell-site routing transport and data center applications, enabling switching platforms with a mix of Ethernet, Optical Transport Network (OTN), and Flex Ethernet (FlexE) ports.

The product series belongs to the seventh generation of the DNX scalable switching product line and processes up to 800 Gb/s of traffic, operating at Layer 1 through Layer 4.

The BCM88480 is the first in the StrataDNX™ product family to integrate FlexE. The FlexE core provides an additional way to optimize the uplink bandwidth in backhaul, transport, and data center interconnect (DCI) applications. FlexE clients can manage the bandwidth allocation per service. An integrated FlexE cross-connect unit minimizes the latency of sensitive services, such as ultra-reliable and low-latency communication (URLLC), through a dedicated high-speed switching plane.

Being optimized for 5G mobile backhaul, the BCM88480 implements a fully featured, large-scale network slicing solution at wire speed. It supports the fast creation of slices and the isolation of these services in the converged network. When configuring network slices, the user can leverage the flexible forwarding classification, virtual databases, and large-scale segment routing. Bandwidth management per-slice is programmable, and supports hierarchical quality-of-service (HQoS), scheduling, and shaping. Latency-sensitive slices, such as radio traffic, can be assigned low-latency and lossless resources.

The Elastic Pipe™ packet classification engine is software programmable, with built-in support for carrier and data center networking applications. The large on-chip classification databases can be extended using an external knowledge-based processor (KBP) from Broadcom.

The traffic manager integrates deep-packet buffers with a distributed scheduling scheme that allows state-of-the-art HQoS, transmission scheduling per-customer, and per-service, as well as tunneling and overlay networks. Flexible flow control mechanisms support Priority-based Flow Control (PFC), Enhanced Transmission Selection (ETS), and Explicit Congestion Notification (ECN).

The integrated bypass path delivers latency-sensitive services, such as OTN, Time Division Multiplex (TDM), or mobile traffic.

#### **Features**

- Seventh-generation Dune scalable fabric access processor (FAP) product line.

- Flexible network interface:

- 1GbE, 10GbE, 25GbE, 40GbE, 50GbE, 100GbE, 200GbE, and 400GbE interfaces.

- Support for a mix of OTN (ODU) and Ethernet ports on the same device.

- FlexE network interface:

- Flexible line rate.

- Large number of FlexE clients.

- Traffic manager:

- On-chip buffer with off-chip deep-buffering option.

- Hierarchical memory management.

- Programmable, hierarchical scheduling.

- Compliant with scheduling and shaping standards, including Metro Ethernet Forum (MEF) and Broadband Forum standards.

- Flexible and software-programmable Elastic Pipe packet processor:

- Bridging, routing, Multiprotocol Label Switching (MPLS), Virtual Private LAN Service (VPLS), Layer 2 virtual private networks (L2VPNs), Layer 3 virtual private networks (L3VPNs), and Operations, Administration, and Maintenance (OAM).

- MPLS and IPv6 segment routing.

- Data center tunneling encapsulations including Virtual Extensible LAN (VXLAN), Network Virtualization using Generic Routing Encapsulation (NVGRE), and Generic Network Virtualization Encapsulation (GENEVE).

- Built-in support for data center, carrier, and metro.

- Ethernet and packet transport applications.

- Large on-chip tables with off-chip expandability.

- Bypass mode:

- Delivery of latency-sensitive services, such as OTN, TDM, or mobile traffic.

- Unified data plane for OTN and Ethernet.

- Precision Time Protocol (PTP) IEEE 1588, Synchronous Ethernet (SyncE).

- Time-sensitive network (TSN) support.

- In-band management.

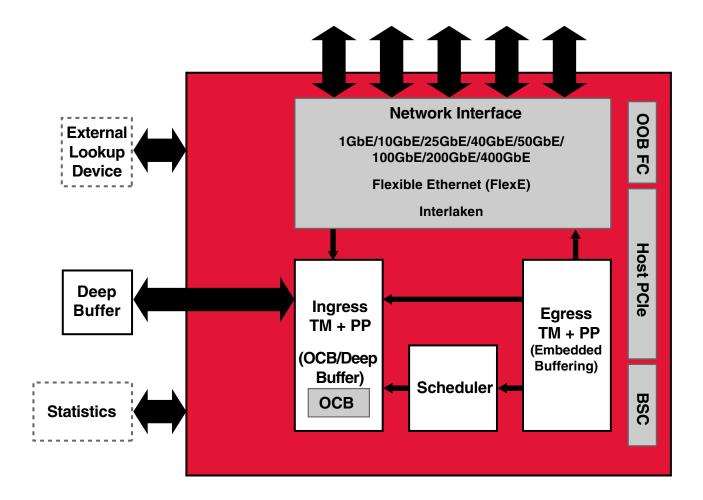

Figure 1: Functional Block Diagram

# **Table of Contents**

| Chapte | er 1: Introduction                                                 | 6  |

|--------|--------------------------------------------------------------------|----|

| 1.1 F  | eatures                                                            | 6  |

| 1.2 D  | Device Overview                                                    | 8  |

| Chapte | er 2: System Configurations                                        | 11 |

| 2.1 S  | Stand-Alone or Centralized Switch                                  | 11 |

| 2.2 F  | lexE Adapter                                                       | 12 |

| Chapte | er 3: System Interfaces                                            | 13 |

|        | letwork Interface                                                  |    |

| 3      | 3.1.1 Ethernet Ports                                               | 15 |

|        | 3.1.1.1 400GbE Port                                                | 19 |

|        | 3.1.1.2 200GbE Port                                                | 19 |

|        | 3.1.1.3 100GbE Port                                                | 20 |

|        | 3.1.1.4 50GbE Port                                                 | 20 |

|        | 3.1.1.5 40GbE Port                                                 | 21 |

|        | 3.1.1.6 25GbE Port                                                 | 22 |

|        | 3.1.1.7 12GbE Port                                                 | 22 |

|        | 3.1.1.8 10GbE Port                                                 | 22 |

|        | 3.1.1.9 1GbE Port                                                  | 22 |

|        | 3.1.1.10 Mixed Port Types on PM50                                  | 23 |

|        | 3.1.1.11 Mixed Port Types on PM25                                  | 25 |

| 3      | 3.1.2 FlexE                                                        | 26 |

| 3      | 3.1.3 Interlaken                                                   | 27 |

|        | 3.1.3.1 Interlaken SerDes Supported Rates and Electrical Standards | 27 |

|        | 3.1.3.2 Interlaken Receive Burst Rules                             | 28 |

|        | 3.1.3.3 Interlaken Transmit Burst Rules                            | 28 |

|        | 3.1.3.4 Interlaken In-Band Flow Control                            |    |

|        | 3.1.4 Bandwidth Provisioning of the Network Interface              |    |

| 3.2 E  | xternal Lookup Engine                                              | 30 |

|        | Out-of-Band Flow Control                                           |    |

|        | Synchronous Ethernet                                               |    |

|        | 3.4.1 Transmit Clock                                               |    |

|        | 3.4.2 Recovered Clock                                              |    |

|        | EEE 1588                                                           |    |

|        | 3.5.1 BroadSync External Interfaces                                |    |

|        | Statistics Interface                                               |    |

|        | xternal DRAM Packet Buffer                                         |    |

| 3.8 C  | PU Interface                                                       | 37 |

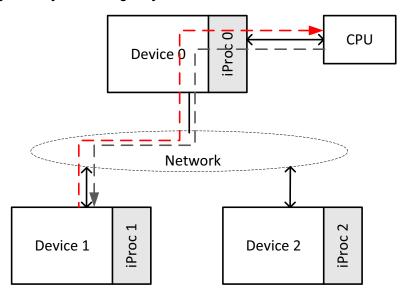

|      | 3.8.1 Remote CPU Support                                  | 38 |

|------|-----------------------------------------------------------|----|

|      | 3.8.2 Remote Packet Operations                            | 39 |

|      | 3.8.3 PCIe Interface                                      | 39 |

|      | 3.8.4 MIIM                                                | 39 |

|      | 3.8.5 UART                                                | 39 |

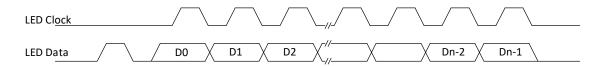

|      | 3.8.6 LED Interface                                       | 40 |

| Chap | pter 4: Pin Signal Description                            | 41 |

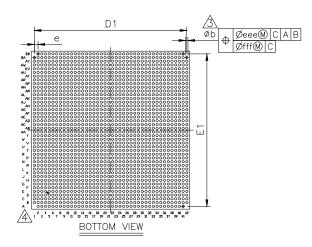

| 4.1  | Pin List and Pin Map                                      | 41 |

| 4.2  | Pin I/O Type Description                                  | 41 |

| 4.3  | Pin Description – Grouped by Function                     | 42 |

| Chap | pter 5: Electrical Specifications                         | 59 |

| 5.1  | Absolute Maximum Ratings                                  | 59 |

| 5.2  | Recommended Operating Conditions                          | 60 |

|      | 5.2.1 Recommended Operating Voltage                       | 60 |

|      | 5.2.2 Recommended Operating Voltage Range for DC Supplies | 61 |

| 5.3  | Device Power Consumption                                  | 62 |

| 5.4  | Power Supply Filtering                                    | 63 |

| 5.5  | Power-Up, Power-Down, and Reset Sequence                  | 64 |

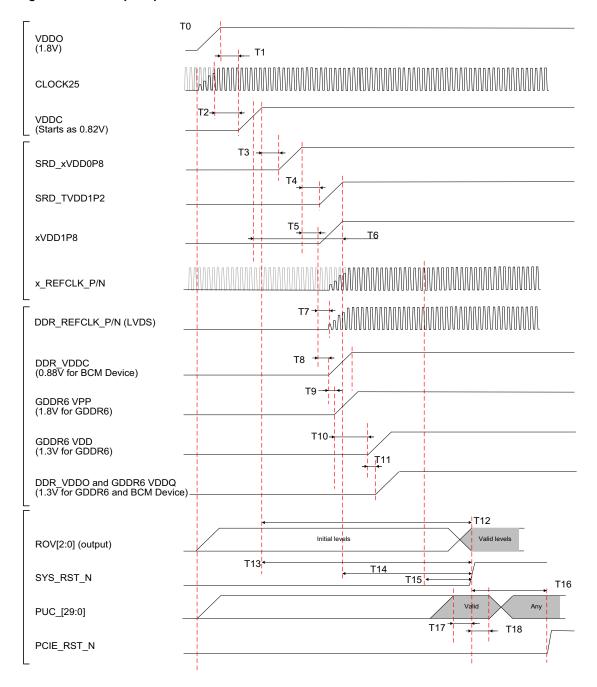

|      | 5.5.1 Power-Up Sequence                                   | 64 |

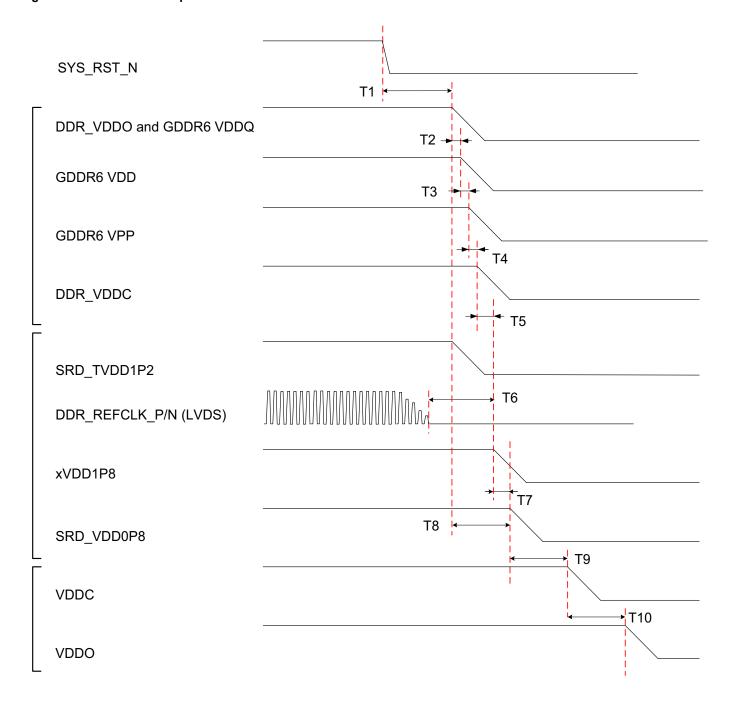

|      | 5.5.2 Power-Down Sequence                                 | 67 |

|      | 5.5.3 Fail-Safe Considerations                            | 69 |

|      | 5.5.4 Warm Reset                                          | 69 |

| 5.6  | Power-Up Configuration Word                               | 70 |

| 5.7  | DC Electrical Specifications                              | 71 |

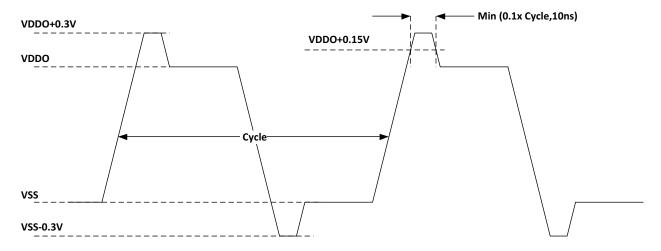

|      | 5.7.1 1.8V Digital I/Os                                   | 71 |

|      | 5.7.2 BSC/I <sup>2</sup> C                                | 71 |

| 5.8  | AC Electrical Specifications                              | 72 |

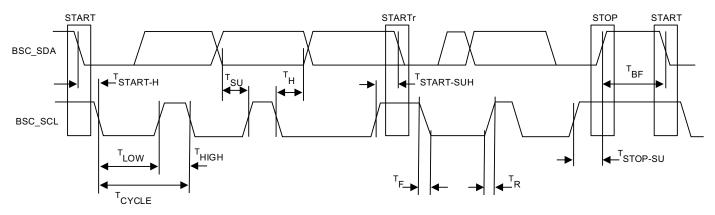

|      | 5.8.1 BSC/I <sup>2</sup> C Interface Timing               | 72 |

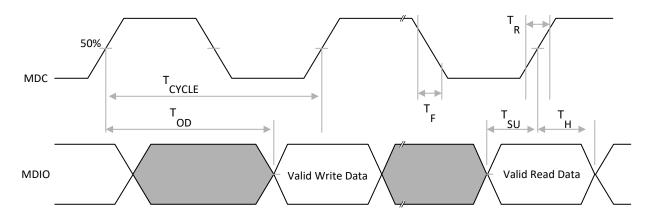

|      | 5.8.2 Management Interface Timing                         | 73 |

|      | 5.8.2.1 MDIO AC Characteristics                           | 73 |

|      | 5.8.3 SyncE Recovered Clocks                              | 73 |

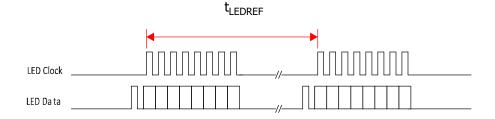

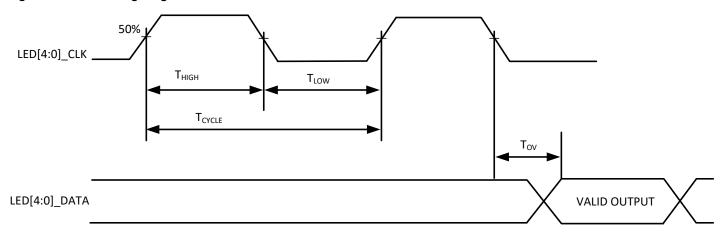

|      | 5.8.4 LED Timing                                          | 74 |

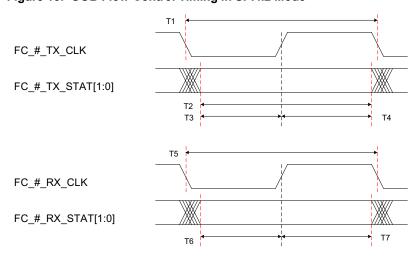

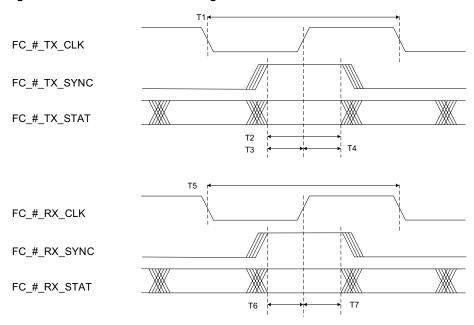

|      | 5.8.5 Out-of-Band Flow Control Timing                     | 75 |

|      | 5.8.5.1 SPI4.2 Flow-Control Mode                          | 75 |

|      | 5.8.5.2 Interlaken Flow-Control Mode                      | 76 |

|      | 5.8.6 BroadSync and Time Sync Timing                      | 77 |

|      | 5.8.7 PCle Interface                                      | 78 |

|      | 5.8.7.1 PCle Receiver                                     | 78 |

|      | 5.8.7.2 PCle Transmitter                                  | 78 |

|      | 5.8.8 QSPI Flash Interface                          | 79 |

|------|-----------------------------------------------------|----|

| 5.9  | Reference Clocks                                    | 80 |

|      | 5.9.1 CLOCK25 Reference Clock                       | 80 |

|      | 5.9.2 Core and Microcontroller PLL Reference Clocks | 80 |

|      | 5.9.3 PCIe PLL Reference Clock                      | 81 |

|      | 5.9.4 SerDes Reference Clock                        | 81 |

|      | 5.9.5 TS_PLL Reference Clock                        | 82 |

|      | 5.9.6 DRAM PLL Reference Clock                      | 82 |

|      | 5.9.7 FlexE PLL Reference Clock                     |    |

|      | 5.9.8 FlexE 8K Clock                                | 83 |

| 5.10 | 0 Blackhawk SerDes Operating Conditions             | 84 |

|      | 5.10.1 Blackhawk SerDes Features                    | 84 |

|      | 5.10.1.1 General Features                           | 84 |

|      | 5.10.1.2 Debug Features                             | 84 |

|      | 5.10.2 Blackhawk SerDes Receiver                    | 85 |

|      | 5.10.3 Blackhawk SerDes Transmitter                 | 85 |

| 5.11 | 1 Falcon16 SerDes Operating Conditions              | 86 |

|      | 5.11.1 Falcon16 SerDes Features                     | 86 |

|      | 5.11.1.1 General Features                           | 86 |

|      | 5.11.1.2 Debug Features                             | 86 |

|      | 5.11.2 Falcon16 SerDes Supported Rates              | 87 |

|      | 5.11.3 Falcon16 SerDes Receiver                     | 87 |

|      | 5.11.4 Falcon16 SerDes Transmitter                  | 87 |

| Chap | oter 6: Thermal Specifications                      | 88 |

| 6.1  | Absolute and Operational Thermal Specifications     | 88 |

| 6.2  | Package Block Thermal Model Specifications          | 89 |

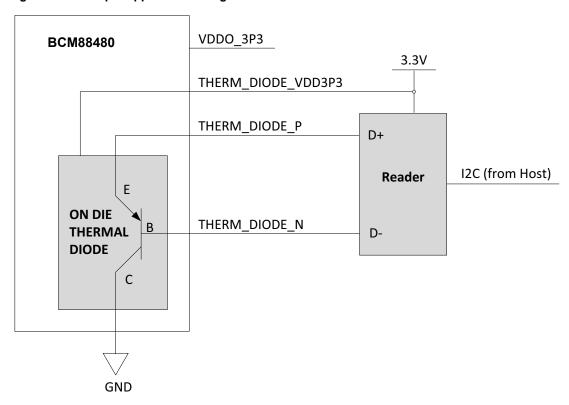

| 6.3  | Temperature Monitoring                              | 89 |

|      | 6.3.1 VTMON                                         | 89 |

|      | 6.3.2 Thermal Diode                                 | 89 |

| 6.4  | Reflow Temperature                                  | 91 |

| 6.5  | Heat Sink Considerations                            | 91 |

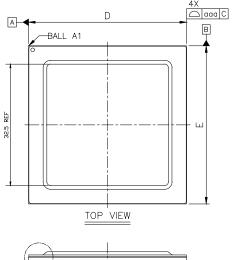

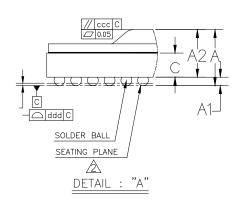

| Chap | oter 7: Packaging                                   | 92 |

| _    | ted Documents                                       | 93 |

# **Chapter 1: Introduction**

### 1.1 Features

The Broadcom BCM88480 is an optimized switching solution for 5G mobile backhaul, cell-site routing transport, and data center applications, enabling switching platforms with a mix of Ethernet, OTN, and FlexE ports.

The following features are available with the BCM88480:

- High performance

- 800 Gb/s full-duplex, integrated traffic manager, packet processor, and Layer 1 switching device.

- 600 Mp/s processing rate (450 Mp/s at 450-MHz core)

- Flexible network interface

- 16 SerDes with rates up to 53.125 Gb/s, supporting the following port configurations:

- 16 × 10GbE/25GbE/50GbE over one lane

- 8 × 40GbE/50GbE/100GbE over two lanes

- 4 × 40GbE/100GbE/200GbE over four lanes

- 2 × 400GbE over eight lanes (400GbE is not available when the core clock is 450 MHz)

- 36 SerDes with rates up to 25.78125G, supporting the following port configurations:

- 36 × 1GbE/10GbE/25GbE over one lane

- 18 × 40GbE/50GbE over two lanes

- 9 × 40GbE/100GbE over four lanes

- Up to four Interlaken interfaces

- Flex Ethernet (FlexE)

- Full support of the Optical Internetworking Forum (OIF) FlexE standard versions 1.x and 2.x

- Up to 400 Gb/s of total FlexE traffic

- Bonding of up to eight PHYs in a group

- Up to 80 FlexE clients, with client bandwidth granularity of 5 Gb/s

- Sub-rating of Ethernet PHYs

- Accurate time synchronization

- Switching at Layer 2 through Layer 4 of FlexE and Ethernet traffic

- Packet lengths supported in the range 64B to 10240B

- Traffic Manager

- 32K programmable wire-rate queues

- Deep packet buffering using two external GDDR6 DRAM devices.

- Congestion management

- Hierarchical WRED and tail-drop policies

- Congestion notification CNM generation and CNM reception (proxy)

- Flow control generation Fully programmable, in-band and out-of-band

- Flow control reception-any level Interface, port, class, flow, traffic type (in-band and out-of-band)

- Priority flow control (PFC) Eight levels

- Congestion tracking statistics

- Three ingress meter operations per packet

- Two egress meter operations per packet

- Hierarchical scheduling and shaping

- · Fully programmable to any depth

- Support for priority propagation

- MEF, Broadband Forum TR-059-compliant scheduling and shaping

- Packet processor

- Bridging, routing, MPLS, VPLS, L2VPNs, L3VPNs, and OAM

- MPLS and IPv6 segment routing

- Data center tunneling encapsulations including VXLAN, NV-GRE, and GENEVE

- Built-in support for data center, carrier and metro Ethernet, and transport applications

- Large modular on-chip databases, application-oriented with off-chip expandability

- OAM accelerator engine

- PEM (flexible pipe)

- Counters, meters, and statistics

- On-chip counter pool up to 128K counters

- On-chip meter pool up to 64K meters

- Statistics interface for expandable, off-chip statistics gathering:

- The SerDes used for the statistics interface is shared with network interface (NIF) SerDes

- Efficient packet-based protocol based on Ethernet simplifies connectivity to KBP BCM16K, TAP BCM5235, or FPGAs

- Seamless connection to KBP BCM16K and TAP BCM5235 devices

- Multicast Pointer-based ingress and egress multicast replication

- IEEE 1588 support with improved time-stamping accuracy of nanosecond scale

- In-band management

- PCIe × two-lane Gen3 host interface with DMA

- Hardware linkscan engine

- LED processor

# 1.2 Device Overview

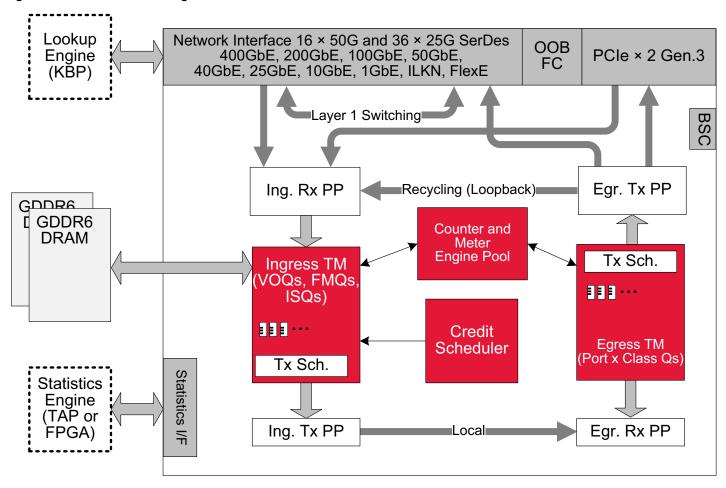

The following figure is a high-level functional block diagram of the BCM88480.

Figure 2: BCM88480 Block Diagram

As shown in Figure 2, the BCM88480 includes the following functional blocks.

#### **Traffic Manager**

- Ingress traffic manager (TM):

- Manages a pool of queues in on-chip SRAM and in off-chip DRAM

- Replicates packets for multicast, snooping, and mirroring

- Ingress and egress end-to-end credit scheduler Schedules packets out of the ingress TM

- Egress traffic manager:

- Manages a pool of egress queues in on-chip memory

- Schedules traffic toward packet interfaces Network, PCIe, internal hosts, and recycling (loopback)

- Replicates multicast packets

- Counter and meter engine pool:

- Features a general-purpose pool of counters and meters

- Handles ingress and egress counting and metering

- Includes configurable counting modes and criteria

- Applied according to the packet processor command

#### **Packet Processing**

- Ingress receive packet processor:

- Manages the main packet processing stage

- Identifies incoming interface link layer, tunnel, PWE, and AC

- Determines where to forward the packet based on packet forwarding header (L2, L3, MPLS, and so on)

- Appends the packet processor (PP) header

- Uses optionally expandable databases using an external lookup (ELK) interface

- Ingress transmit packet processor:

- Edits the packet (or packet copy) before transmitting to egress PP

- Egress receive packet processor:

- Filters packets according to various criteria

- Egress transmit packet processor:

- Edits packets according to PP header (from ingress)

#### Flex Ethernet (FlexE)

- Full support of the OIF FlexE standard versions 1.1 and 2.0

- Up to 400 Gb/s of total FlexE traffic

- Up to eight FlexE groups

- Bonding of up to eight PHYs in a group

- Up to 80 FlexE clients, with client bandwidth granularity of 5 Gb/s

- Bonding of Ethernet PHYs

- Sub-rating of Ethernet PHYs

- Accurate time synchronization

- Layer 1 switching between FlexE clients to FlexE clients

- Layer 1 switching between FlexE clients to Ethernet ports

- Layer 1 switching between clients on different BCM88480 devices (using DNX FAP and Fabric)

- Switching at Layer 2 through Layer 4 of FlexE and Ethernet traffic

#### **Interfaces**

- Network interface:

- 16 SerDes up to 53.125 Gb/s (PAM4)

- 36 SerDes up to 25.78125 Gb/s

- Port types supported include 1GbE, 10GbE, 25GbE, 40GbE, 50GbE, 100GbE, 200GbE, and 400GbE

- Multiple Interlaken (ILKN) interfaces

- Statistics interface:

- Sharing network interface SerDes

- Use Ethernet ports, up to 100GbE per statistics interface

- Generate statistics records over packets

- External lookup interface (ELK):

- Running over Interlaken interface, using NIF SerDes

- Out-of-band flow control (OOBFC):

- Transmit and receive flow control

- SPI 4.2 or ILKN protocol

- PCle x2 lane Gen3 host interface:

- Configuration and status register access

- Packet transfer to and from host memory by using DMA

- Broadcom Serial Control (BSC, which is NXP I<sup>2</sup>C-compatible) two-line interface:

- Basic device debug and register access (PCIe debug)

- PCIe QSPI flash programming

- Loading code used for heating when an industrial device is powered-up at a low ambient temperature (not supported by the current SDK)

# **Chapter 2: System Configurations**

# 2.1 Stand-Alone or Centralized Switch

The BCM88480 may be used as a stand-alone or centralized switch device with ingress and egress intelligent TM. The integrated TM enables intelligent oversubscription with granular, per-flow (or per-customer-and-traffic-class) scheduling and shaping in the upstream direction, downstream direction, or both.

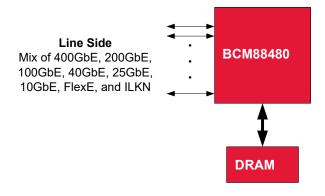

Figure 3: BCM88480 Switch with Integrated Traffic Manager

As shown in the preceding figure, the BCM88480 offers a flexible set of user interfaces, supporting a mix of 10GbE, 25GbE, 40GbE, 50GbE, 100GbE, 200GbE, and 400GbE Ethernet ports, FlexE, and ILKN interfaces.

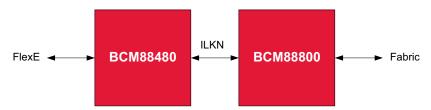

# 2.2 FlexE Adapter

The BCM88480 can be used as a FlexE adapter when connected to the BCM88800 in a line card. This capability enables a scalable system based on the StrataDNX fabric technology. A typical line-card configuration uses one or two BCM88480 devices connected to a single BCM88800 device to create a 400-Gb/s line card (using one BCM88480 device) or an 800-Gb/s line card (using two BCM88480 devices).

When used as an adapter, the BCM88480 operates as a PHY or a media converter device. All packet processing, traffic management, and packet buffering is performed by the BCM88800.

In this mode, the BCM88480 cannot operate Ethernet ports in parallel to the FlexE ports.

Figure 4: BCM88480 as FlexE Adapter

As shown in the figure, the BCM88480 operates as a FlexE adapter for rates up to 400 Gb/s. The connectivity between the BCM88480 and the BCM88800 is through one or two Interlaken interfaces.

In this application, no packet buffering is performed by the BCM88480, and there is no need to attach external DRAM to it.

# **Chapter 3: System Interfaces**

# 3.1 Network Interface

The BCM88480 network interface (NIF) includes two PM50s, nine PM25s, and two Interlaken (ILKN) cores.

#### **Ethernet Port Macros (PMs)**

#### PM50:

- Two Ethernet port macros supporting SerDes rates up to 53.125G

- Each PM50 includes an octal SerDes (Blackhawk) supporting up to 53.125G

- Each PM50 supports the following Ethernet configurations:

- 1 × 400GbE port over eight lanes (PAM4)

- 2 × 200GbE ports over four lanes (PAM4)

- 4 × 100GbE ports over two lanes (PAM4)

- 2 × 100GbE ports over four lanes

- 8 × 50GbE ports over one lane (PAM4)

- 4 × 50GbE ports over two lanes

- 4 × 40GbE ports over two lanes

- 2 × 40GbE ports over four lanes

- 8 × 25GbE ports over one lane

- 8 × 12GbE ports over one lane

- 8 × 10GbE ports over one lane

#### PM25:

- Nine Ethernet port macros supporting SerDes rates up to 25.78125G

- Each PM25 includes a quad SerDes (Falcon16) supporting up to 25.78125G

- Each PM25 supports the following Ethernet configurations:

- 1 × 100GbE port over four lanes

- 2 × 50GbE ports over two lanes

- 2 × 40GbE ports over two lanes

- 1 × 40GbE port over four lanes

- 4 × 25GbE ports over one lane

- 4 × 12GbE ports over one lane

- 4 × 10GbE ports over one lane

- 4 × 1GbE ports over one lane

#### FlexE Core

The BCM88480 supports a 400G FlexE core with the following capabilities:

- Up to 400G FlexE traffic.

- Up to eight FlexE groups.

- Up to 80 clients. Client bandwidth can be from 5G to 400G.

#### Interlaken Cores

The BCM88480 contains two Interlaken cores:

- Each Interlaken core can be configured to two interfaces that can support up to 12 lanes at 25.78125 Gb/s.

- Interface 2 (when it is a single interface in the core) can support up to 24 lanes at 25.78125 Gb/s.

ILKN FEC is not supported in the BCM88480.

#### **SerDes Interface Mapping**

The following table describes the mapping of PMs and Interlaken cores to SerDes and provides the interface naming conventions.

**NOTE:** The information in the table applies to the device family in general. Each part number within the device family might support a different subset of options listed in the table.

Table 1: BCM88480 NIF SerDes Interface Mapping

| PM      | SRD Number | PAM4 | FlexE | STAT | ILKN Core      | ILKN Interface       | ELK |

|---------|------------|------|-------|------|----------------|----------------------|-----|

| PM50_00 | 000 to 007 | +    | +     | _    | 0 <sup>a</sup> | 0 and 1 <sup>b</sup> | +   |

| PM50_01 | 008 to 015 | +    | +     | _    | 0              | 0 and 1              | +   |

| PM25_02 | 016 to 019 | _    | _     | _    | 0              | 0 and 1              | +   |

| PM25_03 | 020 to 023 | _    | _     | _    | 0              | 0 and 1              | +   |

| PM25_04 | 024 to 027 | _    | _     | _    | 0              | 0 and 1              | +   |

| PM25_05 | 028 to 031 | _    | _     | +    | 1              | 2 and 3 <sup>c</sup> | _   |

| PM25_06 | 032 to 035 | _    | _     | +    | 1              | 2 and 3              | _   |

| PM25_07 | 036 to 039 | _    | _     | +    | 1              | 2 and 3              | _   |

| PM25_08 | 040 to 043 | _    | _     | _    | 1              | 2 and 3              | _   |

| PM25_09 | 044 to 047 | _    | _     | _    | 1              | 2 and 3              | _   |

| PM25_10 | 048 to 051 | _    | _     | _    | 1              | 2 and 3              | _   |

a. PM50\_00 can support ILKN only over SerDes 4 to 7.

Only ILKN interfaces 2 and 3 can be used for FlexE L1 traffic.

**NOTE:** For devices using a 600-MHz core clock, limit the total bandwidth of all provisioned ports (NIF ports and internal ports) to 1200 Gb/s.

For devices using a 450-MHz core clock, limit the total bandwidth of all provisioned ports (NIF ports and internal ports) to 900 Gb/s.

b. An ILKN interface cannot use SerDes from different types of PMs.

ILKN interface 0 can use up to 12 lanes from either PM50 (Blackhawk) or PM25 (Falcon), but not from both at the same time.

ILKN interface 1 can use up to 12 lanes from either PM50 (Blackhawk) or PM25 (Falcon), but not from both at the same time.

ILKN interface 2 (if it is a single interface in core 1) can use up to 24 lanes.

ILKN Interface 3 can support up to 12 lanes.

### 3.1.1 Ethernet Ports

Ethernet ports are implemented by the Ethernet port macro (PM). The PMs include the MAC and PCS layers of Ethernet ports. The BCM88480 includes two types of port macros. PM50 is based on an octal SerDes block (Blackhawk) that supports SerDes rates up to 53.125 Gb/s. PM25 is based on a quad SerDes block (Falcon16) that supports SerDes rates of up to 25.78125 Gb/s.

The following table depicts the Ethernet port modes supported by PM50 and PM25. Rates above 25.78125 Gb/s are supported only by PM50.

#### NOTE:

- RS272 FEC is a Broadcom-proprietary protocol to achieve lower latency.

- For 100G and 50G ports using RS-272 FEC mode, the FEC engine serves four SerDes lanes. If using RS-272, no other FEC mode can be used in the same FEC engine.

- BASE-R FEC indicates IEEE 802.3, Clause 74-compliant FEC.

**Table 2: Supported Port Modes**

| Port<br>Speed | No. of<br>Lanes | PM Type   | Port Mode     | SerDes<br>Rate (Gb/s) | VCO Rate (GHz) | SerDes<br>Mode | FEC            | Related Standard                                                          |

|---------------|-----------------|-----------|---------------|-----------------------|----------------|----------------|----------------|---------------------------------------------------------------------------|

| 400GbE        | 8               | PM50 only | 400GAUI-8 C2C | 53.125                | 26.5625        | PAM4           | RS-544, RS-272 | IEEE 802.3 Annex 120D                                                     |

|               |                 |           | 400GAUI-8 C2M | 53.125                | 26.5625        | PAM4           | RS-544, RS-272 | IEEE 802.3 Annex 120E                                                     |

|               |                 |           | 400GBASE-KR8  | 53.125                | 26.5625        | PAM4           | RS-544, RS-272 | This is 400GAUI-8 with KR interface as defined in IEEE 802.3cd Clause 137 |

|               |                 |           | 400GBASE-CR8  | 53.125                | 26.5625        | PAM4           | RS-544, RS-272 | This is 400GAUI-8 with CR interface as defined in IEEE 802.3cd Clause 136 |

| 200GbE        | 4               | PM50 only | 200GAUI-4 C2C | 53.125                | 26.5625        | PAM4           | RS-544, RS-272 | IEEE 802.3 Annex 120D                                                     |

|               |                 |           | 200GAUI-4 C2M | 53.125                | 26.5625        | PAM4           | RS-544, RS-272 | IEEE 802.3 Annex 120E                                                     |

|               |                 |           | 200GBASE-KR4  | 53.125                | 26.5625        | PAM4           | RS-544, RS-272 | IEEE 802.3cd Clause 137                                                   |

|               |                 |           | 200GBASE-CR4  | 53.125                | 26.5625        | PAM4           | RS-544, RS-272 | IEEE 802.3cd Clause 136                                                   |

**Table 2: Supported Port Modes (Continued)**

| Port<br>Speed | No. of Lanes | PM Type       | Port Mode     | SerDes<br>Rate (Gb/s) | VCO Rate (GHz) | SerDes<br>Mode | FEC            | Related Standard                                                                                          |

|---------------|--------------|---------------|---------------|-----------------------|----------------|----------------|----------------|-----------------------------------------------------------------------------------------------------------|

| 100GbE        | 2            | PM50 only     | 100GAUI-2 C2C | 53.125                | 26.5625        | PAM4           | RS-544, RS-272 | IEEE 802.3cd Annex 135F                                                                                   |

|               |              |               | 100GAUI-2 C2M | 53.125                | 26.5625        | PAM4           | RS-544, RS-272 | IEEE 802.3cd Annex 135G                                                                                   |

|               |              |               | 100GBASE-KR2  | 53.125                | 26.5625        | PAM4           | RS-544, RS-272 | IEEE 802.3cd Clause 137                                                                                   |

|               |              |               | 100GBASE-CR2  | 53.125                | 26.5625        | PAM4           | RS-544, RS-272 | IEEE 802.3cd Clause 136                                                                                   |

|               |              |               | CAUI-2 C2C    | 51.5625               | 25.78125       | PAM4           | RS-528         | IEEE 802.3 (CAUI-4) port, bit-muxed to two lanes with C2C interface as defined in IEEE 802.3cd Annex 135F |

|               |              |               | CAUI-2 C2M    | 51.5625               | 25.78125       | PAM4           | RS-528         | IEEE 802.3 (CAUI-4) port, bit-muxed to two lanes with C2M interface as defined in IEEE 802.3cd Annex 135G |

| 100GbE        | 4            | PM50 and PM25 | CAUI-4 C2C    | 25.78125              | 25.78125       | NRZ            | RS-528, no FEC | IEEE 802.3 Annex 83D                                                                                      |

|               |              |               | CAUI-4 C2M    | 25.78125              | 25.78125       | NRZ            | RS-528, no FEC | IEEE 802.3 Annex 83E                                                                                      |

|               |              |               | 100GBASE-KR4  | 25.78125              | 25.78125       | NRZ            | RS-528, no FEC | IEEE 802.3 Clause 93                                                                                      |

|               |              |               | 100GBASE-CR4  | 25.78125              | 25.78125       | NRZ            | RS-528, no FEC | IEEE 802.3 Clause 92                                                                                      |

|               |              | PM50 only     | 100GAUI-4 C2C | 26.5625               | 26.5625        | NRZ            | RS-544         | IEEE 802.3cd Annex 135D                                                                                   |

|               |              |               | 100GAUI-4 C2M | 26.5625               | 26.5625        | NRZ            | RS-544         | IEEE 802.3cd Annex 135E                                                                                   |

| 50GbE         | 1            | PM50 only     | 50GAUI-1 C2C  | 53.125                | 26.5625        | PAM4           | RS-544, RS-272 | IEEE 802.3cd Annex 135F                                                                                   |

|               |              |               | 50GAUI-1 C2M  | 53.125                | 26.5625        | PAM4           | RS-544, RS-272 | IEEE 802.3cd Annex 135G                                                                                   |

|               |              |               | 50GBASE-KR    | 53.125                | 26.5625        | PAM4           | RS-544, RS-272 | IEEE 802.3cd Clause 137                                                                                   |

|               |              |               | 50GBASE-CR    | 53.125                | 26.5625        | PAM4           | RS-544, RS-272 | IEEE 802.3cd Clause 136                                                                                   |

**Table 2: Supported Port Modes (Continued)**

| Port<br>Speed | No. of Lanes | PM Type       | Port Mode             | SerDes<br>Rate (Gb/s) | VCO Rate (GHz) | SerDes<br>Mode | FEC            | Related Standard                                                                                                 |                                                                                                                 |

|---------------|--------------|---------------|-----------------------|-----------------------|----------------|----------------|----------------|------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| 50GbE         | 2            | PM50 and PM25 | Consortium 50G C2C    | , ,                   | 25.78125       | NRZ            | RS-528, no FEC | Consortium 50GE with C2C interface as defined in IEEE 802.3 Annex 83D                                            |                                                                                                                 |

|               |              |               | Consortium 50G<br>C2M | 25.78125              | 25.78125       | NRZ            | RS-528, no FEC | Consortium 50GE with C2M interface as defined in IEEE 802.3 Annex 83E                                            |                                                                                                                 |

|               |              |               | LAUI-2 C2C            | 25.78125              | 25.78125       | NRZ            | RS-528, no FEC | IEEE 802.3cd Annex 135B                                                                                          |                                                                                                                 |

|               |              |               | LAUI-2 C2M            | 25.78125              | 25.78125       | NRZ            | RS-528, no FEC | IEEE 802.3cd Annex 135C                                                                                          |                                                                                                                 |

|               |              |               | Consortium 50G KR2    | 25.78125              | 25.78125       | NRZ            | RS-528, no FEC | Consortium 50GbE with KR interface as defined in IEEE 802.3 Clause 93                                            |                                                                                                                 |

|               |              |               | Consortium 50G CR2    | 25.78125              | 25.78125       | NRZ            | RS-528, no FEC | Consortium 50GbE with CR interface as defined in IEEE 802.3 Clause 92                                            |                                                                                                                 |

|               |              | PM50 only     | 50GAUI-2 C2C          | 26.5625               | 26.5625        | NRZ            | RS-544         | IEEE 802.3cd Annex 135D                                                                                          |                                                                                                                 |

|               |              |               | 50GAUI-2 C2M          | 26.5625               | 26.5625        | NRZ            | RS-544         | IEEE 802.3cd Annex 135E                                                                                          |                                                                                                                 |

| 40GbE         | 2            | PM50 and PM25 | XLAUI-2 KR            | 20.625                | 20.625         | NRZ            | No FEC         | XLAUI-4, bit-muxed to two lanes, with KR interface as defined in 802.3 Clause 93 (masks scaled to 20.625G)       |                                                                                                                 |

|               |              |               |                       | XLAUI-2 CR            | 20.625         | 20.625         | NRZ            | No FEC                                                                                                           | XLAUI-4, bit-muxed to two lanes, with CR interface as defined in IEEE 802.3 Clause 92 (masks scaled to 20.625G) |

|               |              |               | XLAUI-2 C2C           | 20.625                | 20.625         | NRZ            | No FEC         | XLAUI-4, bit-muxed to two lanes, with C2C interface as defined in IEEE 802.3 Annex 83D (masks scaled to 20.625G) |                                                                                                                 |

|               |              |               | XLAUI-2 C2M           | 20.625                | 20.625         | NRZ            | No FEC         | XLAUI-4, bit-muxed to two lanes, with C2M interface as defined in IEEE 802.3 Annex 83E (masks scaled to 20.625G) |                                                                                                                 |

| 40GbE         | 4            | PM50 and PM25 | XLAUI                 | 10.3125               | 20.625         | NRZ            | BASE-R, no FEC | IEEE 802.3 Annex 83A                                                                                             |                                                                                                                 |

|               |              |               | 40GBASE-KR4           | 10.3125               | 20.625         | NRZ            | BASE-R, no FEC | IEEE 802.3 Clause 84                                                                                             |                                                                                                                 |

|               |              |               | 40GBASE-CR4           | 10.3125               | 20.625         | NRZ            | BASE-R, no FEC | IEEE 802.3 Clause 85                                                                                             |                                                                                                                 |

|               |              |               | XLPPI                 | 10.3125               | 20.625         | NRZ            | BASE-R, no FEC | IEEE 802.3 Annex 86A                                                                                             |                                                                                                                 |

**Table 2: Supported Port Modes (Continued)**

| Port<br>Speed | No. of<br>Lanes | РМ Туре       | Port Mode                        | SerDes<br>Rate (Gb/s) | VCO Rate (GHz)                 | SerDes<br>Mode | FEC                       | Related Standard                |

|---------------|-----------------|---------------|----------------------------------|-----------------------|--------------------------------|----------------|---------------------------|---------------------------------|

| 25GbE         | 1               | PM50 and PM25 | 25GAUI C2C                       | 25.78125              | 25.78125                       | NRZ            | RS-528, BASE-R, no<br>FEC | IEEE 802.3 Annex 109A           |

|               |                 |               | 25GAUI C2M                       | 25.78125              | 25.78125                       | NRZ            | RS-528, BASE-R, no<br>FEC | IEEE 802.3 Annex 109B           |

|               |                 |               | 25GBASE-KR/<br>25GBASE-KR-S      | 25.78125              | 25.78125                       | NRZ            | RS-528, BASE-R, no<br>FEC | IEEE 802.3 Clause 111           |

|               |                 |               | 25GBASE-CR/<br>25GBASE-CR-S      | 25.78125              | 25.78125                       | NRZ            | RS-528, BASE-R, no<br>FEC | IEEE 802.3 Clause 110           |

| 12GbE         | 1               | PM50 and PM25 | XFI (Scaled)                     | 12.5                  | 25                             | NRZ            | No FEC                    | XFI+ (FC-PI-3), scaled to 12.5G |

| 10GbE         | 1               | PM50 and PM25 | 10GBASE-KR                       | 10.3125               | PM50: 20.625<br>PM25: 25.78125 | NRZ            | BASE-R, no FEC            | IEEE 802.3 Clause 72            |

|               |                 |               | XFI                              | 10.3125               | PM50: 20.625<br>PM25: 25.78125 | NRZ            | BASE-R, no FEC            | XFI+ (FC-PI-3)                  |

|               |                 |               | SFI                              | 10.3125               | PM50: 20.625<br>PM25: 25.78125 | NRZ            | BASE-R, no FEC            | SFF-8431                        |

|               |                 |               | Direct Attached<br>Cable (DAC)   | 10.3125               | PM50: 20.625<br>PM25: 25.78125 | NRZ            | BASE-R, no FEC            | _                               |

| 1GbE          | 1               | PM25 only     | 1000BASE-X,<br>SGMII (1GbE only) | 1.25                  | 25.78125                       | NRZ            | No FEC                    | _                               |

#### 3.1.1.1 400GbE Port

The BCM88480 device supports standard 400GbE according to IEEE 802.3. This port type is supported on PM50 only (not supported on PM25).

The 400GbE port supports the following interfaces:

- 400GAUI-8 (chip-to-chip IEEE 802.3 Annex 120D and chip-to-module IEEE 802.3 Annex 120E)

- 400GBASE-KR8 (this is 400GAUI-8 with a KR interface as defined in IEEE 802.3cd Clause 137)

- 400GBASE-CR8 (this is 400GAUI-8 with a CR interface as defined in IEEE 802.3cd Clause 136)

When using the 400GbE port, Reed-Solomon FEC is supported. This FEC is compliant with IEEE 802.3 Clause 119, RS(544,514).

#### 3.1.1.2 200GbE Port

The BCM88480 device supports standard 200GbE according to IEEE 802.3 and IEEE 802.3cd. This port type is supported on PM50 only (not supported on PM25).

The 200GbE port supports the following interfaces:

- 200GAUI-4 (chip-to-chip IEEE 802.3 Annex 120D and chip-to-module IEEE 802.3 Annex 120E)

- 200GBASE-KR4 (IEEE 802.3cd Clause 137)

- 200GBASE-CR4 (IEEE 802.3cd Clause 136)

When using the 200GbE port, an optional Reed-Solomon FEC is supported. This FEC is compliant with IEEE 802.3 Clause 119, RS(544,514).

#### 3.1.1.3 100GbE Port

#### 3.1.1.3.1 100GbE over Two Lanes

The BCM88480 device supports standard 100GbE according to IEEE 802.3cd. This port type is supported on PM50 only (not supported on PM25).

The 100GbE port supports the following interfaces:

- 100GAUI-2 (chip-to-chip IEEE 802.3cd Annex 135F and chip-to-module IEEE 802.3cd Annex 135G)

- 100GBASE-KR2 (IEEE 802.3cd Clause 137)

- 100GBASE-CR2 (IEEE 802.3cd Clause 136)

- CAUI-2, which is the IEEE 802.3 (CAUI-4) port bit-muxed to two lanes (chip-to-chip and chip-to-module).

When using the 100GbE port, an optional Reed-Solomon FEC is supported. This FEC is compliant with IEEE 802.3 Clause 91, both RS(528,514) and RS(544,514).

#### 3.1.1.3.2 100GbE over Four Lanes

The BCM88480 device supports standard 100GbE according to IEEE 802.3. This port type is supported on both PM50 and PM25.

The 100GbE port supports the following interfaces:

- CAUI-4 (chip-to-chip IEEE 802.3 Annex 83D and chip-to-module IEEE 802.3 Annex 83E)

- 100GBASE-KR4 (IEEE 802.3 Clause 93)

- 100GBASE-CR4 (IEEE 802.3 Clause 92)

- 100GAUI-4 (chip-to-chip IEEE 802.3cd Annex 135D and chip-to-module IEEE 802.3cd Annex 135E)

When using the 100GbE port, an optional Reed-Solomon FEC is supported. This FEC is compliant with IEEE 802.3 Clause 91, both RS(528,514) and RS(544,514).

#### 3.1.1.4 50GbE Port

#### 3.1.1.4.1 50GbE over One Lane

The BCM88480 supports 50GbE according to IEEE 8023.cd. This port type is supported on PM50 only (not supported on PM25).

The 50GbE port supports the following interfaces:

- 50GAUI-1 (chip-to-chip IEEE 802.3cd Annex 135F and chip-to-module IEEE 802.3cd Annex 135G)

- 50GBASE-KR (IEEE 802.3cd Clause 137)

- 50GBASE-CR (IEEE 802.3cd Clause 136)

When using the 50GbE port, an optional Reed-Solomon FEC is supported. This FEC is compliant with IEEE 802.3 Clause 134, RS(544,514).

#### 3.1.1.4.2 50GbE over Two Lanes

The BCM88480 supports 50GbE according to IEEE 802.3cd and the 25G/50G Ethernet consortium. This port type is supported on both PM50 and PM25.

The 50GbE port supports the following interfaces:

- 50GbE over two lanes according to the 25G/50G Ethernet consortium

- LAUI-2 (chip-to-chip IEEE 802.3cd Annex 135B and chip-to-module IEEE 802.3cd Annex 135C)

- 50GBASE-KR2 (this is Ethernet consortium 50GbE with a KR interface as defined in IEEE 802.3 Clause 93)

- 50GBASE-CR2 (this is Ethernet consortium 50GbE with a CR interface as defined in IEEE 802.3 Clause 92)

- 50GAUI-2 (chip-to-chip IEEE 802.3cd Annex 135D and chip-to-module IEEE 802.3cd Annex 135E)

When using the 50GbE port, an optional Reed-Solomon FEC is supported. This FEC is compliant with IEEE 802.3 Clause 134, RS(544,514), or Clause 91, RS(528,514). PM25 supports only Clause 91, RS(528,514).

#### 3.1.1.5 40GbE Port

#### 3.1.1.5.1 40GbE over Two Lanes

The BCM88480 supports standard 40GbE according to IEEE 802.3. This port type is supported on both PM50 and PM25.

The 40GbE ports support the following interfaces:

- XLAUI-2 This is XLAUI-4, bit-muxed to two lanes, with a KR interface as defined in IEEE 802.3 Clause 93 (masks scaled to 20.625G).

- XLAUI-2 This is XLAUI-4, bit-muxed to two lanes, with a CR interface as defined in IEEE 802.3 Clause 92 (masks scaled to 20.625G).

- XLAUI-2 This is XLAUI-4, bit-muxed to two lanes, with a chip-to-chip interface as defined in IEEE 802.3 Annex 83D (masks scaled to 20.625G).

- XLAUI-2 This is XLAUI-4, bit-muxed to two lanes, with a chip-to-module interface as defined in IEEE 802.3 Annex 83E (masks scaled to 20.625G).

No FEC is supported for the 40GbE port over two lanes.

#### 3.1.1.5.2 40GbE over Four Lanes

The BCM88480 supports standard 40GbE according to IEEE 802.3. This port type is supported on both PM50 and PM25.

The 40GbE ports support the following interfaces:

- XLAUI (IEEE 802.3 Annex 83A)

- 40GBASE-KR4 (IEEE 802.3 Clause 84)

- 40GBASE-CR4 (IEEE 802.3 Clause 85)

- XLPPI (IEEE 802.3 Annex 86A)

When using the 40GbE port in four-lane mode, an optional FEC is supported. The FEC is compliant with IEEE 802.3 Clause 74.

#### 3.1.1.6 25GbE Port

The BCM88480 supports 25GbE according to IEEE 802.3, and the 25G/50G Ethernet consortium. This port type is supported on both PM50 and PM25.

The 25GbE ports support the following interfaces:

- 25GAUI (chip-to-chip IEEE 802.3 Annex 109A and chip-to-module IEEE 802.3 Annex 109B)

- 25GBASE-KR/25GBASE-KR-S (IEEE 802.3 Clause 111)

- 25GBASE-CR/25GBASE-CR-S (IEEE 802.3 Clause 110)

When using the 25GbE port, an optional FEC is supported. The FEC can be either IEEE 802.3 Clause 108, RS(528,514) or IEEE 802.3 Clause 74 FEC.

### 3.1.1.7 12GbE Port

The BCM88480 supports 12GbE. The 12GbE port is similar to the 10GbE port, with a SerDes rate of 12.5G (scaled up from 10.3125G). This port type is supported on both PM50 and PM25.

The 12GbE port supports XFI+ (FC-PI-3), and the SerDes rate is scaled up to 12.5G from 10.3125G.

The 12GbE port does not support FEC.

#### 3.1.1.8 10GbE Port

The BCM88480 supports 10GbE according to IEEE 802.3. This port type is supported on both PM50 and PM25.

The 10GbE ports support the following interfaces:

- XFI or SFI for direct connect to optical module<sup>1</sup>

- 10GBASE-KR (IEEE 802.3 Clause 72)

- Direct-attached cable (DAC)

When using the 10GbE port with the KR interface, an optional FEC is supported. The FEC is compliant with IEEE 802.3 Clause 74.

#### 3.1.1.9 1GbE Port

The BCM88480 supports 1GbE over an SGMII or a 1000BASE-X interface.

- The GbE port is supported over the PM25 port macro only.

- The GbE port supports 1GbE only (no support for 10-Mb/s and 100-Mb/s speeds).

- The GbE port does not support auto-negotiation.

- The GbE port does not support clock recovery for SyncE.

- Half-duplex mode is not supported.

- No support is available for a 2.5GbE port.

Supported: SR (limiting), LR (limiting), ER (limiting).

Not supported: ZR (limiting), ZR (linear), LRM (linear), DWDM (linear).

### 3.1.1.10 Mixed Port Types on PM50

Different port types can be supported on the same Blackhawk port macro (PM50). Mixing port types is allowed when all ports in the same PM50 are derived from one or two PLL rates. The following table defines the PLL (VCO) combinations and available ETH ports on each combination.

NOTE: For Ethernet ports, TVCO (PLL1) and OCVO (PLL0) do not have the same functionality. (See

Section 3.1.1.10.1, PM50 Mixed Port-Type Limitations.)

NOTE: When FlexE is used, PM50 TVCO must be configured to 26.5625G.

Table 3: PM50 PLL VCO Combinations and Supported Port Types

|                 |                      |       | TVCO     | 25.78125G | 25.78125G | 25.78125G | 26.5625G | 26.5625G | 26.5625G  |

|-----------------|----------------------|-------|----------|-----------|-----------|-----------|----------|----------|-----------|

|                 |                      |       | ovco     | 20.625G   | 25.000G   | 26.5625G  | 20.625G  | 25.000G  | 25.78125G |

| VCO Rate (Gb/s) | Port BW              | Lanes | SRD Rate |           |           |           |          |          |           |

| 26.5625         | 400GbE               | 8     | 53.1250  |           |           | +         | +        | +        | +         |

| 26.5625         | 200GbE               | 4     | 53.1250  |           |           | +         | +        | +        | +         |

| 26.5625         | 100GbE               | 2     | 53.1250  |           |           | +         | +        | +        | +         |

| 26.5625         | 100GbE               | 4     | 26.5625  |           |           | +         | +        | +        | +         |

| 26.5625         | 50GbE                | 1     | 53.1250  |           |           | +         | +        | +        | +         |

| 26.5625         | 50GbE                | 2     | 26.5625  |           |           | +         | +        | +        | +         |

| 25.78125        | 100GbE               | 2     | 51.5625  | +         | +         | +         |          |          | +         |

| 25.78125        | 100GbE               | 4     | 25.78125 | +         | +         | +         |          |          | +         |

| 25.78125        | 50GbE                | 1     | 51.5625  | +         | +         | +         |          |          | +         |

| 25.78125        | 50GbE                | 2     | 25.78125 | +         | +         | +         |          |          | +         |

| 25.78125        | 25GbE                | 1     | 25.78125 | +         | +         | +         |          |          | +         |

| 25.000          | 12.5GbE <sup>a</sup> | 1     | 12.5000  |           | +         |           |          | +        |           |

| 20.6250         | 40GbE                | 2     | 20.6250  | +         |           |           | +        |          |           |

| 20.6250         | 40GbE                | 4     | 10.3125  | +         |           |           | +        |          |           |

| 20.6250         | 10GbE                | 1     | 10.3125  | +         |           |           | +        |          |           |

a. 12.5GbE data bandwidth is 12.12G. This is a non-standard ETH rate.

## 3.1.1.10.1 PM50 Mixed Port-Type Limitations

The main limitations of the PM50 are as follows:

- Up to eight lanes can be supported.

- Up to two VCO rates can be supported. An ETH application on PM50 requires a TVCO rate of 25.78125G or 26.5625G. This requirement prevents using a combination of 20.625G and 25.0000G PLL rates if ETH is used.

- Any modification of TVCO causes ETH ports based on OVCO to be reset as well.

- When FlexE is used, TVCO is set to 26.5625G.

#### 3.1.1.10.2 Software Sequence and Rules for Port Allocation

This section describes the software sequence and rules for port allocation. The goal is to provide a better understanding of the device options. For more information and updates regarding PMx50 mixed ports, refer to the *BCM88690 Traffic Manager Programming Guide* (88690-PG2xx).

Ports can be allocated to the PM8x50 by a single port assignment or by a multi-port assignment using the following APIs:

- bcm port resource set()

- bcm port resource multi set()

Ports are allocated only if the new configuration meets the TVCO and OVCO combinations in Table 3 and the following software limitations are met.

For the initial allocation (there are no active ports on the PM), VCO rates are defined according to the following table.

**Table 4: Initialization Options Table**

| Requested PLL Rate                 | Port Requirement for PM50 Initialization | TVCO                   | ovco      |

|------------------------------------|------------------------------------------|------------------------|-----------|

| Initialization with One Rate       |                                          |                        |           |

| 20.625G                            | At least one ETH port                    | 25.78125G <sup>a</sup> | 20.625G   |

| 20.625G                            | ILKN only (no ETH)                       | Shut-down              | 20.625G   |

| 25.000G                            | At least one ETH port                    | 25.78125G <sup>a</sup> | 25.000G   |

| 25.000G                            | ILKN only (no ETH)                       | Shut-down              | 25.000G   |

| 25.78125G                          | No restrictions                          | 25.78125G              | Shut-down |

| 26.5625G                           | No restrictions                          | 26.5625G               | Shut-down |

| Initialization with Two Rates      | S                                        |                        |           |

| 25.000G + 20.625G <sup>b</sup>     | ILKN only (no ETH)                       | 20.625G                | 25.000G   |

| 25.78125G + 20.625G                | No restrictions                          | 25.78125G              | 20.625G   |

| 25.78125G + 25.000G                | No restrictions                          | 25.78125G              | 25.000G   |

| 26.5625G + 20.625G                 | No restrictions                          | 26.5625G               | 20.625G   |

| 26.5625G + 25.000G No restrictions |                                          | 26.5625G               | 25.000G   |

| 26.5625G + 25.78125G               | No restrictions                          | 26.5625G               | 25.78125G |

a. The default rate is 25.78125G for the dynamic addition of 25.78125G ports. A software flag can configure the TVCO to 26.5625G if that rate is expected.

For an allocation update (there are active ports on the PM), the following information applies:

- If all ports in the PM are included in the update command, the SW treats the update as if this is the initial allocation.

- If only some of the PM ports are included in the update command, the SW tries to perform the PLL update without impacting used resources.

- To update TVCO, all ETH ports using TVCO and OVCO, as well as all ILKN ports using TVCO, should be included in the update command. All of these ports will go through the port-down and port-up sequence. (Only ILKN ports using OVCO are not affected.)

- To update OVCO, all ETH ports using OVCO and all ILKN ports using OVCO should be included in the update command. All of these ports will go through the port-down and port-up sequence. (Ports using TVCO are not affected.)

b. This combination cannot work with ETH. It works only with ILKN.

### 3.1.1.10.3 PM50 Mixed Port Type Allocation Restrictions

The scenarios in this section show examples of configuration restrictions.

#### Scenario 1

If a PM is configured using a 40GbE port (four lanes, VCO = 20.6250G) and a 50GbE port (two lanes, VCO = 25.78125G), a dynamic configuration adding a 100GbE port (four lanes, VCO = 25.78125G) results in an error indication because more than eight lanes are required.

#### Scenario 2

If a PM is configured using a 40GbE port (four lanes, VCO = 20.6250G) and a 50GbE port (two lanes, VCO = 26.5625G), a dynamic configuration that adds a 50GbE port (two lanes, VCO = 25.78125G) results in an error indication because three VCO rates are required.

#### Scenario 3

Static configuration of a 1  $\times$  200GbE port (four lanes, VCO = 26.5625G), and 4  $\times$  10GbE ports (four lanes, VCO = 20.6250G) results in {PLL1 = 26.5625G, PLL0 = 20.6250G}.

A dynamic configuration that replaces the 200GbE port with a 100GbE port (four lanes, VCO = 25.78125G) results in an error indication because PLL1 should be updated, causing a port-down event on the 10GbE ports as well.

If it is acceptable to allow the 10GbE ports to go down and back up, they should be added to the allocation update (by using bcm port resource multi set).

# 3.1.1.11 Mixed Port Types on PM25

The 25GbE (25.78125G), 10GbE (10.3125G), and 1GbE (1.25G) port types can coexist simultaneously on the same PM25. Any combination of other rates is not allowed.

For example, when using 12GbE (12.5G), other rates can not be used on the same PM25.

**NOTE:** If PM25 is used for ETH, it cannot be used for ILKN.

#### 3.1.2 FlexE

The BCM88480 includes a FlexE core with the following features:

- Full support of the OIF FlexE standard versions 1.1 and 2.0.

- Up to 400 Gb/s of total FlexE traffic.

- Up to eight FlexE groups.

- 50G, 100G, 200G, and 400G PHY rates. 53.125G, 26.5625G, and 25.78125G SerDes rates.

- Bonding of up to eight PHYs in a group.

- Up to 80 FlexE clients, with client bandwidth granularity of 5 Gb/s.

- Dynamic configuration of adding and removing FlexE groups and clients.

- Insertion and extraction of FlexE overhead.

- IEEE1588 over FlexE overhead.

- OAM insertion, extraction, and monitoring.

- 1+1 and 1:1 protection.

- Bonding of Ethernet PHYs.

- Sub-rating of Ethernet PHYs.

- Accurate time synchronization.

- Layer 1 switching between FlexE clients to FlexE clients.

- Layer 1 switching between FlexE clients to Ethernet ports.

- Layer 1 switching between clients on different BCM88480 devices (using a DNX FAP and fabric).

- Switching at Layer 2 through Layer 4 of FlexE and Ethernet traffic.

The BCM88480 FlexE core shares SerDes with PM50-0 and PM50-1. Depending on the device part-number, up to eight SerDes from either PM50-0 or PM50-1 can be used for FlexE 50G PAM4. Alternatively, up to 16 SerDes can be used for FlexE in NRZ mode.

FlexE can be enabled on BCM88480 devices that are running at 600 MHz only. A BCM88480 device running at 450 MHz cannot support FlexE.

For more information about BCM88480 support for FlexE, refer to the application note, FlexE Interface (88480-AN2xx).

NOTE: When FlexE is used, the TVCO of the PM50 that is used must be configured to 26.5625G.

#### 3.1.3 Interlaken

The BCM88480 has two Interlaken cores.

The BCM88480 Interlaken cores support SerDes rates of up to 25.78125G. For the defined ILKN rates, see Section 3.1.3.1, Interlaken SerDes Supported Rates and Electrical Standards.

ILKN core 0 can support two interfaces (ILKN\_0 and ILKN\_1), and each interface can be up to 12 lanes. ILKN core 0 shares SerDes with PM50-0 (lanes 4 to 7), PM50-1, PM25-2, PM25-3, and PM25-4.

ILKN core 1 can be configured to operate as either a single interface (ILKN\_2, up to 24 lanes) or as two interfaces (ILKN2 and ILKN 3, each up to 12 lanes). ILKN core 1 shares SerDes with PM25-25 to PM25-10.

When FlexE is used, ILKN\_0 and ILKN\_1 cannot be used for data (ILKN\_0 can be used for ELK).

For information about PM assignment to ILKN cores, see Table 1. When making assignments, use the following guidelines:

- If the RX (or TX) of a specific physical SerDes is used for ILKN, the TX (or RX) of the same SerDes should go to the same ILKN interface.

- For a logical ILKN lane, RX SerDes and TX SerDes should be on the same PM.

### 3.1.3.1 Interlaken SerDes Supported Rates and Electrical Standards

The ILKN interface is targeted to comply with the electrical specifications of the standards as listed in the following table.

Table 5: ILKN Supported Rates and Electrical Specifications Standards

| SerDes Rate (Gb/s) | SerDes Mode | Standard Electrical Specifications              |

|--------------------|-------------|-------------------------------------------------|

| 25.78125           | NRZ         | 25GBASE-KR-S IEEE 802.3 Clause 111              |

|                    |             | CAUI-4 C2C: IEEE 802.3 Annex 83D                |

|                    |             | CAUI-4 C2M: IEEE 802.3 Annex 83E                |

| 25.0               | NRZ         | 25GBASE-KR-S IEEE 802.3 Clause 111 <sup>a</sup> |

|                    |             | CAUI-4 C2C: IEEE 802.3 Annex 83D <sup>a</sup>   |

| 12.5               | NRZ         | 10G XFI: XFI+ (FC-PI-3) <sup>a</sup>            |

| 10.3125            | NRZ         | 10GBASE-KR IEEE 802.3 Clause 72                 |

|                    |             | 10G XFI: XFI+ (FC-PI-3)                         |

a. Scaled to the appropriate rate.

#### 3.1.3.2 Interlaken Receive Burst Rules

Packets are transmitted across the Interlaken interface in bursts. The BCM88480 requires that burst sizes and burst intervals (Interlaken BurstShort) conform to certain rules.

The BCM88480 Interlaken receive supports both burst interleaving and full packet mode. If the peer device is configured to burst interleaving, assign a separate ingress reassembly context for each active channel.

Receive (into the BCM88480) burst interleaving rules are as follows:

- Supported BurstMax size is 256B.

- Start-of-packet (SOP) bursts should be 192B or larger.

- Bursts that are not end-of-packet (EOP) bursts may be either 128B, 192B, or 256B.

- EOP bursts may be any size (up to the configured BurstMax).

- BurstShort (the minimum interval between burst control words) should be at least 64B for a 600 MHz-core clock or 96B for a 450-MHz core clock.

#### 3.1.3.3 Interlaken Transmit Burst Rules

When the StrataDNX TM is operational (stand-alone or central switch mode), the BCM88480 ILKN TX supports only full-packet mode (burst-interleaving occurs only when TDM packets preempt data packets).

When operating as a FlexE adapter, the BCM88480 ILKN TX works in burst-interleaving mode.

When transmitting across an Interlaken interface, the BCM88480 supports configurations consistent with the following:

- BurstShort (minimum interval between burst control words):

- When using a 600-MHz core clock, configuration is from 64B to 256B in increments of 32B.

- When using a 450-MHz core clock, configuration is from 96B to 256B in increments of 32B.

- BurstMax options:

- BurstMax = 256B, normal scheduling:

- Non-EOP bursts are 256B.

- EOP burst can be from 1B to 256B.

- BurstMax = 256B, enhanced scheduling (not supported in FlexE adapter mode):

- Configurable BurstMin of 64B or 128B.

- Non-EOP bursts are 256B.

- Penultimate burst when BurstMin is 128B: 128B or 256B.

- Penultimate burst when BurstMin is 64B: 192B or 256B.

- EOP bursts are from 64B to 256B.

#### 3.1.3.4 Interlaken In-Band Flow Control

Each Interlaken interface supports in-band flow control according to the Interlaken protocol definition.

The flow-control (FC) information is carried over the control words sent across the interface. Each control word includes a 16-bit flow-control field and a reset calendar bit. Each flow-control bit indicates the flow-control status (ON/OFF) of a specific Interlaken calendar channel. The BCM88480 supports a configurable calendar length between 16 to 256 channels (16, 32, 64, 128, and 256).

The BCM88480 supports two options for link level flow control (LLFC) mapping:

- Map the LLFC to flow control calendar channel #0.

- Map the LLFC to the first flow-control calendar channel in every control word (that is, entries 0, 16, 32, and so on). This option is useful for faster reaction times for LLFC, at the expense of flow-control channels.

The BCM88480 is flexible in flow-control processing, and each calendar entry can be mapped to one of the following flow-control reaction points:

- Link level (mapped to Interlaken NIF port)

- Channel level (mapped to OTM port)

- Egress queue pair level

Flow-control generation (flow-control transmission) – The BCM88480 can assign each calendar entry with flow control information or indications that may represent the following:

- Status of Interlaken port receive buffer (useful for link level).

- Status of the global resources (in other words, DRAM buffers).

- Status of a virtual-statistics queue May be programmed to generate flow control per Interlaken channel but enables more fine-grain flow-control indications; for example, per port and traffic class, per flow, and so on.

# 3.1.4 Bandwidth Provisioning of the Network Interface

The NIF of the BCM88480 allows flexible and oversubscribed connectivity that exceeds the switching capacity of the device.

When provisioning the device NIF ports, use the following calculations to avoid misconfiguration and unpredictable packet loss. In the equations, *INT* is the reserved bandwidth for internal ports (such as recycling, CPU, and so on), and *L1* is L1 switching between any FlexE group client and any Ethernet or ILKN interface.

**NOTE:** L1 switching between a FlexE group client and other FlexE group clients has no impact on the NIF provisioning and is not considered in this calculation.

For a core clock of 600 MHz, the maximum bandwidth provisioned to NIF ports (Ethernet, FlexE and Interlaken, but not ELK), is calculated by the following equation:

Maximum provisioned NIF bandwidth = 1.2 Tb/s – INT – (3 × L1)

For a core clock of 450 MHz (FlexE is not supported), the maximum bandwidth provisioned to NIF ports (Ethernet and Interlaken, but not ELK), is calculated by the following equation:

Maximum provisioned NIF bandwidth = 900 Gb/s - INT

For example, with a core clock of 600 MHz, active FlexE, 30 Gb/s reserved for internal ports, and 100-Gb/s L1 switching, the maximum bandwidth provisioned for NIF (ETH, ILKN, and L2 FlexE) is 870 Gb/s.

$870 \text{ Gb/s} = 1.2T - 30G - (3 \times 100G)$

# 3.2 External Lookup Engine

The packet processing engine uses various types of databases. To address the requirement of some applications for greater database capacity, the BCM88480 supports expansion of some databases with the use of an external lookup (ELK) interface.

NOTE: The BCM88480 does not support MAC table expansion over the ELK interface.

The BCM88480 ELK interface connects directly to Broadcom knowledge-based processor (KBP) devices.

The ELK interface has the following guidelines and characteristics:

- The ELK interface uses ILKN 0 from core 0.

- If ILKN 0 is used for ELK, ILKN 1 cannot be used.

- Up to 12 lanes are available for the ELK interface.

- ELK uses a SerDes rate of 25.78125.

# 3.3 Out-of-Band Flow Control

The BCM88480 supports out-of-band flow control (OOBFC) from the user to the BCM88480 (egress flow control or reception) and from the BCM88480 to the user (ingress flow control or generation).

The BCM88480 has two independent bidirectional OOBFC interfaces. Each interface can work in SPI-4.2 mode or Interlaken mode.

In all modes, the OOBFC interface supports the following:

- Reception Each calendar entry is mapped to a flow-control reaction point that is either:

- Link-level (NIF port)

- Channel-level (OTM port)

- Priority-level (egress queue pair)

- Generation (flow-control transmission) Each calendar entry represents a flow-control generation point that is either:

- Status of a virtual-statistics queue

- Status of the global resources, in other words, DRAM buffers

- Status of the port (MAC) receive buffer (link level)

- XON/XOFF signaling (no concept of credits, such as SPI-4.2)

In SPI-4.2 mode, the OOBFC interface has the following characteristics:

- SPI-4.2 status channel-like framing

- Calendar length of up to 512 entries

- Three-wire signaling for each direction Two data and one clock to support the following XON/XOFF indications:

- On TX STARVING = XON and SATISFIED = XOFF

- On RX XON = (HUNGRY or STARVING) and XOFF = SATISFIED

- SDR operation for data signals

- Transmission clock rate Core frequency divided by 6, 8, 10, 12, 14, or 16 (maximum rate is 166 MHz)

- Reception clock rate DC to 200 MHz

In Interlaken mode, the OOBFC interface has the following characteristics:

- Interlaken protocol

- Calendar length of up to 512 entries

- Reception and generation of Interlaken retransmit requests

- Three-wire signaling for each direction One each for clock, data, and sync

- 4b CRC protection

- DDR operation for data and sync signals

- Transmission clock rate Core frequency divided by 6, 8, 10, 12, 14, or 16 (maximum rate is 166 MHz)

- Reception clock rate Up to 180 MHz

NOTE: In-band and out-of-band flow-control signaling may be used simultaneously.

# 3.4 Synchronous Ethernet

The BCM88480 supports Synchronous Ethernet (SyncE) applications. The support includes two functions: controlling the transmit clock of network ports, and recovering a clock from a network port.

### 3.4.1 Transmit Clock

The transmit clock of each SerDes is locked to one of the NIF\_[3:0]\_REFCLK\_P/N input reference clocks (for mapping information, see the NIF\_[3:0]\_REFCLK\_P/N description in Section 4.3, Pin Description – Grouped by Function).

By connecting the system transmit clock to the NIF\_[3:0]\_REFCLK\_P/N inputs, it is possible to control the transmit clock of the SerDes.

### 3.4.2 Recovered Clock

The BCM88480 provides up to two recovered clocks that may be used as reference clocks for an external synchronization unit. The source for the recovered clocks can be any of the NIF SerDes configured as an Ethernet port. The BCM88480 drives two recovered clocks (SYNCE[1:0] CLK\_OUT) and a valid indication per clock (SYNCE[1:0] CLK\_OUT\_VALID).

**NOTE:** Support for clock recovery is as follows:

- Clock recovery is supported for a NIF interface configured as an Ethernet port or FlexE interface.

- Clock recovery is not supported for a 1G Ethernet interface.

The valid indication is asserted when the recovered clock is synchronized to the selected SerDes RX signal and can be used for system synchronization. The valid indication is based on a PCS lock and a link-up indication.

Each of the recovered clocks works as either a normal clock or a squelched clock. In normal clock mode, the CLK\_OUT is the recovered clock of the selected SerDes. In squelched mode, the CLK\_OUT halts if the RX of the selected link is not synced.

For multilane ports (for example, 40GbE or 100GbE), the recovered clock is derived from the first SerDes of the relevant port, and the valid signal is according to the linkup status of the entire port.

The recovered clock frequency is 25 MHz.

A fractional divider is used for generating an average clock of 25 MHz.

The following example describes how the average output frequency of 25 MHz is generated for a 100GbE port  $(4 \times 25.78125 \text{ Gb/s})$ .

The 25.78125 GHz is divided by 40, and the fractional divider, over 32 clock cycles, uses 7 clock cycles of a 25 divider  $[(25.78125 \div 40) \div 25]$  and 25 clock cycles of a 26 divider  $[(25.78125 \div 40) \div 26]$ , as shown in the following equation.

$$\frac{25.78125 \text{ GHz}}{40} \div \frac{(7 \times 25) + (25 \times 26)}{32} = 25 \text{ MHz}$$

Similarly:

- A fractional divider of 26.5625 GHz uses 14 clock cycles of a 26 divider and 18 clock cycles of a 27 divider.

- A fractional divider of 20.625 GHz uses 12 clock cycles of a 20 divider and 20 clock cycles of a 21 divider.

**NOTE:** An external jitter attenuator is required to clean the recovered clock before using it as a reference for the rest of the system.

# 3.5 IEEE 1588

The BCM88480 is a highly integrated device with many hardware hooks for designs that require network time synchronization with improved time-stamping accuracy on a nanosecond scale. The following features make the device ideally suited for time synchronization applications that comply with IEEE 1588.

- Supported modes:

- E2E and P2P transparent clock (TC).

- Boundary clock (BC).

- TC + OC timeReceiver, BC + OC timeReceiver.

- One-step clock features:

- On-the-fly egress packet modification including UDP checksum update and CRC update.

- All modifications to the correction field are handled in hardware.

- Very short residence time.

- All packets timestamped on ingress.

- Switch-packet processing engines identify IEEE 1588 packets.

- Two-step features:

- Egress timestamps are stored in per-port FIFO, along with IEEE 1588 sequence number.

- The CPU indicates which packets should generate a timestamp on egress.

- All packets are timestamped on ingress.

- Uses switch packet processing engines to identify IEEE 1588 packets and trap to CPU.

- Synchronizable timestamp counter:

- Can be phase-locked to external source.

- BroadSync<sup>®</sup> (timecode + event clock) interface.

- Broadcom PHY sync interface.

- Timestamped GPIOs.

- Frequency synthesizer:

- Additional clock divider: 10 MHz + 1 p/s.

- Low jitter.

**NOTE:** PTP/IEEE 1588 functionality is supported over Ethernet ports only. Timestamping is not supported over Interlaken interfaces.

**NOTE:** For information about PTP/IEEE 1588 over FlexE, refer to the *BCM88480 FlexE Overhead*, *OAM*, and *IEEE 1588 Handling* (88480-AN3xx).

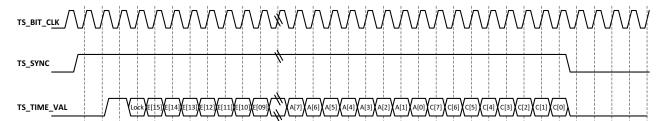

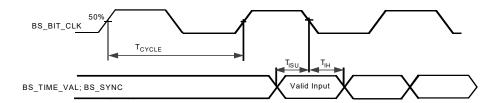

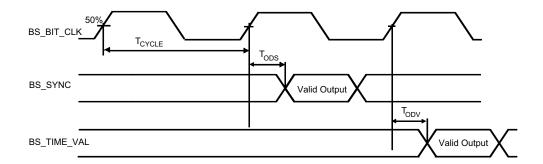

# 3.5.1 BroadSync External Interfaces

The BroadSync block provides the following external interfaces for providing timing information to off-chip devices or for retrieving timing information from external devices:

- Reference clock (input)

- External Sync 1 (input or output)

- External Sync 2 (input or output)

- Three-pin BroadSync interface (input or output):

- TS BIT CLK

- TS SYNC

- TS\_TIME\_VAL

The reference clock input is used for the clocking of all of the logic in the BroadSync block. The BroadSync block operates on a separate clock domain than the rest of the switch logic. The reference clock input should be driven from a low-jitter source to ensure that all time-related functions are accurate.