### **Product Brief**

### **Features**

- Line-side interface supports backplane channels (30-dB insertion loss) with high-performance receiver equalization

- Host-side interface compliant to the CEI-28G/56G-LR specifications supporting LR 30-dB channels

- · Supports FEC, bypassable

- Supports multiple standard/line rates in both PAM-4 and NRZ

- · Continuous auto-adaptive equalization

- Designed with low-power, 16-nm CMOS technology

- · Line-side and host-side loopbacks

- Advanced diagnostics, including eye monitoring feature with pseudorandom bit sequence (PRBS) generator and checker

- Single, low-cost 156.25-MHz reference clock

- Interoperability with Broadcom ASIC and Merchant Switch Silicon

- 19-mm × 19-mm, 1.0-mm pitch, 324-ball BGA, RoHS-compliant package

# BCM81330

# Octal 56-Gb/s PAM-4 Duplex Backplane PHY

## Overview

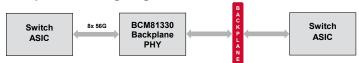

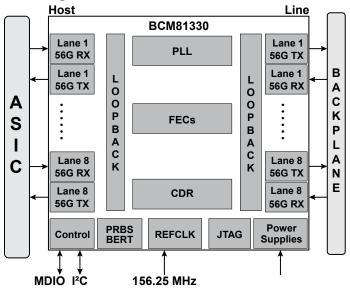

The Broadcom® BCM81330 is a single-chip, low-power Pulse Amplitude Modulation 4-Level (PAM-4) PHY. It integrates equalizer and retimer functions, supporting eight full-duplex, 56-Gb/s ports for backplane applications. In the octal 56-Gb/s mode, the BCM81330 supports duplex 8× 56-Gb/s PAM-4 to 8× 56-Gb/s PAM-4 to drive Long Reach (LR) (30 dB) backplane in fabric/line cards.

The BCM81330 also supports multiple standard/line rate, including both PAM-4 and Non Return-to-Zero (NRZ). The BCM81330 provides forward error corrections (FECs) support. On-chip clock synthesis is performed by a single, low-cost 156.25 MHz reference clock via high-frequency, low-jitter phase-locked loops (PLLs). Individual clock recovery is performed on the device by synchronizing directly to the respective incoming data streams.

The BCM81330 is designed in 16-nm CMOS technology to provide a low-power solution with integrated AC-coupling capacitors. The BCM81330 is available in a 19-mm × 19-mm, 1.0-mm pitch, 324-ball BGA, RoHS-compliant package.

#### **Block Diagram**

### **Backplane Retiming Diagram**