# BCM56072/BCM56071N Low-Power 440G Switch

### Overview

The Broadcom<sup>®</sup> BCM56072/BCM56071N is a low-power, 16-nm Ethernet switch with a small footprint and a flexible I/O that supports varied port speeds, from 1G through 100G. The BCM56072/BCM56071N can also connect directly to multigigabit (mGig) PHYs. The device supports a maximum of 440G bandwidth at line rate, with capability for up to 16 × 25G ports, 28 × 10G ports, or 48 × 2.5G ports.

The BCM56072/BCM56071N adds new functionalities that are aligned with networking market trends, especially security, reliability, and telemetry. The BCM56072/ BCM56071N includes an integrated OAM engine that simplifies fault isolation and performance monitoring, relieving CPU load for some of these functions and improving network reliability.

The low power, 1-ns timestamping accuracy, versatile I/O with high-speed and low-speed ports, and time-sensitive networking (TSN) support makes this device attractive for enterprise, connectivity, and mobile 5G wireless connectivity applications. The BCM56072/BCM56071N is part of the proven StrataXGS<sup>®</sup> family with the unified SDK, enabling quick time-to-market.

### Applications

- Enterprise

- Connectivity

### **Key Features**

- Flexible I/O that supports 1G, 2.5G, 5G, 10G, 25G, 40G, 50G, and 100G port speeds

- Support for direct connection to mGig PHYs

- Non-blocking architecture with 440G Gb/s line-rate performance

- Support for Time Sensitive Networking (TSN) features such as Seamless Redundancy Flow, Time Aware Scheduling, Time Aware Stream Filtering and Policing (IEEE802.1Qci), IEEE802.1AS-Rev

- Virtual Extensible LAN (VXLAN) support for next-generation wireless LAN and software-defined networking (SDN) support

- Support for port extender applications (IEEE802.1BR E-Tag and VN-Tag)

- Virtual routing and forwarding (VRF) to support isolated Layer 3 domains in a multi-tenant environment

- Full IPv4 and IPv6 routing support

- IEEE 1588 transparent clock with 1-ns timestamping accuracy on Falcon cores and synchronous Ethernet (SyncE) support

- Hardware support for Operations, Administration, and Maintenance (OAM), (IEEE 802.1ag and ITU-T Y.1731)

- Energy Efficient Ethernet (EEE) support

- Low-power 16-nm CMOS process

- Cut-through mode support for low-latency applications

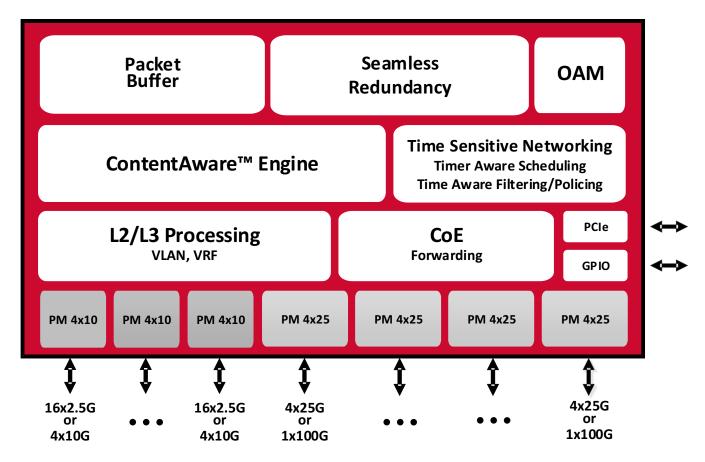

#### Figure 1: Device Block Diagram

## **Table of Contents**

| Chap | oter 1: Introduction                                        | 7  |

|------|-------------------------------------------------------------|----|

| Chap | oter 2: Device Description                                  | 8  |

| 2.1  | iProc Subsystem                                             | 8  |

| 2.2  | Port Configurations                                         | 9  |

|      | 2.2.1 Flexport Configurations                               | 10 |

| 2.3  | SerDes Interface Operating Rates                            | 12 |

| 2.4  | Port Mode Capabilities                                      | 14 |

|      | 2.4.1 PCIe Interface                                        | 14 |

|      | 2.4.2 Merlin Interface                                      | 14 |

|      | 2.4.3 Falcon Interface                                      | 15 |

| 2.5  | Feature List                                                |    |

| 2.6  | Memory                                                      | 25 |

| 2.7  | Target Applications                                         |    |

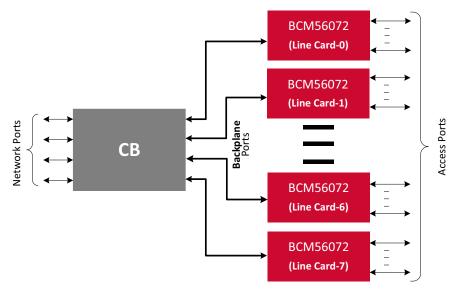

|      | 2.7.1 Enterprise Line Card Application                      |    |

| Chap | oter 3: System Functional Blocks                            | 29 |

| 3.1  | HiGig2 Support                                              | 29 |

|      | 3.1.1 HiGig2 Frame Structure                                | 29 |

| 3.2  | Energy Efficient Ethernet                                   |    |

|      | 3.2.1 EEE Control Policy                                    |    |

|      | 3.2.2 EEE-Related Register Controls and Statistics          |    |

| 3.3  | IEEE 1588                                                   |    |

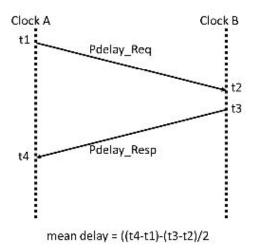

|      | 3.3.1 Hardware Support for Peer-to-Peer Pdelay_Req Messages |    |

|      | 3.3.1.1 Feature List                                        |    |

|      | 3.3.1.2 Functional Description                              | 31 |

| 3.4  | Thermal Monitor                                             |    |

|      | 3.4.1 Ports Register Associated with the Thermal Monitor    |    |

| Chap | oter 4: System Interfaces                                   | 33 |

| 4.1  | Overview                                                    |    |

| 4.2  | QSPI                                                        |    |

| 4.3  | SPI                                                         |    |

| 4.4  | PCIe                                                        |    |

| 4.5  | Broadcom Serial Controller                                  |    |

| 4.6  | UART                                                        |    |

| 4.7  | GPIO                                                        |    |

| 4.8  | LED                                                         |    |

| 4.9  | Merlin SerDes                                               |    |

|      | 4.9.1 Feature List                                          |    |

| 4.9.2 Functional Description                                               |    |

|----------------------------------------------------------------------------|----|

| 4.10 Falcon SerDes                                                         | 40 |

| 4.10.1 Feature List                                                        | 40 |

| 4.10.2 Functional Description                                              | 40 |

| 4.11 MIIM                                                                  | 41 |

| 4.12 JTAG                                                                  | 41 |

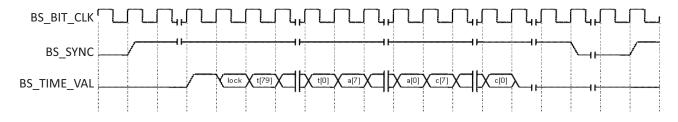

| 4.13 BroadSync Interface                                                   | 42 |

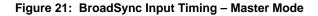

| 4.13.1 Master Mode: BroadSync Signals as Inputs                            | 42 |

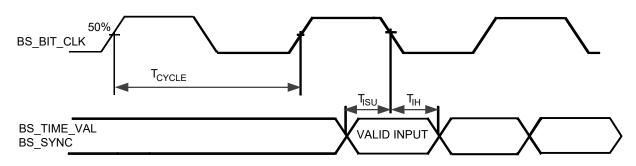

| 4.13.2 Slave Mode: BroadSync Signals as Outputs                            | 42 |

| 4.14 Ethernet Time Synchronization (SyncE)                                 | 43 |

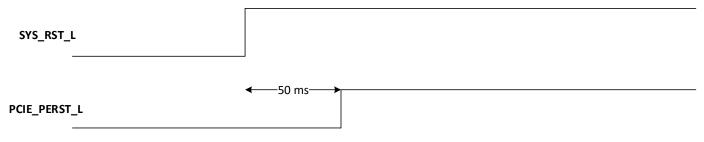

| 4.15 Reset                                                                 | 43 |

| Chapter 5: Pin Assignment and Signal Descriptions                          | 44 |

| 5.1 Pin Description: Grouped by Function                                   | 45 |

| 5.2 Pin List                                                               |    |

| 5.3 Shared Strap Pins                                                      | 57 |

| 5.4 Default IEEE 1588 and SyncE Pin Assignments                            | 58 |

| Chapter 6: Electrical Specifications                                       | 59 |

| 6.1 Absolute Maximum Ratings                                               |    |

| 6.2 DC Characteristics                                                     | 59 |

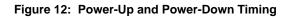

| 6.2.1 Operating Conditions                                                 | 59 |

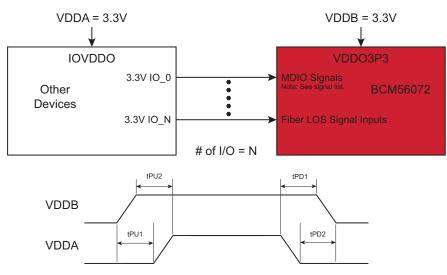

| 6.2.2 Power-Up and Power-Down Specifications                               | 60 |

| 6.2.2.1 Power-Up Sequence                                                  | 60 |

| 6.2.2.2 Power-Down Sequence                                                | 61 |

| 6.2.3 Sequencing Requirements for Non-Failsafe I/O Signals                 | 61 |

| 6.2.4 Power Supply Current and Power                                       | 63 |

| 6.2.5 Standard 3.3V Signals                                                | 63 |

| 6.2.6 PCIe Characteristics                                                 | 64 |

| 6.2.7 I <sup>2</sup> C Signals                                             | 64 |

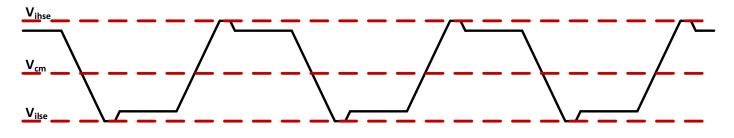

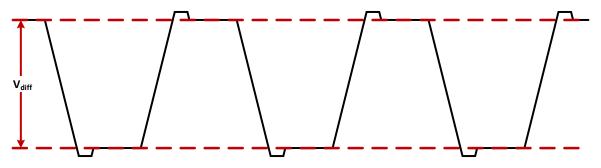

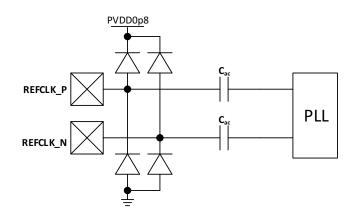

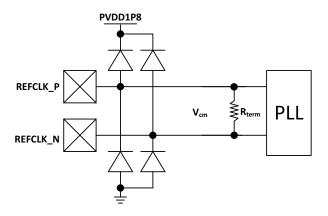

| 6.2.8 Reference Clocks                                                     | 65 |

| 6.2.8.1 LCPLL0 Reference Clock (LCPLL0_FREF)                               | 65 |

| 6.2.8.2 TimeSync PLL Reference Clock (TS_PLL_FREF)                         | 66 |

| 6.2.8.3 PCIe PLL Reference Clock (PCIe_REFCLK)                             | 66 |

| 6.2.8.4 BroadSync PLL Reference Clocks (BS_PLL0_REFCLK and BS_PLL1_REFCLK) | 67 |

| 6.2.9 Merlin Transceiver Electrical Specifications                         | 67 |

| 6.2.10 Falcon Quad SerDes Signal                                           | 68 |

| 6.2.11 AC-JTAG                                                             | 68 |

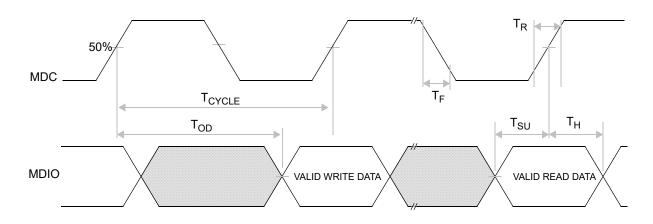

| 6.2.12 MIIM (MDIO) Signals                                                 | 69 |

| 6.3 AC Characteristics                                                     | 70 |

| 6.3.1 AC Timing for Reset                                                  | 70 |

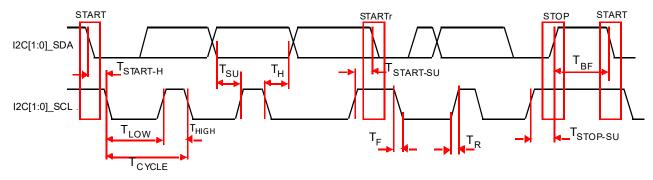

| 6.3.2 I <sup>2</sup> C AC Specifications                  |    |

|-----------------------------------------------------------|----|

| 6.3.3 MIIM (MDIO) AC Specifications                       | 72 |

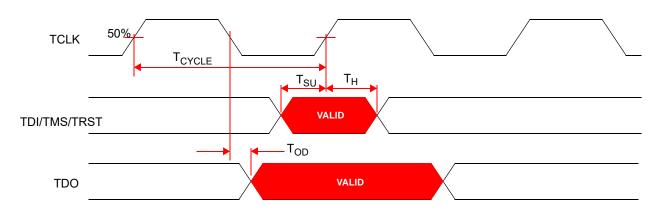

| 6.3.4 JTAG AC Specifications                              | 73 |

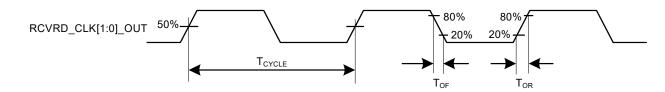

| 6.3.5 BroadSync AC Specifications                         |    |

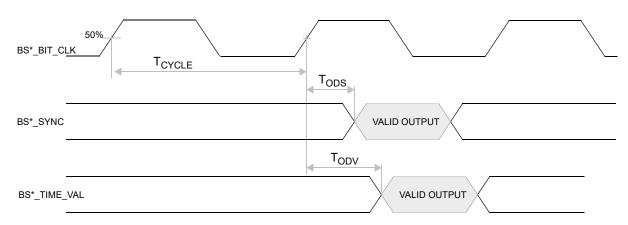

| 6.3.6 Synchronous Ethernet Interface Specifications       | 75 |

| 6.3.7 iProc QSPI Interface Timing Specifications          | 76 |

| 6.3.8 SPI Interface Timing Specification                  |    |

| 6.3.9 iProc PCIe Interface Timing Specifications          | 80 |

| 6.3.9.1 PCIE_REFCLK Timing                                | 80 |

| 6.3.9.2 PCIe_RX Timing                                    |    |

| 6.3.9.3 PCIe_TX Timing                                    | 81 |

| 6.3.10 LED Controller Interface Specifications            | 82 |

| 6.3.11 LCPLL0_FREF Clock Requirements                     |    |

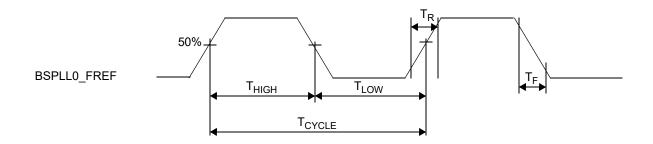

| 6.3.12 BSPLL0_FREF Clock Requirements                     | 85 |

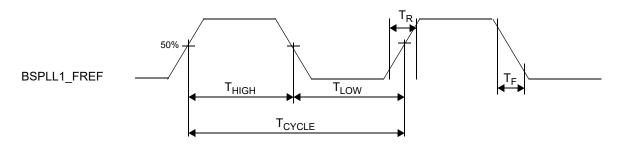

| 6.3.13 BSPLL1_FREF Clock Requirements                     | 86 |

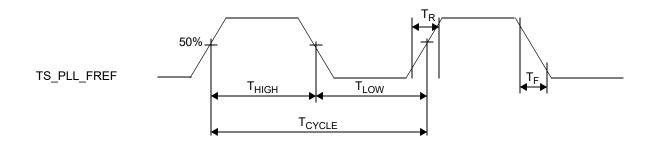

| 6.3.14 TS_PLL_FREF Clock Requirements                     |    |

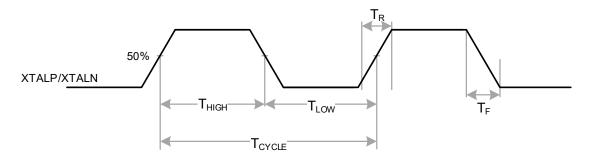

| 6.3.15 XTAL Clock Requirements                            |    |

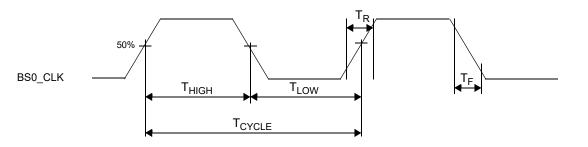

| 6.3.16 BS0_CLK Output Clock                               |    |

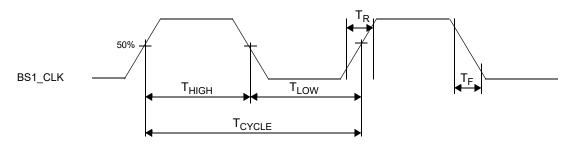

| 6.3.17 BS1_CLK Output Clock                               |    |

| 6.3.18 Merlin AC Specifications                           |    |

| 6.3.19 Merlin SerDes AC Specifications                    | 91 |

| 6.3.19.1 Merlin SerDes Interface Output Timing            |    |

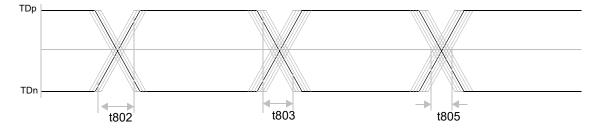

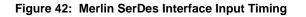

| 6.3.19.2 Merlin SerDes Interface Input Timing             | 91 |

| 6.3.20 Merlin XAUI SerDes AC Specifications               |    |

| 6.3.20.1 Merlin XAUI SerDes Receiver AC Specifications    |    |

| 6.3.20.2 Merlin XAUI SerDes Transmitter AC Specifications |    |

| 6.3.21 Falcon Serial Interface AC Specification           |    |

| 6.3.22 10GBASE-KR Electrical Characteristics              |    |

| 6.3.22.1 Transmitter                                      |    |

| 6.3.22.2 Receiver                                         |    |

| Chapter 7: Thermal Information                            |    |

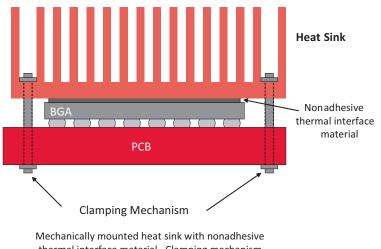

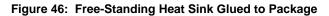

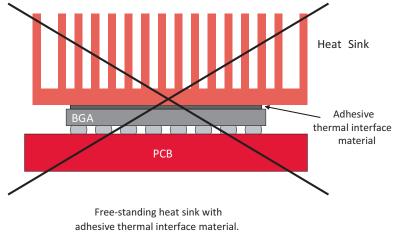

| 7.1 Heat Sink                                             |    |

| 7.1.1 Heat Sink Selection                                 |    |

| 7.1.2 Heat Sink Attachment                                |    |

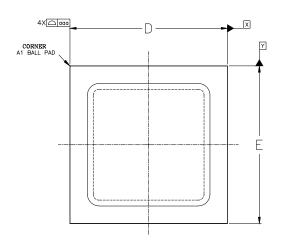

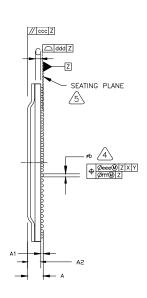

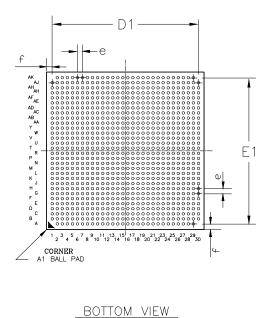

| Chapter 8: Mechanical Information                         |    |

| Chapter 9: Ordering Information                           |    |

| 9.1 Devices                                               |    |

| 9.2 Lead-Free Packaging                                   |    |

| Related Documents                                         |    |

|                                                           |    |

Low-Power 440G Switch

## **Chapter 1: Introduction**

This document describes the Broadcom® BCM56072/BCM56071N System-on-a-Chip (SoC).

The Broadcom BCM56072/BCM56071N is a complete L2/L3 SoC solution for rapid development of Ethernet switching applications. This device provides different interface modes.

This flexible I/O device with 440G throughput is ideally suited for low-cost, dual-homed line cards for centralized chassis and provider edge (PE) pizza boxes and embedded connectivity switch applications. This device combines all the functions of a high-speed switch system into a single 16-nm CMOS device.

The following table summarizes the high-level features of devices in the BCM56072/BCM56071N device.

#### Table 1: BCM56072/BCM56071N Feature List

| Feature                     | BCM56072                                 | BCM56071N                                |

|-----------------------------|------------------------------------------|------------------------------------------|

| I/O bandwidth               | 440G                                     | 320G                                     |

| Package                     | 25 × 25 mm                               | 25 × 25 mm                               |

| Ball pitch                  | 0.8                                      | 0.8                                      |

| SDK support                 | $\checkmark$                             | ✓                                        |

| Port configuration          | See Table 2, Ethernet Port Configuration | See Table 2, Ethernet Port Configuration |

| Serial LEDs                 | $\checkmark$                             | ✓                                        |

| Parallel flash              | No                                       | No                                       |

| GPIOs                       | 16                                       | 16                                       |

| DDR3/DDR4                   | No                                       | No                                       |

| Serial flash (QSPI)         | $\checkmark$                             | $\checkmark$                             |

| SPI master/slave            | $\checkmark$                             | ✓                                        |

| PCIe Gen3                   | $\checkmark$                             | ✓ <i>✓</i>                               |

| MDC/MDIO 1                  | $\checkmark$                             | ✓                                        |

| MDC/MDIO 0                  | $\checkmark$                             | $\checkmark$                             |

| Number of UARTs             | 2                                        | 2                                        |

| BroadSync <sup>®</sup>      | ✓                                        | ✓                                        |

| Number of I <sup>2</sup> Cs | 2                                        | 2                                        |

| USB 2.0                     | No                                       | No                                       |

| Loss of Signal (LoS) pins   | 7                                        | 7                                        |

| TDPLL                       | No                                       | No                                       |

| 1588-TC                     | $\checkmark$                             | ✓ ·                                      |

| 1588-OC                     | ✓                                        | $\checkmark$                             |

| 1588-BC                     | ✓                                        | $\checkmark$                             |

| TSN                         | ✓                                        | $\checkmark$                             |

## **Chapter 2: Device Description**

The BCM56072/BCM56071N has a modular, high-performance, pipelined packet-switching (BroadScale<sup>®</sup>) architecture. This architecture provides the following capabilities:

- Cost reduction

- Migration to different process technologies without architectural changes

- Flexible port configurations

- Scalable throughput

- Scalable custom features

### 2.1 iProc Subsystem

This section lists the full feature sets of the iProc system within the switch device.

- Two R5 for general processing

- Four Cortex-M0 CPUs

- Quad Serial Peripheral Interface (QSPI) interface (master or slave)

- One PCIe Gen3-compliant port with a single-lane SerDes supporting end-point operating mode

- Low-speed interfaces:

- 1 × Serial Peripheral Interface (SPI) for serial NOR flash support

- 2 × UARTs

- Supports 16 × GPIOs

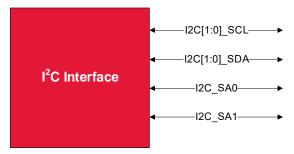

- 2 × Broadcom Serial Control (BSC). The BSC is NXP I<sup>2</sup>C-compatible

- Two timestamped GPIOs (TS\_GPIOs)

- 2 × external MDIO rings (CMICx)

- JTAG

- Primary and backup recovered clock outputs (SyncE)

- 2 × BroadSync interfaces

- 2 × LED interfaces driven by M0

## 2.2 Port Configurations

The BCM56072/BCM56071N device port configuration capabilities are summarized in the following tables. For the available port mode configurations on each Flexport<sup>™</sup>, see the tables in Section 2.2.1, Flexport Configurations.

#### Table 2: Ethernet Port Configuration

|                        | Falcon SerDes    |                  |                  | Merlin SerDes    |               |               |               |

|------------------------|------------------|------------------|------------------|------------------|---------------|---------------|---------------|

|                        | CLPort 0         | CLPort 1         | CLPort 2         | CLPort 3         | PMQ 0         | PMQ 1         | PMQ 2         |

| Part Number            | Falcon0          | Falcon1          | Falcon2          | Falcon3          | MerlinQ0      | MerlinQ1      | MerlinQ2      |

| BCM56072               | _                | F.CAUI.Gen3      | F.CAUI.Gen3      | F.2xHG[53].Gen3  | F.XLAUI-QXG   | F.XLAUI-QXG   | F.XLAUI-QXG   |

|                        | F.CAUI.Gen3      | F.CAUI.Gen3      | F.CAUI.Gen3      | F.CAUI.Gen3      | —             | —             | _             |

|                        | F.HG[42]-UL.Gen3 | F.CAUI.Gen3      | F.CAUI.Gen3      | F.HG[42]-UL.Gen3 | F.HG[42].Gen2 | F.HG[42].Gen2 | F.HG[42].Gen2 |

|                        | F.2xHG[53].Gen3  | F.2xHG[53].Gen3  | F.2xHG[53].Gen3  | F.2xHG[53].Gen3  | F.HG[42].Gen2 | —             |               |

|                        | F.2xHG[53].Gen3  | F.2xHG[53].Gen3  | F.2xHG[53].Gen3  | F.2xHG[53].Gen3  | F.MGL.Gen2    | F.MGL.Gen2    | F.MGL.Gen2    |

|                        | F.MGL.Gen3       | F.HG[42]-UL.Gen3 | F.HG[42]-UL.Gen3 | F.MGL.Gen3       | F.MGL.Gen2    | F.MGL.Gen2    | F.MGL.Gen2    |

| BCM56071N <sup>a</sup> | —                | F.CAUI.Gen3      | F.CAUI.Gen3      | _                | F.XLAUI-QXG   | F.XLAUI-QXG   | F.XLAUI-QSG   |

a. Falcon0 and Falcon3 are disabled in hardware. Merlin2 does not support QXGMII (4 × 2.5G) mode, but it does support QSGMII (4 × 1G) mode.

### 2.2.1 Flexport Configurations

- **NOTE:** Flexport configurations are limited to flexible port configurations that can be set up on device boot up. No runtime changes are possible in this device.

- **NOTE:** The port configuration options are hierarchical definitions. For example, in F.CAUI.Gen3 mode, the macro supports either 100GE mode or F.2xHG[53] mode.

#### Table 3: F.CAUI.Gen3 Configuration Options

| Lane 1          | Lane 2 | Lane 3 | Lane 4 |  |  |

|-----------------|--------|--------|--------|--|--|

|                 | 100GE  |        |        |  |  |

| F.2xHG[53].Gen3 |        |        |        |  |  |

#### Table 4: F.2xHG[53].Gen3 Configuration Options

| Lane 1              | Lane 2              | Lane 3              | Lane 4              |  |

|---------------------|---------------------|---------------------|---------------------|--|

| HGd[53]/HGd[50]     |                     | HGd[53]/HGd[50]     |                     |  |

| 50                  | GE                  | 50GE                |                     |  |

| HGs[27]/HGs[25]     | HGs[27]/HGs[25]     | HGs[27]/HGs[25]     | HGs[27]/HGs[25]     |  |

| 25GE/10GE/2.5GE/1GE | 25GE/10GE/2.5GE/1GE | 25GE/10GE/2.5GE/1GE | 25GE/10GE/2.5GE/1GE |  |

#### Table 5: F.HG[42]-UL.Gen3 Configuration Options

| Lane 1             | Lane 2          | Lane 3          | Lane 4          |  |

|--------------------|-----------------|-----------------|-----------------|--|

| HG[42]/HG[40]/40GE |                 |                 |                 |  |

| HGd[21]            | /HGd[20]        | HGd[21]/HGd[20] |                 |  |

| HGs[11]/HGs[10]    | HGs[11]/HGs[10] | HGs[11]/HGs[10] | HGs[11]/HGs[10] |  |

| 10GE/2.5GE/1GE     | 10GE/2.5GE/1GE  | 10GE/2.5GE/1GE  | 10GE/2.5GE/1GE  |  |

#### Table 6: F.MGL.Gen3 Configuration Options

| Lane 1 | Lane 2 | Lane 3 | Lane 4 |

|--------|--------|--------|--------|

| 2.5GE  | 2.5GE  | 2.5GE  | 2.5GE  |

| 1GE    | 1GE    | 1GE    | 1GE    |

#### Table 7: F.XLAUI-QXG Configuration Options

| Lane 1                                  | Lane 2              | Lane 3              | Lane 4              |  |  |

|-----------------------------------------|---------------------|---------------------|---------------------|--|--|

| F.HG[42].Gen2                           |                     |                     |                     |  |  |

| QXGMII <sup>a</sup> QXGMII <sup>a</sup> |                     | QXGMII <sup>a</sup> | QXGMII <sup>a</sup> |  |  |

| QSGMII <sup>b</sup>                     | QSGMII <sup>b</sup> | QSGMII <sup>b</sup> | QSGMII <sup>b</sup> |  |  |

a. Each lane can connect to an external QXGMII PHY that supports the following interfaces: 4 × 2.5GE, 4 × GE, 4 × 100M FD/HD, or 4 × 10M FD/HD.

b. Each lane can connect to an external QSGMII PHY that supports the following interfaces: 4 × GE, 4 × 100M FD/HD, or 4 × 10M FD/HD.

#### Table 8: F.XLAUI-QSG Configuration Options

| Lane 1                                                                          | Lane 2 | Lane 3 | Lane 4 |  |  |

|---------------------------------------------------------------------------------|--------|--------|--------|--|--|

| F.HG[42].Gen2                                                                   |        |        |        |  |  |

| QSGMII <sup>a</sup> QSGMII <sup>a</sup> QSGMII <sup>a</sup> QSGMII <sup>a</sup> |        |        |        |  |  |

a. Each lane can connect to an external QSGMII PHY that supports the following interfaces: 4 × GE, 4 × 100M FD/HD, or 4 × 10M FD/HD.

#### Table 9: F.HG[42].Gen2 Configuration Options

| Lane 1                     | Lane 2                     | Lane 3                     | Lane 4                     |  |  |

|----------------------------|----------------------------|----------------------------|----------------------------|--|--|

| HG[42]/HG[40]              |                            |                            |                            |  |  |

|                            | 40GE                       |                            |                            |  |  |

| HGd[21]                    | /HGd[20]                   | HGd[21]/HGd[20]            |                            |  |  |

| HGs[11]/HGs[10]            | HGs[11]/HGs[10]            | HGs[11]/HGs[10]            | HGs[11]/HGs[10]            |  |  |

| 10GE/5GE/2.5GE/1GE/100M FD | 10GE/5GE/2.5GE/1GE/100M FD | 10GE/5GE/2.5GE/1GE/100M FD | 10GE/5GE/2.5GE/1GE/100M FD |  |  |

#### Table 10: F.MGL.Gen2 Configuration Options

| Lane 1            | Lane 2            | Lane 3            | Lane 4            |

|-------------------|-------------------|-------------------|-------------------|

| 2.5GE/1GE/100M FD | 2.5GE/1GE/100M FD | 2.5GE/1GE/100M FD | 2.5GE/1GE/100M FD |

## 2.3 SerDes Interface Operating Rates

The SerDes port module allows the device to support low-latency throughput.

Ports set to run with HiGig2<sup>™</sup> protocols see a few packets lost when an I/Os stream is at line rate. For more information, see Footnote a in the following table.

#### Table 11: Operating Rates

| SerDes Rate       | Number<br>of<br>SerDes | Encoding      | Interface                                                                                              | Total SerDes<br>Rate | Post<br>Encoding<br>Rate | HiGig2<br>(Ethernet<br>Bandwidth) <sup>a</sup> |

|-------------------|------------------------|---------------|--------------------------------------------------------------------------------------------------------|----------------------|--------------------------|------------------------------------------------|

| Ethernet          |                        |               |                                                                                                        |                      |                          |                                                |

| 1.25G             | 1                      | 8B/10B        | SGMII: 10/100/1000 SGMII                                                                               | 1.25000G             | 1.0000G                  | N/A                                            |

| 1.25G             | 1                      | 8B/10B        | 1GE:1000BASE-X                                                                                         | 1.25000G             | 1.0000G                  | N/A                                            |

| 3.125G            | 1                      | 8B/10B        | 2.5GE: 2500BASE-X                                                                                      | 3.12500G             | 2.5000G                  | N/A                                            |

| 10.3125G          | 1                      | 64B/66B       | 10G-QXGMII                                                                                             | 10.3125G             | 10.000G                  | N/A                                            |

| 5G                | 4                      | 8B/10B        | QSGMII                                                                                                 | 5.00000G             | 4.0000G                  | N/A                                            |

| 6.25/<br>5.15625G | 1                      | . ,           | MGBASE-T: 5GE XFI (5G mGig)<br>5.15625G data rate, 5000BASE-R                                          | 5.00000G             | 5.0000G                  | N/A                                            |

| 10.31250G         | 1                      | 64B/66B       | 10GE: XFI, SFI (MerlinCore only),<br>10GBASE-KR, 10GBASE-LR,<br>10GBASE-SR, 10GBASE CR                 | 10.31250G            | 10.0000G                 | N/A                                            |

| 10.31250G         | 2                      | 64B/66B (MLD) | 20GE-2: 20GBASE-KR2,<br>20GBASE-CR2 (FalconCore only)                                                  | 20.62500G            | 20.0000G                 | N/A                                            |

| 25.78125G         | 1                      | 64B/66B       | 25GE: 25GBASE-KR, 25GBASE-CR                                                                           | 25.78125G            | 25.0000G                 | N/A                                            |

| 10.31250G         | 4                      | 64B/66B (MLD) | 40GE-4: XLAUI, XLPPI (FalconCore only),<br>40GBASE KR4,<br>40GBASE-LR4,<br>40GBASE-SR4,<br>40GBASE-CR4 | 41.25000G            | 40.0000G                 | N/A                                            |

| 20.62500G         | 2                      | 64B/66B (MLD) | 40GE-2: MLD2, VSR2                                                                                     | 41.25000G            | 40.0000G                 | N/A                                            |

| 25.78125G         | 2                      | 64B/66B (MLD) | 50GE-2: MLD2, VSR2                                                                                     | 51.56250G            | 50.0000G                 | N/A                                            |

| 25.78125G         | 4                      | 64B/66B (MLD) | 100GE-4: CAUI, 100GBASE-KR4,<br>100GBASE-LR4, 100GBASE-SR4,<br>100GBASE-CR4                            | 103.12500G           | 100.0000G                | N/A                                            |

#### Table 11: Operating Rates (Continued)

| SerDes Rate | Number<br>of<br>SerDes | Encoding             | Interface            | Total SerDes<br>Rate | Post<br>Encoding<br>Rate | HiGig2<br>(Ethernet<br>Bandwidth) <sup>a</sup> |

|-------------|------------------------|----------------------|----------------------|----------------------|--------------------------|------------------------------------------------|

| HiGig2      |                        |                      |                      |                      |                          |                                                |

| 10.93750G   | 1                      | 64B/66B              | HGs[11] <sup>b</sup> | 10.93750G            | 10.6061G                 | 10.1234G                                       |

| 10.3125G    | 2                      | 64B/66B <sup>c</sup> | HGd[20]              | 20.6250G             | 20.0000G                 | 19.0900G                                       |

| 10.93750G   | 2                      | 64B/66B (MLD)        | HGd[21] <sup>d</sup> | 21.87500G            | 21.2121G                 | 20.2469G                                       |

| 27.34375G   | 1                      | 64B/66B              | HGs[27] <sup>e</sup> | 27.34375G            | 26.5151G                 | 25.3087G                                       |

| 10.93750G   | 4                      | 64B/66B (MLD)        | HG[42]               | 43.75000G            | 42.4242G                 | 40.4939G                                       |

| 25.78125G   | 2                      | 64B/66B (MLD)        | HGd[50]              | 51.56250G            | 50.0000G                 | 47.7250G                                       |

| 27.34375G   | 2                      | 64B/66B (MLD)        | HGd[53]              | 54.68750G            | 53.0303G                 | 50.6174G                                       |

a. The HiGig2 (Ethernet Bandwidth) is calculated based on the assumption of having HG\_IPG = 8 bytes and a minimum payload size of 64 bytes. For example, a HG[11]-1 port will have an effective Ethernet switching bandwidth of 10.1240G. This is based on the following formula:

• HG (Ethernet Bandwidth) = HG[speed] × Ethernet\_Efficiency

- HG[speed] = N\_Lanes × Baud Rate × Encoding

- Ethernet\_Efficiency =  $(E_1PG + Preamble + E_Payload) \div (HG_1PG + HG_Header + E_Payload) = (12 + 8 + 64) \div (8 + 16 + 64) = 95.45\%$

- b. A small amount of packet loss is observed when a port set to HGs[11] runs at line rate because only 10 Gb/s data bandwidth is allocated to the port.

- c. This 64B/66B encoding is a Broadcom-proprietary implementation. Falcon supports only IEEE standard 64B/66B encoding.

- d. A small amount of packet loss is observed when a port set to HGd[21] runs at line rate because only 20-Gb/s data bandwidth is allocated to the port.

- e. A small amount of packet loss is observed when a port set to HGs[27] runs at line rate because only 25-Gb/s data bandwidth is allocated to the port.

- NOTE: Broadcom-proprietary 64B/66B encoding is not supported in the Falcon (TSC4-F) SerDes core. Other legacy devices that use Eagle (TSC4-E), TSC-4, or Warpcore<sup>®</sup> support both IEEE and Broadcom-proprietary 64B/66B encoding. Therefore, when Falcon operates in a HiGig<sup>™</sup> mode, such as HG[42] and interfacing to a legacy device, the legacy device must enable IEEE 64B/66B encoding rather than Broadcom-proprietary 64B/66B encoding.

#### Table 12: Port Terminology

| Port Terms                    | Standard    | Port Speed   | Standard Terminology |

|-------------------------------|-------------|--------------|----------------------|

| Multigigabit (mGig)           | IEEE802.3bz | 5G, 2.5G, 1G | MGBASE-T (5.0 Gb/s)  |

| Multigigabit-Lite (mGig-Lite) | IEEE802.3bz | 2.5G, 1G     | NBASE-T (2.5 Gb/s)   |

## 2.4 Port Mode Capabilities

The BCM56072/BCM56071N contains three types of SerDes interfaces: the PCIe Gen3 PHY, the Merlin SerDes interface, and the Falcon SerDes interface. Each of these interfaces has different capabilities depending on the device part number and selected configuration option. This section describes the various capabilities of each SerDes interface.

### 2.4.1 PCIe Interface

The PCIe interface provided by the BCM56072/BCM56071N conforms to PCIe Gen 3.0 specifications.

- PCIe controller supports a single-lane endpoint configuration

- Root port configuration is not supported

### 2.4.2 Merlin Interface

The Merlin SerDes interfaces are primarily used for high-speed front-panel ports, up-links, or stacking ports. For operating modes in a given Merlin core, the following features are applied:

- Quad 10G SerDes with QSGMII/10G-QXGMII support.

- Supports 1 PLL per quad.

- 5G XFI (5.15625 Gbaud or 64/66 5 Gb/s), QSGMII, and 10G-QXGMII in multiport mode (4 × 1G and 4 × 2.5G) are supported.

- XFI, SFI, XAUI, 1000BASE-X, and 2500BASE-X (8b/10b, no auto-negotiation) is supported.

- 10GBASE-KR, 10GBASE-LR, 10GBASE-SR, 10GBASE-CR, 40GBASE-KR4, 40GBASE-CR4, 40GBASE-LR4, and 40GBASE-SR4 interface types are supported.

- 20G HG+ (two lanes), 21G HG2 (two lanes), and 42G HG2 (four lanes) is supported.

- Single-lane FEC (Clause 74).

- Supports half-duplex mode for 10/100 Mb/s speed with external GPHY in QSGMII interface mode.

- 1G/10G (native Ethernet) or HGs[10] mix in the same SerDes supporting HGd[20].

- Polarity inversion can be made on both the TD and RD paths with individual lane controls.

- The lane-swap capability is restricted to RD lanes in the receive path and TD lanes in the transmit path. Lane swapping

across TD and RD lanes is not supported.

- 1G (native Ethernet)/10G (native Ethernet or HGSolo[10]) mix in the same quad is supported.

- HiGigSolo[11] (HG+/HG2 packets over 10.9375-GHz lane, in other words, overclocked XFI) is supported.

- 1G and 10G port mix over the backplane is supported in the same quad.

### 2.4.3 Falcon Interface

The Falcon (TSC4-F) SerDes core interfaces are primarily used for high-speed up-links or stacking ports. For operating modes in a given Falcon core, the following features are applied:

- Clause 73 full-duplex is supported where applicable.

- 1000BASE-X and 2500BASE-X are supported.

- 100GBASE-KR4, 100GBASE-SR4, 100GBASE-LR4, and 100GBASE-CR4 are supported.

- 1000BASE-KX and SFI are supported, but the mix of port speeds is limited to a shared VCO.

- XFI, 10GBASE-KR, 10GBASE-CR, 10GBASE-LR, 10GBASE-SR, and 5000BASE-R are supported.

- XAUI is not supported.

- HGd[21], HGs[27], HG[42], and HGd[53] are supported.

- HGs[11] (HG+/HG2 packets over 10.9375 GHz lane, in other words, overclocked XFI) is supported.

- 1G/10G (native Ethernet) or HGs[10] mix in the same SerDes supporting HGd[20].

- 1G/10G Ethernet mix in the same quad, concurrently.

- 1G/25G Ethernet mix in the same quad, concurrently.

- 10G/25G Ethernet mix in the same quad, concurrently.

- Clause 91 FEC is supported on 25G, 25G HG2, 50G, 53G HG2, 100G, and 106G interfaces.

- Clause 74 FEC is supported for 10G and 40G interfaces.

- Half-duplex is not supported.

- 1G, 2.5G, 10G, 25G, and 50G (MLD) Ethernet mix is supported in the same quad.

- Polarity inversion can be made on both the TD and RD paths with individual lane controls.

- The lane swap capability is restricted to RD lanes in the receive path and TD lanes in the transmit path. Lane swapping

across TD and RD lanes is not supported.

**NOTE:** 5G and 25G cannot operate within the same port macro.

### 2.5 Feature List

The feature list in the following table applies to the BCM56072/BCM56071N.

#### Table 13: Feature List

| Feature                         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Interfaces                      | <ul> <li>PCIe Gen3 1-lane.</li> <li>16 GPIOs.</li> <li>UART.</li> <li>JTAG.</li> <li>BroadSync.</li> <li>Serial LED for network ports.</li> <li>MDC/MDIO.</li> <li>QSPI, SPI, and I<sup>2</sup>C.</li> <li>Sixteen 25G SerDes (four Falcon cores, four lanes per core).</li> <li>Flexible SerDes contains four SerDes lanes per Falcon core, configured to operate in any of the following configurations: <ul> <li>10GbE XFI, SFI, KR, CR, SR, and LR (CL74) (1-lane).</li> <li>20GbE KR2 (CL74) (2-lane).</li> <li>20GbE KR2 (CL74) (2-lane).</li> <li>40GbE MLD2 and VSR2 (2-lane).</li> <li>40GbE MLD2 and VSR2 (2-lane) (L108)</li> <li>100GbE KR4, CR4, SR4, ER4, and LR4 (CL74) (4-lane).</li> <li>50GbE MLD2 and VSR2 (2-lane) (CL74) (4-lane)</li> </ul> </li> <li>Twelve 10G SerDes (three Merlin cores, four lanes per core).</li> <li>Flexible SerDes contains four SerDes lanes per Merlin Core, configured to operate in any of the following configurations: <ul> <li>10/100 BASE-X.</li> <li>2500BASE-X.</li> <li>2500BASE-X.</li> <li>200BE KR2 (CL74) (2-lane).</li> <li>40GbE XL, SFI, KR, CR, SR, ER, and LR (CL74) (1-lane).</li> <li>200BE KR2 (CL74) (2-lane).</li> <li>40GbE XL, VL, XLPPI, KR4, CR4, SR4, ER4, and LR4 (CL74) (4-lane).</li> <li>500BE XLAU, XLPPI, KR4, CR4, SR4, ER4, and LR (CL74) (1-lane).</li> <li>200BE KR2 (CL74) (2-lane).</li> <li>40GbE XLAU, XLPPI, KR4, CR4, SR4, ER4, and LR (CL74) (4-lane).</li> <li>200BE KR2 (CL74) (2-lane).</li> <li>40GbE XLAU, XLPPI, KR4, CR4, SR4, ER4, and LR4 (CL74) (4-lane).</li> <li>200BE KR2 (CL74) (2-lane).</li> <li>40GbE XLAU, XLPPI, KR4, CR4, SR4, ER4, and LR4 (CL74) (4-lane).</li> <li>200BE KR2 (CL74) (2-lane).</li> <li>40GbE XLAU, XLPPI, KR4, CR4, SR4, ER4, and LR4 (CL74) (4-lane).</li> <li>200BE KR2 (CL74) (2-lane).</li> <li>40GbE XLAU, XLPPI, KR4, CR4, SR4, ER4, and LR4 (CL74) (4-lane).</li> <li>40GbE XLAU, XLPPI, KR4, CR4, SR4, ER4, and LR4 (CL74) (4-lane).</li> <li>MLD-HiGigg 2 HG[42] (CL74) (4-lane).</li> <li>40GbE XLAU, XLPPI, KR4, CR4, SR4, ER4, and LR4 (CL74) (4-lane).</li> <li>40GbE XLAU, XLPPI, KR</li></ul></li></ul> |

| Integrated Processors           | <ul> <li>10G-QXGMII.</li> <li>4 Cortex M0 and 2 R5 CPU.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Flexible Port<br>Configurations | <ul> <li>12 × 10GE + 6 × 50GE or 12 × 25GE.</li> <li>48 × 2.5GE + 6 × 50GE or 12 × 25GE.</li> <li>20 × 10GE</li> <li>1 × 100GE + 2 × 100GE.</li> <li>2 × 100GE + 2 × 100GE (bump-in-the-wire).</li> <li>28 × 10GE or 7 × 40GE.</li> <li>40 × 1GE + 8 × 2.5GE + 2 × 25GE + 10 × 10GE.</li> <li>48 × 1GE + 6 × 50GE or 12 × 25GE.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Feature                            | Description                                                                                                                                                                                                                                                                                            |

|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAC Characteristics                | <ul> <li>Supports:         <ul> <li>Ethernet/IEEE 802.3 frame sizes (64 bytes to 1522 bytes).</li> <li>Jumbo frames up to 12,288 bytes.</li> <li>EEE.</li> </ul> </li> <li>Supports IEEE 802.1AS, pre-standard IEEE 802.1AS-Rev, IEEE 1588, and IEEE 1588v2-2008 network time distribution:</li> </ul> |

|                                    | <ul> <li>IEEE 1588 and pre-standard 802.1AS-Rev.</li> <li>Transparent clock (TC), boundary clock (BC), and ordinary clock (OC).</li> <li>Supports SyncE layer-1 clock recovery.</li> </ul>                                                                                                             |

| 802.3ad Link                       | <ul> <li>128 trunk groups supported with up to eight members per group. No adjacency limitation.</li> </ul>                                                                                                                                                                                            |

| Aggregation                        | <ul> <li>Traffic load distribution for L2 switched and L3 routed packets.</li> </ul>                                                                                                                                                                                                                   |

|                                    | <ul> <li>Trunk port selection based on a hash on source or destination MAC, VLAN, EtherType, source or destination<br/>IP address, and TCP or UDP ports.</li> </ul>                                                                                                                                    |

|                                    | Trunk port selection for DLF, broadcast, and multicast packets.                                                                                                                                                                                                                                        |

| HiGig Trunking                     | Eight HiGig trunk groups supported with up to eight members per group. HiGig trunk failover supported.                                                                                                                                                                                                 |

| VLANs                              | Supports 4K VLAN assignment for untagged and priority tagged packets based on the following:                                                                                                                                                                                                           |

|                                    | 64 IP subnet-based VLANs.                                                                                                                                                                                                                                                                              |

|                                    | ■ 16 protocol-based VLANs.                                                                                                                                                                                                                                                                             |

|                                    | ■ 1K MAC-based VLANs.                                                                                                                                                                                                                                                                                  |

|                                    | ■ 256 flow-based VLAN.                                                                                                                                                                                                                                                                                 |

|                                    | ■ IEEE 802.1p.                                                                                                                                                                                                                                                                                         |

|                                    | IEEE 802.1Q ingress port.                                                                                                                                                                                                                                                                              |

|                                    | Additional VLAN features include the following:                                                                                                                                                                                                                                                        |

|                                    | Independent VLAN learning (IVL) and shared VLAN learning (SVL).                                                                                                                                                                                                                                        |

|                                    | Ingress filtering for IEEE 802.1Q VLAN security.                                                                                                                                                                                                                                                       |

|                                    | <ul> <li>VLAN-based packet filtering.</li> </ul>                                                                                                                                                                                                                                                       |

|                                    | <ul> <li>VLAN translation on ingress and egress. VLAN Cross-connect.</li> </ul>                                                                                                                                                                                                                        |

|                                    | Private VLANs.                                                                                                                                                                                                                                                                                         |

|                                    | VLAN counter pool (ingress):                                                                                                                                                                                                                                                                           |

|                                    | - 256 counters in the shared pool.                                                                                                                                                                                                                                                                     |

|                                    | <ul> <li>Indexed by ingress VLAN translation table action.</li> </ul>                                                                                                                                                                                                                                  |

|                                    | - Indexed by VFP action.                                                                                                                                                                                                                                                                               |

|                                    | <ul> <li>VLAN counter pool (egress):</li> </ul>                                                                                                                                                                                                                                                        |

|                                    | <ul> <li>256 counters in the shared pool.</li> </ul>                                                                                                                                                                                                                                                   |

|                                    | Indexed by egress VLAN translation table action.                                                                                                                                                                                                                                                       |

| VLAN Range-Based<br>Double Tagging | <ul> <li>Allows a range of CVIDs to be mapped into the same SPVID without consuming multiple entries in the VLAN<br/>translation table.</li> </ul>                                                                                                                                                     |

| (Matching)                         | <ul> <li>Supports 128 VLAN range profiles.</li> </ul>                                                                                                                                                                                                                                                  |

|                                    | <ul> <li>Each VLAN range profile has a set of eight VLAN ranges configurable by software.</li> </ul>                                                                                                                                                                                                   |

| VLAN Double Tagging                | Support for IEEE 802.1ad provider bridging:                                                                                                                                                                                                                                                            |

|                                    | <ul> <li>Unqualified learning and forwarding.</li> </ul>                                                                                                                                                                                                                                               |

|                                    | Ability to add, remove, and translate (replace) both the service-provider VLAN tag and customer VLAN tag.                                                                                                                                                                                              |

|                                    | <ul> <li>Support for four, programmable outer TPIDs with non-overlapping VLANs.</li> </ul>                                                                                                                                                                                                             |

|                                    | <ul> <li>Support for double tagging requirements of Broadband Forum TR-101.</li> </ul>                                                                                                                                                                                                                 |

|                                    | <ul> <li>Packet forwarding is supported based on:</li> </ul>                                                                                                                                                                                                                                           |

|                                    | <ul> <li>S-VLAN bridging: L2 switch based on MAC_DA and S-VID.</li> </ul>                                                                                                                                                                                                                              |

|                                    | <ul> <li>S-VLAN cross-connect: Destination port is based on S-VID only.</li> </ul>                                                                                                                                                                                                                     |

|                                    | <ul> <li>Double VLAN cross-connect: Destination port is based on (S-VID, C-VID) combination.</li> </ul>                                                                                                                                                                                                |

|                                    | <ul> <li>Support for 2K shared (S-VID, C-VID).</li> </ul>                                                                                                                                                                                                                                              |

| Feature                         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Spanning Tree                   | <ul> <li>Spanning tree support includes the following:</li> <li>128 counters in the shared pool.</li> <li>IEEE 802.1D spanning tree protocol (single spanning tree per port).</li> <li>IEEE 802.1s for multiple spanning trees.</li> <li>IEEE 802.1w rapid spanning tree protocol – delete and/or replace per port, per VLAN.</li> <li>Spanning tree protocol packets detected and sent to the CPU.</li> </ul>                                                                                                                                                                                                                                                                                                                           |

| 32-bit Custom Header<br>support | <ul> <li>32-bit custom header addition after MAC source address in an Ethernet packet (Channelized Flow Control and Forwarding).</li> <li>32-bit custom header removal after MAC source address in an Ethernet packet.</li> <li>32-bit custom header replacement after MAC source address in an Ethernet packet.</li> <li>Custom header based forwarding (channelized forwarding).</li> <li>128 custom headers (1024 with OAM disabled).</li> </ul>                                                                                                                                                                                                                                                                                      |

| L2 Unicast                      | <ul> <li>Supports the following:</li> <li>Learning up to 16K MAC addresses.</li> <li>16K static entries.</li> <li>64 user entries.</li> <li>Line rate switching for all packet sizes.</li> <li>Shared and independent hardware VLAN learning.</li> <li>VLAN flooding for broadcast and DLF packets.</li> <li>Hardware-based address learning.</li> <li>TCAM to learn up to 64 MAC addresses encountering hash collision.</li> <li>Hardware- and software-based aging.</li> <li>Software insertion, deletion, and lookups of the L2 table.</li> <li>Same port bridging supported.</li> <li>Class based learning (station movement control).</li> <li>Supports MAC learn limits per source port (trunk), per VLAN, and per VFI.</li> </ul> |

| L2 Multicast                    | <ul> <li>Supports 1K L2 multicast groups.</li> <li>Line rate switching for all packet sizes.</li> <li>Three port-filtering modes to control multicast packet behavior.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| IGMP snooping                   | <ul> <li>IPv4 IGMP (v1, v2, v3) snooping without tunnels.</li> <li>IPv6 MLD snooping without tunnels.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Provider Backbone<br>Bridging   | <ul> <li>MAC-in-MAC Lite with limited support for initiation and termination of, at most, 64 IEEE 802.1ah compliant MAC-in-MAC tunnels:</li> <li>Parsing MAC-in-MAC.</li> <li>Forwarding decision based on outer MAC header B-SA, B-DA, BVID, ISID in IFP.</li> <li>Configurable backbone service instance tag (EtherType) classification based on I-Tag TCI.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                 |

| Feature                                     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Layer-3 Routing (IPv4,<br>IPv6)             | <ul> <li>IPv4 or IPv6 hosts line rate routing for all packet sizes and conditions. Supports:</li> <li>Up to 512 directly-attached hosts in the L3 table.</li> <li>Up to 64 longest prefix match (LPM) based routing.</li> <li>512 next hops</li> <li>128 Layer-3 interfaces</li> <li>Up to 16 partitions of routing tables (VRF) based on ingress port, VLAN, or flow type.</li> <li>Unicast reverse path forwarding (uRPF) to limit malicious traffic.</li> <li>Software-based aging support.</li> <li>64 ECMP groups.</li> <li>ECMP hash-selection mechanisms:</li> </ul>                                                                                                                                                                                                       |

|                                             | <ul> <li>Legacy hash-selection mechanisms:</li> <li>Legacy hash-selection mechanisms.</li> <li>IP + UDP + BTH header-based hash for Routable RDMA over Converged Ethernet (RRoCE), and also L2 RRoCE.</li> <li>L2 + VXLAN header-based hash for VXLAN-Lite implementation.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| IP Multicast                                | <ul> <li>Up to 128 IPMC groups.</li> <li>Multicast packet replication support for up to 1K VLANs.</li> <li>Line-rate operation for all packet sizes and conditions.</li> <li>Simultaneous L2 bridging and L3 routing.</li> <li>Optional source port and VLAN checks.</li> <li>Lookup: {S, G, V} and {*, G, V}</li> <li>IM-SM, PIM-DM, PIM-SSM, and DVMRP on a per VLAN basis.</li> <li>Reverse path forwarding checks.</li> <li>Ability to fall back to L2 multicast lookup on an IPMC miss.</li> <li>Filter Mode (PFM) per VLAN for L2 multicast, IPv4 multicast, and IPv6 multicast packets.</li> <li>Control trapping of unknown IPMC packets to CPU on a per VLAN per IP type basis.</li> <li>IP multicast address consistency check with destination MAC address.</li> </ul> |

| MAC-IP binding                              | <ul> <li>Hardware support for checking source IP and source MAC address combinations (binding) in IPv4 ARP and<br/>RARP packets.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Tunnel Encapsulation<br>and Deencapsulation | <ul> <li>IP tunnels: VXLAN-Lite.</li> <li>VXLAN-Lite:</li> <li>VTEP – Limited end-point support for, at most, 128 VXLAN tunnels (VFIs).</li> <li>VXLAN transit: parsing of VXLAN header-based limited ACL and QoS support and ECMP-based load balancing of VXLAN packets passing through the switch.</li> <li>ACL and QoS using IFP.</li> <li>Multiple MAC addresses mapping to one VFI.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                               |

| Feature                                                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ContentAware™<br>Processing (Ingress<br>Field Processor) | <ul> <li>1K Single-wide rules.</li> <li>Layer 2 through 7 packet classification.</li> <li>Intelligent protocol-aware processor with backward compatible byte-based classification option.</li> <li>Parses up to 128 bytes per packet. Multiple lookups per packet. Supports: <ul> <li>Multiple matches and actions per packet.</li> <li>ACL-based policing.</li> <li>Ingress port-based filtering.</li> <li>MAC destination address remarking.</li> <li>Class-based marking for SLAs.</li> <li>Traffic-class definition based on the filter.</li> <li>Classification of different packet formats (IPv6, IPv4, double tagged, HTLS, IEEE 802.1Q, Ether II, IEEE 802.3).</li> </ul> </li> <li>Hierarchical min/max programmable meters allows policing of flows.</li> <li>Dual-leaky bucket meters support two-rate three-color marking. srTCM, trTCM, and modified trTCM (RFC2697, RFC2698, RFC4115).</li> <li>Metering support on ingress ports and CPU queues.</li> <li>Jumbo packet metering.</li> <li>TCP and UDP port number range checking.</li> <li>IPv6 filtering (128 bits).</li> <li>Filtering IP packets with options.</li> <li>Modified srTCM support in ingress field processor (IFP) meters (consume green + yellow tokens for frames marked yellow). Also known as TSN metering.</li> <li>Minimum 250 b/s service metering granularity.</li> </ul> |

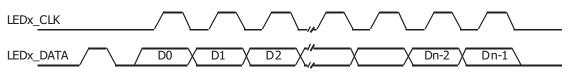

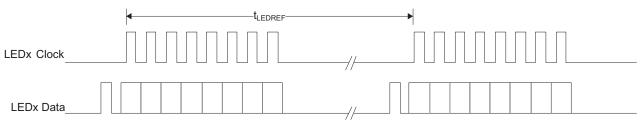

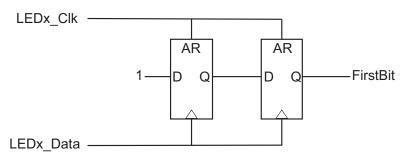

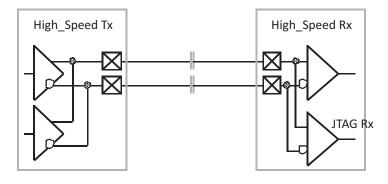

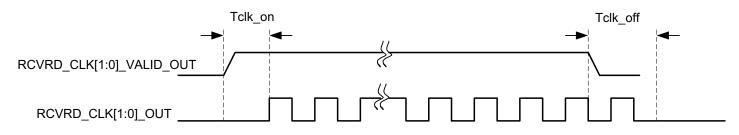

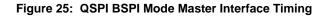

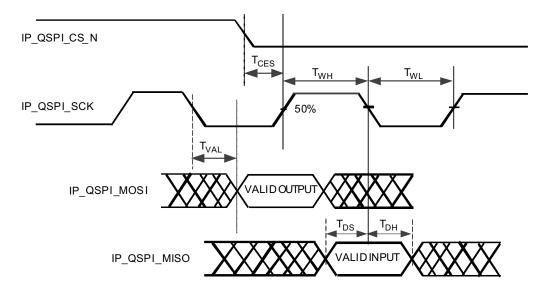

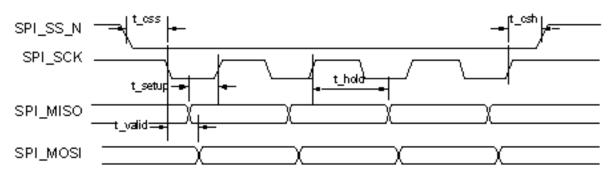

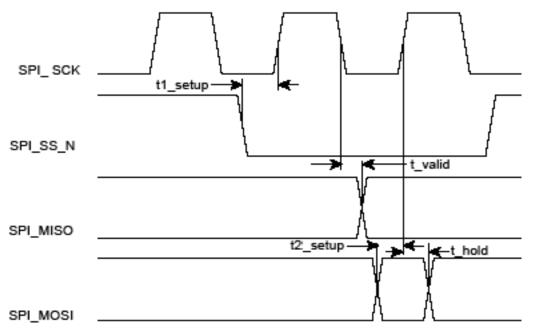

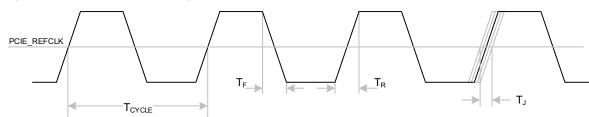

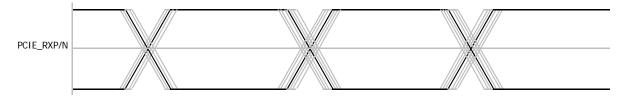

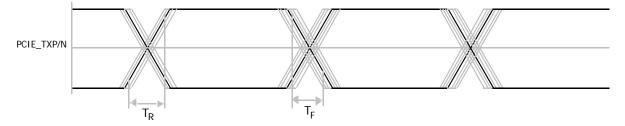

| VLAN Field Processor<br>(VFP)                            | <ul> <li>256 single-wide rules.</li> <li>Flexible VLAN assignment, for untagged and tagged packets, based on L2 through L4 field processing.</li> <li>Q-in-Q feature capability includes modifications to fields within inner or outer tags.</li> <li>Single-wide, or double-wide modes.</li> <li>Field selectors on per-port, per-slice, and per-packet-type basis.</li> <li>Ability to add or replace VLAN tag, change priority, assign classification-ID, or drop.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |