#

# BCM16K Knowledge-Based Processor

### **General Description**

The BCM16K Knowledge-Based Processor (KBP) performs highspeed operations on large-rule databases for a wide range of telecommunications applications, including data center switches and Enterprise routers. It provides network awareness and enables real-time modifications and updates to the routing configuration, making it ideal for packet classification, policy enforcement, and forwarding.

This family of processors addresses next-generation classification requirements through high-performance parallel decisions and improved entry storage capabilities. Parallel operations allow the device to reach decision speeds of multiple billion decisions per second (BDPS). Embedded error correction circuitry (ECC) improves system testability and operational reliability. The key processing unit (KPU) and the context buffer (CB) enable efficient interface transfers with flexible search key construction.

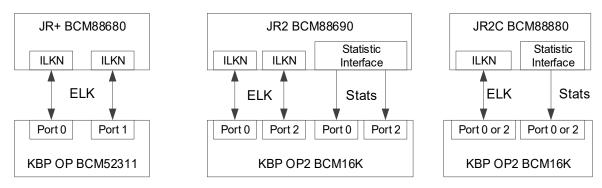

This device seamlessly connects to Jercicho 2C+ BCM88850, Jericho 2C BCM88800, Qumran 2C, Jericho 2 BCM88690, Jericho+ BCM88680, and Jericho BCM88670.

### Features

- Dual host enables two host devices to connect to one device.

- Database records 40b: 2048k/1024k.

- Table width configurable as 80/160/320/480/640 bits.

- User Data Array for associated data, width configurable as 32/ 64/128/256 bits.

- Context Buffer for storing master search keys.

- Up to sixteen parallel searches.

- Simultaneous Multithreading (SMT) operation up to four threads.

- NetRoute forwarding solution for Longest Prefix Match (LPM).

- NetACL solution for Access Control Lists (ACL).

- Logical Tables provide support for intelligent database management (LTR).

- Key Processing Unit (KPU) for flexible search key construction.

- Statistics and counters.

- Result Buffer provides programmability for flexible routing of search results.

- Range Matching for efficient storage utilization.

- ECC on User Data and Database Array. Parity protection on all embedded memories.

- Background ECC scan for database entries with provision for 2-bit anywhere and 4-bit continuous error detection.

- Forward Error Correction (FEC) when using PAM-4 signaling.

- PCI Express (PCIe) lane.

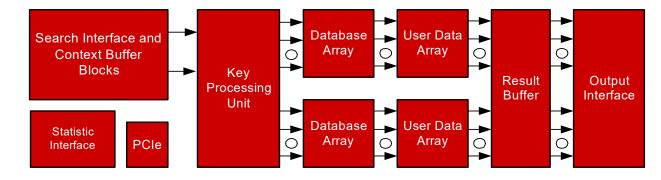

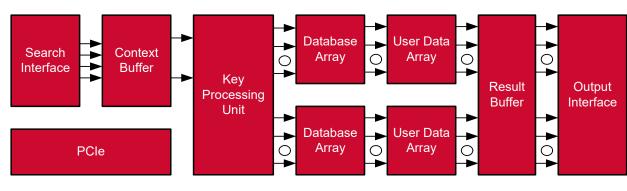

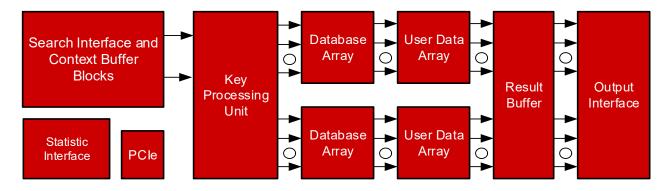

#### Figure 1: Functional Block Diagram

| Chap | pter 1: About This Document            |    |

|------|----------------------------------------|----|

| 1.1  | Purpose and Audience                   | 8  |

| 1.2  | 2 Acronyms and Abbreviations           | 8  |

| 1.3  | References                             | 8  |

| Chap | pter 2: Introduction                   | 9  |

| 2.1  | Overview                               | 9  |

| 2.2  | Peatures                               | 9  |

|      | 2.2.1 General Features                 | 9  |

|      | 2.2.2 Electrical Features              | 10 |

| 2.3  | Applications                           |    |

| 2.4  | Device Architecture Overview           | 11 |

|      | 2.4.1 Context Buffer                   | 11 |

|      | 2.4.2 Key Processing Unit              | 11 |

|      | 2.4.3 Database Array                   | 12 |

|      | 2.4.4 User Data Array                  | 12 |

|      | 2.4.5 Result Buffer                    | 12 |

|      | 2.4.6 PCIe Interface                   | 12 |

|      | 2.4.7 Search Data Flow                 | 13 |

| Chap | pter 3: Context Buffer                 |    |

| 3.1  | Overview                               | 14 |

| 3.2  | 2 Context Buffer Key Transfer to KPU   | 15 |

| 3.3  | Context Buffer Addressing              | 16 |

| 3.4  | Context Buffer Update                  |    |

| Chap | pter 4: Key Processing Unit            |    |

| 4.1  | Overview                               |    |

| 4.2  | 2 Key Processing Unit Byte Parsing     | 21 |

| Char | pter 5: Range Matching                 |    |

|      | Overview                               |    |

|      | Range Matching Implementation          |    |

|      | Naming Convention                      |    |

| 5.4  | Considerations                         |    |

| 5.5  | Range Encoding Data Flow               | 24 |

| 5.6  | Encoded Range Fields                   | 25 |

| Char | pter 6: Database Architecture Overview |    |

|      | Database Entry                         |    |

|      | 2 Block Description                    |    |

|      | 6.2.1 Superblock                       |    |

|      |                                        |    |

|      | 6.2.2 Block and Superblock Relationship                                    |    |

|------|----------------------------------------------------------------------------|----|

|      | 6.2.2.1 Number of Records per Width                                        | 28 |

| 6.3  | B Error Detection and Correction                                           | 29 |

|      | 6.3.1 Database Soft Error Detection and Correction                         | 29 |

|      | 6.3.2 Context Buffer Soft Error Detection                                  | 29 |

| Chap | pter 7: User Data Array                                                    | 30 |

| 7.1  | Overview                                                                   |    |

| 7.2  | Preatures                                                                  | 30 |

| 7.3  | UDA Read/Write Accesses                                                    | 31 |

| 7.4  | UDA Organization for Associated Data                                       | 31 |

| 7.5  | 5 Database to UDA Referencing                                              | 32 |

|      | 7.5.1 UDA Base Address Translation                                         | 33 |

|      | 7.5.2 Associated Data Response Formats                                     | 36 |

|      | 7.5.2.1 Example HPM Index and Associated Data                              | 36 |

|      | 7.5.2.2 Example Associated Data Only                                       |    |

|      | 7.5.2.3 Example HPM Index and Associated Data                              |    |

|      | 7.5.3 Example HPM Index or Associated Data                                 |    |

| Chap | pter 8: Simultaneous Multithreading (SMT)                                  | 39 |

| 8.1  | Overview                                                                   |    |

| 8.2  | 2 Simultaneous Multithread Mode                                            |    |

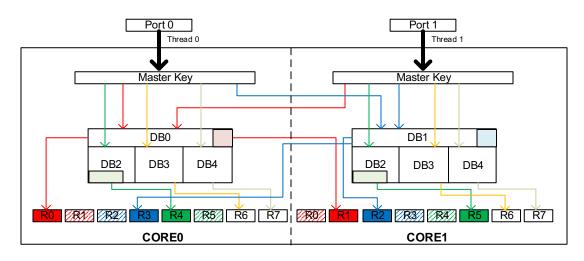

|      | 8.2.1 Assignment of Resources in SMT Mode                                  | 40 |

|      | 8.2.2 Database Array Bank Boundaries                                       | 41 |

|      | 8.2.3 UDA Bank Boundaries                                                  | 41 |

| Chap | pter 9: Pin Descriptions                                                   |    |

| 9.1  | Overview                                                                   | 42 |

| 9.2  | Pin Descriptions                                                           | 43 |

| Char | pter 10: Statistics and Counters                                           |    |

|      | 1 Overview                                                                 |    |

| -    | 10.1.1 General Features                                                    |    |

|      | 10.1.2 Statistics/Counters Tables Specifications                           |    |

|      | 10.1.3 Independent Statistics Records Specifications for Broadcom Switches |    |

|      | 10.1.4 Statistic Interface                                                 |    |

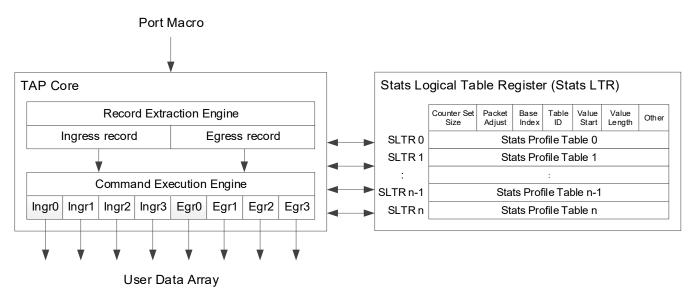

|      | 10.1.5 TAP Core and Stats Logical Table Register (Stats LTR)               | 51 |

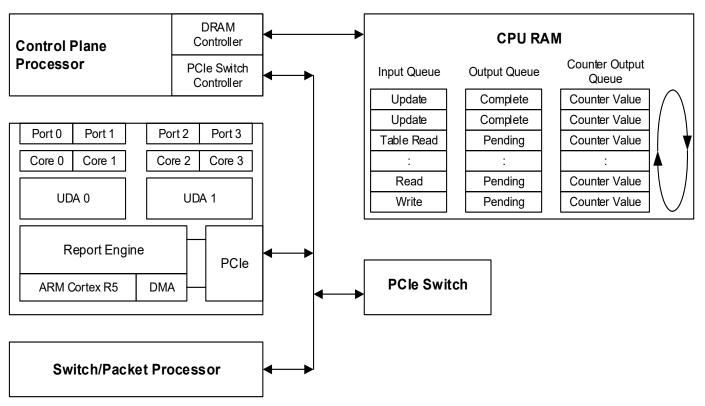

| 10.  | .2 Report Engine                                                           | 52 |

| 10.  | 3 Data Structure in PCI Control Plane Memory                               | 54 |

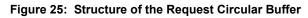

|      | 10.3.1 Request Data Structure                                              | 54 |

|      | 10.3.2 Response Data Structure                                             | 54 |

|      | 10.3.3 Counter Event Data Structure                                        |    |

| 10.  | .4 DMA Message Format                                                      | 56 |

|      |                                                                            |    |

| Chapter 11: Statistics Record                                              | 58 |

|----------------------------------------------------------------------------|----|

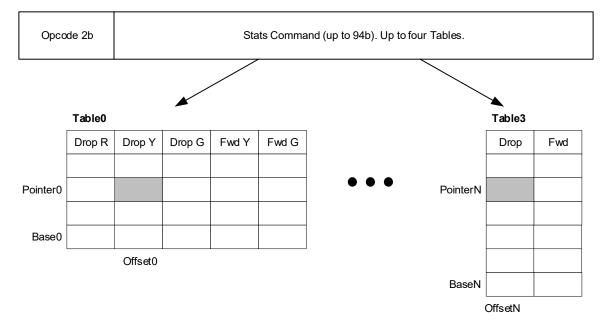

| 11.1 Statistics Command                                                    | 58 |

| 11.2 Stats Record Structure                                                | 60 |

| 11.3 Stats Record Format Examples                                          | 62 |

| Chapter 12: Ethernet Packet Format                                         | 63 |

| 12.1 Standard and Stats Processor Ethernet Packet Format                   | 63 |

| Chapter 13: NetRoute and NetACL                                            | 65 |

| 13.1 Overview                                                              | 65 |

| 13.2 Features                                                              | 65 |

| Chapter 14: Configuration Examples: Jericho 2, Jericho 2C, and Jericho 2C+ | 66 |

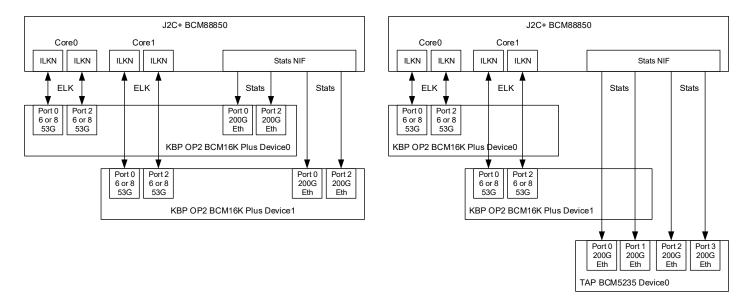

| 14.1 ELK SerDes Connectivity Options for J2C+ BCM88850                     |    |

| 14.2 Excerpt from J2C+ Data Sheet on Statistics                            | 68 |

| Chapter 15: Power Control                                                  | 73 |

| 15.1 Overview                                                              |    |

| 15.2 Usage                                                                 | 73 |

| Chapter 16: Interlaken-LA Instruction Descriptions                         | 74 |

| 16.1 Overview                                                              | 74 |

| 16.2 Interlaken Look-Aside Descriptor Formats                              | 74 |

| 16.2.1 Example of Interlaken-LA Instruction                                | 74 |

| 16.2.1.1 Control Word                                                      | 74 |

| 16.2.1.2 Data Words                                                        | 74 |

| 16.2.2 Interlaken-LA Control Word Format for Request and Response Packets  | 75 |

| 16.2.3 Interlaken-LA Data Word Format for Request and Response Packets     | 77 |

| 16.3 OpCode Definitions                                                    |    |

| 16.4 Non-Network Byte Ordering Within Data Words                           | 77 |

| 16.5 Data Word to Context Buffer Mapping—Non-Network Byte Ordering         |    |

| 16.6 Network Byte Ordering Within Data Words                               |    |

| 16.7 Data Word to Context Buffer Mapping—Network Byte Ordering             |    |

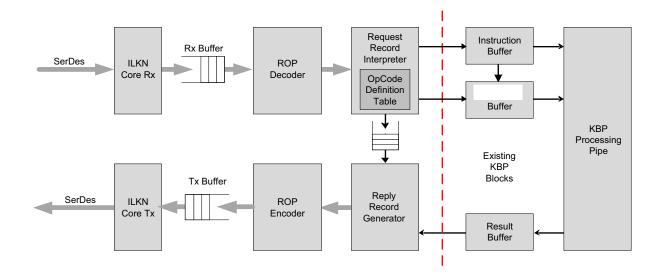

| Chapter 17: ROP Layer and Interlaken Controller                            |    |

| 17.1 General Overview                                                      |    |

| 17.2 Interlaken Controller Overview                                        |    |

| 17.2.1 Interlaken Controller Feature Set                                   |    |

| 17.2.1.1 Interlaken Controller Performance                                 |    |

| 17.2.1.2 Interlaken Descriptor Formats                                     |    |

| 17.2.1.2.1 Example of Interlaken Instruction                               |    |

| 17.2.1.2.3 Data Words                                                      |    |

| 17.2.1.2.4 Interlaken Control Word Format for Request and Response Packets |    |

| 17.2.1.2.5 Interlaken Data Word Format for Request and Response Packets    | 95 |

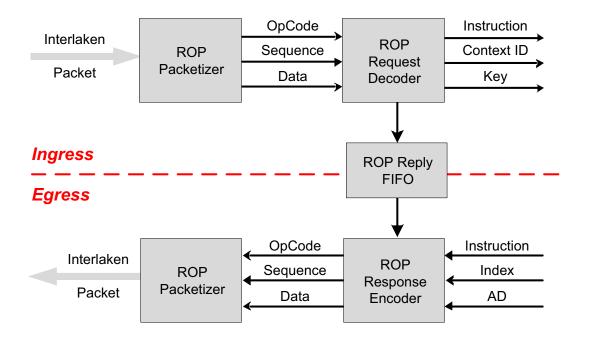

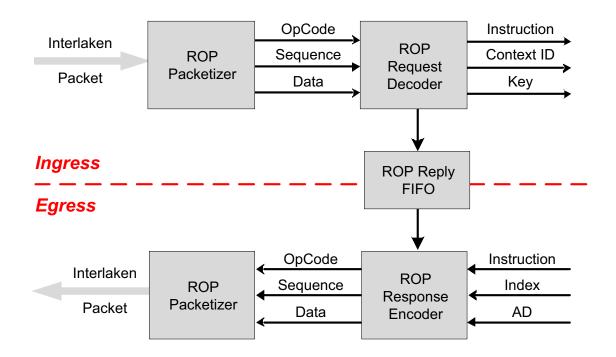

| 17.3 ROP Layer Overview                                                    | 96 |

| 17.3.1 ROP Layer Performance                                                                      |     |

|---------------------------------------------------------------------------------------------------|-----|

| 17.3.2 ROP Ingress and Egress Flow                                                                |     |

| 17.3.2.1 ROP Request Decoder Lookup Table (LUT)                                                   |     |

| 17.3.2.2 ROP OpCodes                                                                              |     |

| 17.3.2.3 Instruction Set Definitions                                                              |     |

| 17.4 Instruction Formats                                                                          |     |

| 17.4.1 CMP Instruction                                                                            |     |

| 17.4.2 CMP Response Format                                                                        |     |

| 17.4.3 ERROR Record                                                                               |     |

| 17.4.4 ROP Egress Flow                                                                            |     |

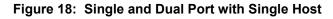

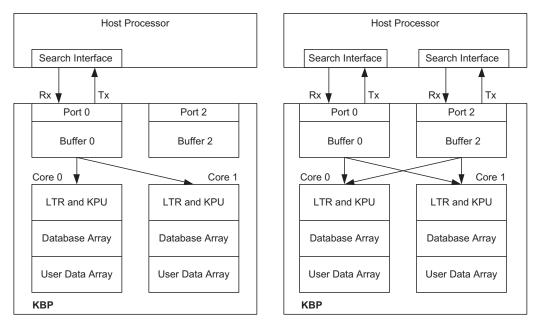

| Chapter 18: Single and Dual-Host Mode                                                             | 106 |

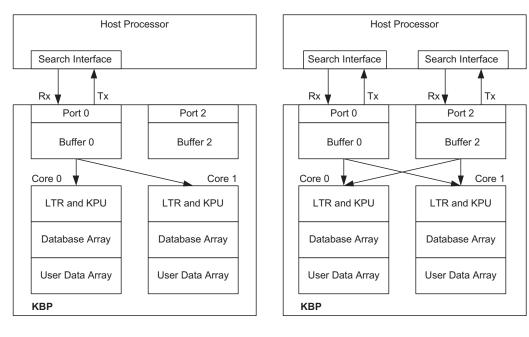

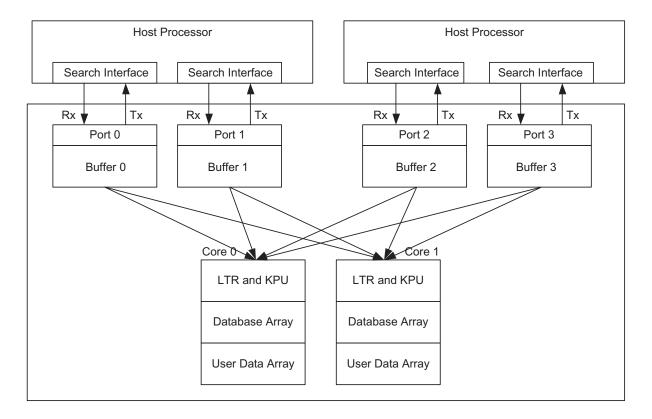

| 18.1 Overview                                                                                     |     |

| 18.2 Dual-Port Mode                                                                               |     |

| 18.3 Search Lane Assignments in Single-Host Mode                                                  |     |

| 18.4 Interface Feature Summary                                                                    |     |

| 18.5 Interlaken FEC                                                                               |     |

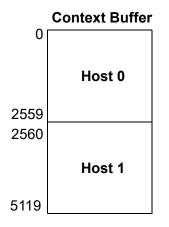

| 18.6 Context Buffer Organization in Dual Host Mode                                                | 110 |

| 18.7 Overlapping Contexts in Dual-Port Mode                                                       | 112 |

| Chapter 19: Device Configuration                                                                  | 113 |

| 19.1 Overview                                                                                     |     |

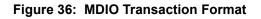

| 19.2 MDIO Physical Interface                                                                      |     |

| 19.2.1 MDIO Address Transaction                                                                   |     |

| 19.2.2 MDIO Write Transaction                                                                     |     |

| 19.2.3 MDIO Read Transaction                                                                      | 114 |

| Chapter 20: Device Usage Restrictions                                                             | 115 |

| 20.1 Overview                                                                                     |     |

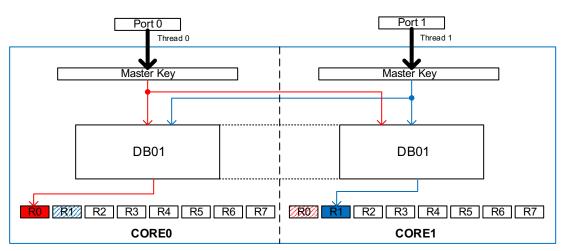

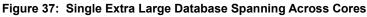

| 20.2 Single Database Spanning Across the Cores                                                    |     |

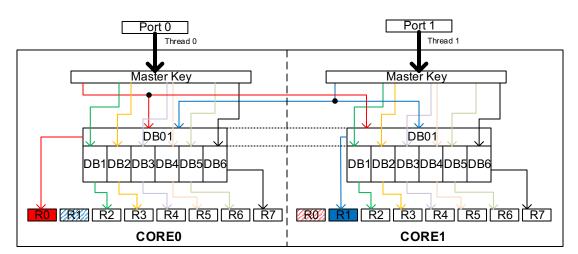

| 20.3 Single Database Residing On One Core, But Accessed From Two Parallel Threads                 |     |

| 20.4 Effect of Search 'N Count on Number of Possible Searches When Any Database is Sha<br>Threads |     |

| 20.5 Result Port Allocation Restriction when a Shared Database is Present                         |     |

| 20.6 STATS Interface Restriction                                                                  |     |

| Chapter 21: PCIe Interface                                                                        | 120 |

| 21.1 Introduction                                                                                 |     |

| 21.2 PCIe Features                                                                                |     |

| 21.3 Theory of Operation                                                                          |     |

| 21.3.1 PCIe Configuration Space Access                                                            |     |

| 21.3.2 DMA Descriptor Structures                                                                  |     |

| 21.4 PCIe Interrupts                                                                              |     |

| 21.4.1 Interrupt Setup                                        | 122 |

|---------------------------------------------------------------|-----|

| 21.4.2 Configuring PCIe                                       | 122 |

| Chapter 22: Device Initialization and Power-Up/Down Sequence  |     |

| 22.1 Device Initialization                                    |     |

| 22.2 Power-Up Sequence                                        |     |

| 22.3 Power-Down Sequence                                      | 123 |

| Chapter 23: LMax                                              |     |

| 23.1 Overview                                                 |     |

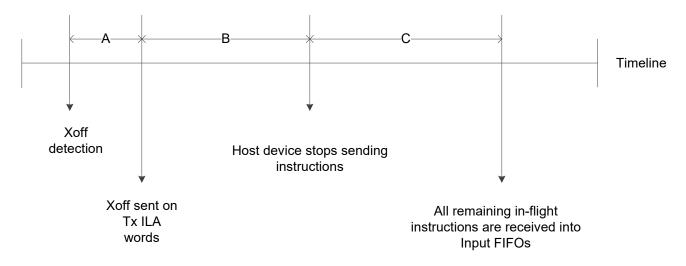

| 23.2 Input FIFO Architecture                                  |     |

| 23.3 Calculating System LMax Requirements                     | 125 |

| Chapter 24: Latency                                           |     |

| Chapter 25: JTAG Boundary Scan                                |     |

| 25.1 JTAG Boundary Scan Overview                              |     |

| 25.1.1 JTAG Boundary Scan Uses 1.8V CMOS I/O Signaling        |     |

| 25.1.2 Disabling JTAG                                         |     |

| 25.1.3 Resetting the TAP Controller                           |     |

| 25.1.4 JTAG Boundary Scan Registers                           |     |

| 25.1.4.1 Instruction Register                                 |     |

| 25.1.4.2 Boundary Scan Register                               |     |

| 25.1.4.3 Identification Register                              | 129 |

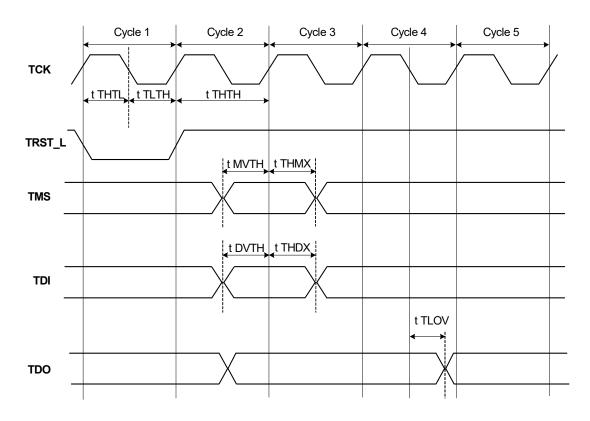

| 25.1.5 JTAG Timing Diagram and AC-Timing Parameters           | 130 |

| Chapter 26: Electrical Specifications                         |     |

| 26.1 Overview                                                 |     |

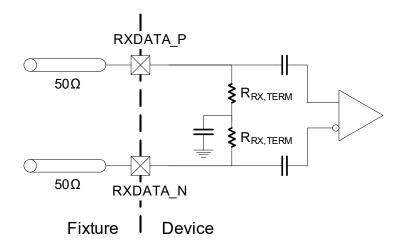

| 26.1.1 Receiver                                               |     |

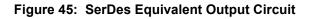

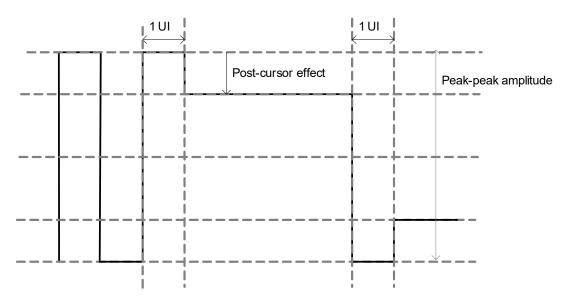

| 26.1.2 Transmitter                                            |     |

| 26.2 Absolute Maximum Ratings                                 |     |

| 26.3 Recommended Operating Conditions                         | 134 |

| 26.4 Electrical Specifications                                |     |

| 26.5 DC Electrical Specifications                             | 136 |

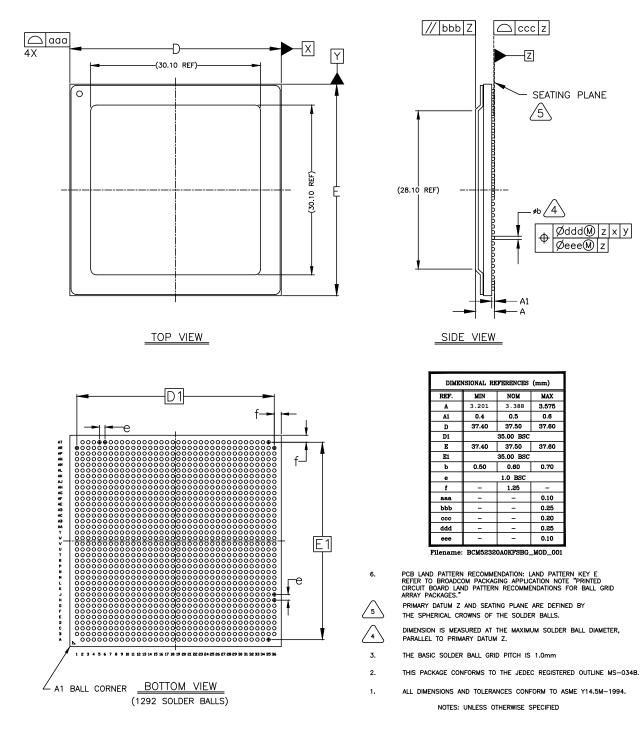

| Chapter 27: Mechanical Specifications                         |     |

| 27.1 Package Specifications                                   |     |

| 27.1.1 Package Notes                                          |     |

| 27.2 Package Thermal Characteristics                          | 138 |

| Chapter 28: Ball Assignment                                   |     |

| 28.1 Ball Assignment by Location                              |     |

| Chapter 29: Summary of BCM15K/BCM52311 and BCM16K Differences |     |

| 29.1 Summary of Differences                                   |     |

| Chapter 30: Errata and Device Status                          |     |

|                                                               |     |

| 30.1 KBP SDK for B0                                                                         | 148 |

|---------------------------------------------------------------------------------------------|-----|

| 30.2 Switching MDIO Access from Pins to PCIe                                                | 148 |

| 30.3 A0 Silicon 56G Link-Training and Tracking is Sub-Optimal across Full Temperature Range | 149 |

| 30.4 PCI Configuration Space STATUS Register Access                                         | 149 |

| Chapter 31: Ordering Information                                                            | 150 |

| 31.1 Part Number Decoding                                                                   | 150 |

| Appendix A: Acronyms and Abbreviations                                                      | 152 |

| Revision History                                                                            | 153 |

# **Chapter 1: About This Document**

# 1.1 Purpose and Audience

The processor performs high-speed operations on large-rule databases for a wide range of telecommunications applications including WAN, MAN, and Enterprise switches and routers. It provides network awareness and enables real-time modifications and updates to the routing configuration, making it ideal for packet classification, policy enforcement, and forwarding.

This document is intended for software, hardware, and application engineers.

# 1.2 Acronyms and Abbreviations

In most cases, acronyms and abbreviations are defined on first use.

Acronyms and abbreviations in this document are also defined in Appendix A: "Acronyms and Abbreviations," on page 152.

For a comprehensive list of acronyms and other terms used in Broadcom documents, go to: <u>http://www.broadcom.com/press/glossary.php</u>.

# 1.3 References

The references in this section may be used in conjunction with this document.

For Broadcom documents, replace the "xx" in the document number with the largest number available in the repository to ensure that you have the most current version of the document.

| Document (or Item) Name |                                | Number            | Source       |  |

|-------------------------|--------------------------------|-------------------|--------------|--|

| Broa                    | Broadcom Items                 |                   |              |  |

| [1]                     | KBP SDK Reference Manual       | KBP-SDK-SWUM1xx-R | Broadcom CSP |  |

| [2]                     | BCM16K Board Design Guidelines | 16000-DG1Xx       | Broadcom CSP |  |

# **Chapter 2: Introduction**

# 2.1 Overview

This family of processors addresses next-generation classification needs through high-performance parallel decisions and improved entry storage capabilities. Parallel operations allow the device to reach decision speeds of multiple Billion Decisions Per Second (BDPS). Embedded Error Correction Circuitry (ECC) improves system testability and operational reliability. The key processing unit (KPU) and the context buffer (CB) enable efficient interface transfers with flexible search key construction.

This knowledge-based processor seamlessly connects to Jercicho 2C+ BCM88850, Jericho 2C BCM88800, Qumran 2C, Jericho 2 BCM88690, Jericho+ BCM88680, and Jericho BCM88670.

# 2.2 Features

### 2.2.1 General Features

- Dual host enables two host devices to connect to one device.

- Database records 40b: 2048k/1024k.

- Tables width configurable as 80/160/320/480/640 bits.

- User Data Array for associated data, width configurable as 32/64/128/256 bits.

- Dual core DBA/UDA architecture.

- Context Buffer for storing master search keys.

- Up to sixteen parallel searches.

- Simultaneous Multithreading (SMT) operation up to four threads (one per port) for search applications.

- Implements the NetRoute forwarding solution for Longest Prefix Match (LPM).

- NetACL solution for access control list.

- Logical Tables provide support for intelligent database management.

- Key Processing Unit (KPU) for flexible search key construction.

- Result Buffer provides programmable interconnect for flexible routing of search results.

- Range Matching for efficient storage utilization.

- ECC protection for User Data and Database Array. Parity protection on all embedded memories.

- Background ECC scan for database entries.

- Forward Error Correction (FEC) when using PAM-4 signaling.

### 2.2.2 Electrical Features

- Core clock operating frequency 1000 MHz.

- 32 RX and TX Serial Lanes up to 56.25 Gb/s (PAM-4) for search:

- In single-host single-port mode, a maximum 16 lanes for search.

- In single-host dual-port mode, a maximum 16 lanes per port for search.

- In dual-host quad-port mode, a maximum of 8 lanes per port for search.

- All search ports must operate at the same SerDes rate

- 16 RX and TX Serial Lanes up to 53.125 Gb/s (PAM-4) for statistics:

- Four lanes per port for statistics.

- All statistics ports must operate at the same SerDes rate.

- Miscellaneous CMOS I/Os at 1.8V.

- Core Supply 0.850V controlled through AVS.

- Package 37.5 mm x 37.5 mm FCBGA.

# 2.3 Applications

The processor can be used in many applications, including;

- IPv4 and IPv6 Packet Classification

- Access Control Lists

- Policy-based Routing and QoS

- IPv4 and IPv6 Longest Prefix Match

- Flow-based Access Control Lists

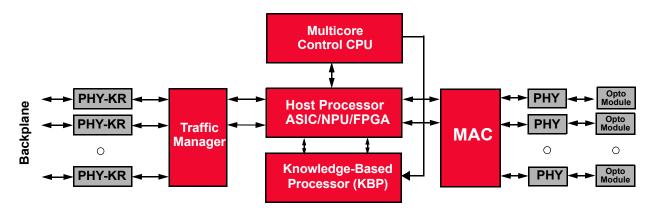

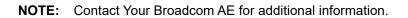

Figure 2 shows a typical line-card application.

### Figure 2: Line Card

# 2.4 Device Architecture Overview

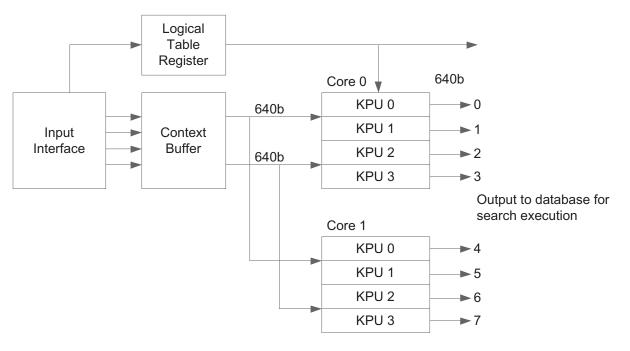

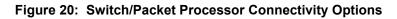

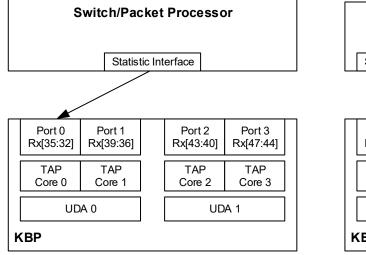

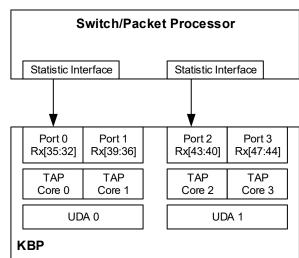

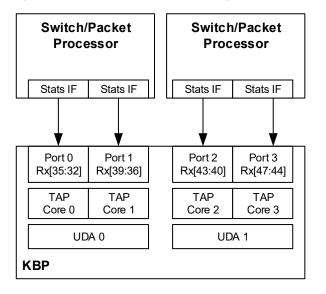

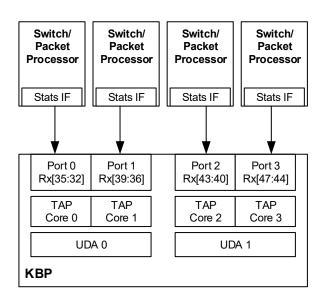

Figure 3 and Figure 4 shows a block diagram of the processor. The main blocks are described in the following subsections.

Figure 4: Functional Block Diagram (with Broadcom Switch)

# 2.4.1 Context Buffer

The context buffer is for loading and storing master search keys from the host processor. All data written from the host processor is stored in the context buffer until overwritten.

See Chapter 3, Context Buffer for additional information.

# 2.4.2 Key Processing Unit

The key processing unit provides user flexibility in generating search keys for the various search profiles (logical tables) through key manipulation and preprocessing. The key processing unit offers the ability for users to create unique keys for each search operation issued per a compare instruction.

See Chapter 4, Key Processing Unit for additional information.

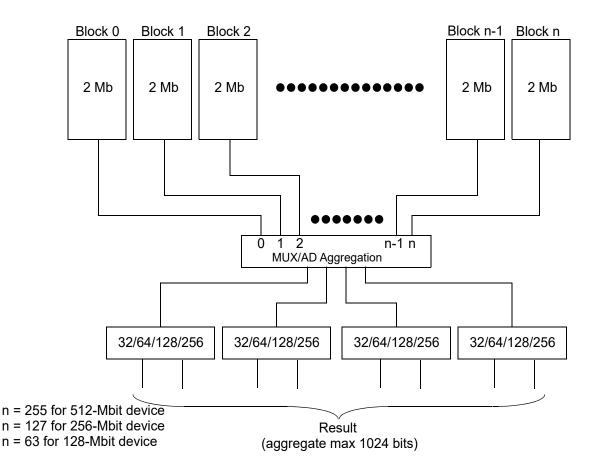

### 2.4.3 Database Array

Each database record is composed of 80 X-Y values, one X-Y pair for each bit in the entry. When writing to the processor, users can choose to write in Data Word/Mask Word format or in the X-Y format.

See Chapter 6, Database Architecture Overview for additional information.

### 2.4.4 User Data Array

The User Data Array (UDA) is a RAM subsystem. The UDA is a shared storage resource with a capacity of 512 Mb per core. The resource consists of 2 x 256 blocks capable of multiple core parallel accesses per clock cycle. ECC protection is provided with 1-bit correct and 2-bit detect.

See Chapter 7, User Data Array for additional information.

### 2.4.5 Result Buffer

The highest priority match response is sent to the Output Interface for transmission. Result Buffer also allows for post processing of AD (truncating, shifting and padding).

### 2.4.6 PCIe Interface

The processor has a PCIe 2 port configured for one lane enabling direct connection to control plane. All device functions are supported including device initialization, PIO read/write, table updates, and searches. Multi-channel TX DMA exports statistics and counter data. Multi-channel exports the RX DMA to the control plane processor for updates.

See Chapter 19, Device Configuration for additional details.

### 2.4.7 Search Data Flow

The processor is designed to offer maximum flexibility for the user to create and apply search keys, resolve search results from database blocks, access user data memory, and output the results.

The processor provides a context buffer for loading and storing a "master search key." The context buffer is followed by the key processing units, which can generate up to eight per core unique keys, up to 640b in width, from the master search key. The KPU output can be further modified by inserting up to two range information. The range hardware is programmable. The programmable interconnect maps the keys generated by the KPUs to superblocks containing the database entries.

On the result side, a programmable interconnect is available to provide flexible routing and priority encoding of search results. All blocks directed toward the same result output (same parallel search) are used in the determination of the highest priority match (HPM) for that output. The programmable result interconnect allows for the results from the database blocks to be mapped to any one of eight result outputs. This results in a mesh structure between block results to eight per core output slots. These eight per core results can then be sent to the result buffer to be output through the interface or can be used to index the user data memory. The search results and user data can then be sent to the result buffer for output.

# **Chapter 3: Context Buffer**

# 3.1 Overview

The context buffer is for loading and storing master search keys from the host processor. All data written from the host processor is stored in the context buffer until overwritten.

The context buffer is used to store search keys from current or previous instructions for later modification and reissue for flexible multithreaded search key management. During a compare operation, the processor sends 640 bits of search key from the context buffer to the Key Processing Unit (KPU) to be transformed into the search keys to be presented to the database. The 640-bit context is selected by the context buffer address provided in the Interlaken Look-Aside control word during the compare operations.

The context buffer is designed for a multithreaded environment with key persistence. The user can write to any context buffer location at any time. For example, the user can write to address location 20 in one cycle and address location 9 in the next cycle.

#### Figure 5: Context Buffer and Key Processing Unit Block Diagram

# 3.2 Context Buffer Key Transfer to KPU

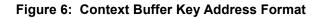

The Context Buffer address (ContextAddr[15:0]) provided in the control word dictates the storage location of the data inside the context buffer. Each address points to an 80b entry in the context buffer, as shown in Figure 6.

The context buffer address decoder ignores the least significant three bits of the context buffer address when selecting the 640b of data to be transferred to the key processing unit. For example, if a user executes a compare instruction at Context Address location 11, then the search key data transferred to the KPU come from Context Address locations 8, 9, 10, 11, 12, 13, 14, and 15. Address location 8 will have LSB 80 bits of the 640-bit key. In 320b context configuration, the context buffer address decoder ignores the least significant two bits of the context buffer address when selecting the 320b of data to be transferred to the key processing unit (on the [319:0] bits).

### 3.3 Context Buffer Addressing

The context buffer is written in multiples of 80b. The number of 80b context buffer locations that are written is determined by the width of the new search key transferred during either compare operations or context buffer write operations. The relationship is as follows:

$n = \left\lceil \frac{s}{(80)} \right\rceil$ , n = number of 80b context buffer locations written, s = width of the new search key in bits

For example:

- If 80b of the new search key is transferred, then one 80b context buffer entry is updated.

- If 240b of the new search key is transferred, then three 80b context buffer entries are updated.

- If 384b of the new search key is transferred, then five 80b context buffer entries are updated.

If the width of the new search key is not divisible by 80, as shown in the last example, the remaining bits are filled with "don't care" values. In this scenario, the placement of the search "don't care" values in the context buffer is determined by whether the device is configured for network byte ordering (NBO) or non-network byte ordering (NNBO). If the device is in NBO mode, the "don't care" values are written in the LSB. If the device is in NNBO mode, the "don't care" values are written in the MSB. See "Data Word to Context Buffer Mapping—Non-Network Byte Ordering" and "Data Word to Context Buffer Mapping—Network Byte Ordering" for details.

These random bits must be properly masked using Block Mask Registers or local masks in each database entry.

The context buffer is protected by parity. The instruction "Context Buffer No Write and Compare" will not overwrite existing data in the context buffer (key persistence) enabling the CPU to send 64b junk data. The parity is checked for the targeted 640b context during a compare operation. The compare operation will not be executed if a context buffer error is detected and the response for the compare operation will be flagged with an Error Status bit being set. See "Context Buffer Soft Error Detection" for details.

The context buffer address dictates the storage location of the least significant 80b of the new search key. If the new search key crosses a 640-bit context buffer boundary, only the 640-bit context location that is referred to by the context buffer address is updated. The portion of the new search key that falls outside of the addressed 640-bit context buffer location is lost and the original data retained.

For Table 1, Data A [x] is new data written into the context buffer and Data B [x] and Data C [x] are existing data in the context buffer.

| Context Buffer Address                                                                 | Context Buffer Address from Command                                                                                                         |                                                                                                                                                                      |                                                                                                                                                                |                                                                                                                                                                                            |

|----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| from Command<br>ContextAddr[15:0]                                                      | If Context Buffer<br>Address = 0x0                                                                                                          | lf Context Buffer<br>Address = 0x2                                                                                                                                   | If Context Buffer<br>Address = 0x5                                                                                                                             | If Context Buffer<br>Address = 0x7                                                                                                                                                         |

| 0x0                                                                                    | A [0] 79:0                                                                                                                                  | B [0] 79:0                                                                                                                                                           | B [0] 79:0                                                                                                                                                     | B [0] 79:0                                                                                                                                                                                 |

| 0x1                                                                                    | A [1] 159:80                                                                                                                                | B [1] 159:80                                                                                                                                                         | B [1] 159:80                                                                                                                                                   | B [1] 159:80                                                                                                                                                                               |

| 0x2                                                                                    | B [2] 239:160                                                                                                                               | A [0] 79:0                                                                                                                                                           | B [2] 239:160                                                                                                                                                  | B [2] 239:160                                                                                                                                                                              |

| 0x3                                                                                    | B [3] 319:240                                                                                                                               | A [1] 159:80                                                                                                                                                         | B [3] 319:240                                                                                                                                                  | B [3] 319:240                                                                                                                                                                              |

| 0x4                                                                                    | B [4] 399:320                                                                                                                               | B [4] 399:320                                                                                                                                                        | B [4] 399:320                                                                                                                                                  | B [4] 399:320                                                                                                                                                                              |

| 0x5                                                                                    | B [5] 479:400                                                                                                                               | B [5] 479:400                                                                                                                                                        | A [0] 79:0                                                                                                                                                     | B [5] 479:400                                                                                                                                                                              |

| 0x6                                                                                    | B [6] 559:480                                                                                                                               | B [6] 559:480                                                                                                                                                        | A [1] 159:80                                                                                                                                                   | B [6] 559:480                                                                                                                                                                              |

| 0x7                                                                                    | B [7] 639:560                                                                                                                               | B [7] 639:560                                                                                                                                                        | B [7] 639:560                                                                                                                                                  | A [0] 79:0                                                                                                                                                                                 |

| 0x8                                                                                    | C [0] 79:0                                                                                                                                  | C [0] 79:0                                                                                                                                                           | C [0] 79:0                                                                                                                                                     | C [0] 79:0                                                                                                                                                                                 |

| Data written to context<br>buffer<br>and<br>Data transferred to key<br>processing unit | Data A [1:0] (160b)<br>written to context buffer<br>Data A [1:0] (160b) and<br>Data B [7:2] (480b)<br>transferred to key<br>processing unit | Data A [1:0] (160b)<br>written to context buffer<br>Data B [1:0] (160b), Data<br>A [1:0] (160b), and Data B<br>[7:4] (320b)<br>transferred to key<br>processing unit | Data A [1:0] (160b)<br>written to context buffer<br>Data B [4:0] (400b), Data<br>A [1:0] (160b), and Data B<br>[7] (80b) transferred to<br>key processing unit | Data A [0] (80b)<br>written to context buffer<br>Data A [1] (80b) NOT<br>written to context buffer<br>Data B [6:0] (560b) and<br>Data A [0] (80b)<br>transferred to key<br>processing unit |

#### Table 1: 160b Context Buffer Write Operation

# 3.4 Context Buffer Update

The Context Buffer address specifies the storage location of the least significant 80b of the new search key. If the new search key crosses a 640-bit Context Buffer boundary, only the 640-bit context location, which is referred to by the Context Buffer address, is updated. The portion of the new search key, which falls outside of the addressed 640-bit Context Buffer location, is lost. In the last example in Table 2, the upper most 80 bits of data, 'S,' is not written to Context Buffer address 0x8.

### Figure 7: Context Buffer Update Example

Context Buffer Address 0x0 Context Buffer Address 0x1 Context Buffer Address 0x2 Context Buffer Address 0x3

#### Table 2: Context Buffer Update Example

| Context Address | New Search Key | Existing Data Within the Addressed<br>640-bit Context | New 640-bit Data Within the<br>Addressed 640-bit Context |

|-----------------|----------------|-------------------------------------------------------|----------------------------------------------------------|

| 0x0             | QP             | HGFEDCBA                                              | HGFEDCQP                                                 |

| 0x1             | QP             | HGFEDCBA                                              | HGFEDQPA                                                 |

| 0x3             | SRQP           | HGFEDCBA                                              | HSRQPCBA                                                 |

| 0x5             | SRQP           | HGFEDCBA                                              | RQPEDCBA                                                 |

# **Chapter 4: Key Processing Unit**

# 4.1 Overview

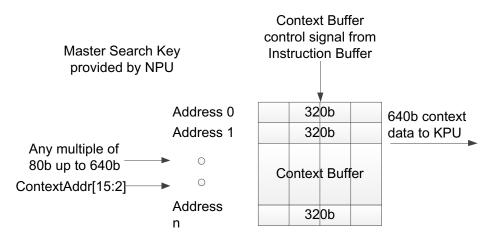

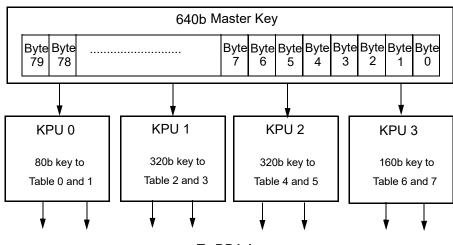

The key processing unit provides user flexibility in generating search keys for the various search profiles (logical tables) through key manipulation and preprocessing. The key processing unit offers the ability for users to create unique keys for each search operation issued per compare instruction. Through register control, the key processing unit assembles eight unique keys up to 640b or four unique key pairs, with each key pair sharing, in unit of 160b, up to 640b of data from the NPU. Byte-level parsing is used across the entire 640b of data.

Up to 15 segments can be used to generate search keys for compare operations. Each KPU gets the 640b master key coming from the NPU in single thread mode, and one of the four 640b master keys coming from the NPU in SMT mode. On the master key, a given KPU can produce one key of up to 640b length and one additional key of up to 320b length. However, as stated above, the combined width of the two keys must not exceed 640b.

The KPU has a Fill-with-Zero feature which, when set, will fill all bytes in a segment with zeros. Enabling Fill-with-Zero for all unused key segments will reduce power consumption.

KPU programming is controlled by the KBP SDK. Contact Broadcom application engineering for further details.

#### Context Database Master Search KPU **Buffer** Array Key from NPU Addr 0 79:0 Addr 0 79:0 79:0 Addr 1 159:80 159:80 159:80 Addr 1 Addr 2 239:160 239:160 239:160 Addr 2 KPU 319:240 319:240 Addr 3 n bits 319:240 Addr 3 Addr 4 399:320 399:320 399:320 Addr 4 479:400 Addr 5 479:400 479:400 Addr 5 Addr 6 559:480 559:480 559:480 Addr 6 Addr 7 639:560 639:560 639:560 Addr 7 Addr n-1 Addr n

### Figure 8: Master Key

The key processing functionality of the key processing unit is preconfigured using registers, and then activated during compare operations with the referenced logical table register. Figure 9 depicts an example of each key processing unit constructing a unique search key from one distinct context.

#### Figure 9: Key Processing Unit Diagram—Example 1

Valid Start\_Byte values range from 0 to 0x4F. If the Start\_Byte fields of all segments are programmed to 0x7F then the search key data is passed through to the database for search operation. Length\_Byte values range from one to 16 with 0 = 1 byte, 1 = 2 bytes, ... 15 = 16 bytes. If the 15 search key segments are greater than 640b, then only the first 640b is used, and the balance of bits of Most Significant bits greater than 640b is ignored. If all 15 segments do not complete 640b in length, then the remaining balance up to 640b is copied from the master search key.

#### Figure 10: Key Processing Unit Diagram for Eight Search Keys

To DBA Array

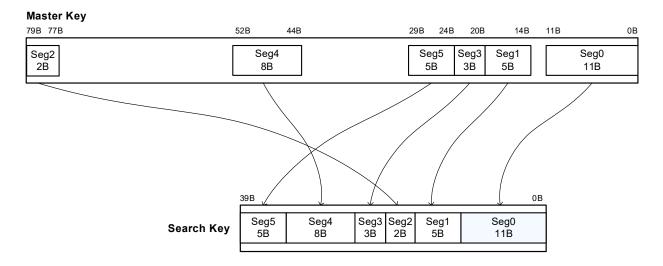

# 4.2 Key Processing Unit Byte Parsing

The key processing unit parses search key data from the master key. The byte-level parsing is defined by register settings in the logical table register. The user specifies the Start\_Byte and the Length\_Byte of each segment. Up to 15 segments can be concatenated to form a search key.

### Figure 11: KPU Byte Parsing

# Chapter 5: Range Matching

# 5.1 Overview

Source and Destination port ranges are often used in Access Control List entries (ACLs) to better identify and process network traffic. However, when the port ranges are translated to ternary values, they often require multiple entries, leading to inefficient use of the database and a reduction in the number of user ACLs that can be stored. The worst case number of entries required to store an n-bit range with prefix encoding is  $(2^n - 2)$ . This inefficiency is compounded when both source and destination port fields include ranges.

Range matching programming is controlled by the KBP SDK. Contact Broadcom application engineering for further details.

# 5.2 Range Matching Implementation

The processor implements range encoding by utilizing unused bits within each database entry to minimize the expansion in the number of database entries required. This effectively doubles the number of user ACEs with port ranges. The encoding algorithm in the processor is flexible and selects a combination of encoding schemes, with the control plane software selecting the optimal encoding for each range set.

In the example shown in Table 3, six entries are required to store a single ACL containing the range 1 to 14; with only the range field changing between entries. The same ACL port range 1 to 14, using range expansion requires only three entries as shown in Table 4. The same data is now contained in half the number of entries, effectively doubling the storage density, with part of the unused width being used for range encoding.

### Table 3: Port Expansion Without Range Matching for Ports 1 to 14

| Destination Address | Source Address | 16b Port                | Ports           |

|---------------------|----------------|-------------------------|-----------------|

| A                   | В              | 16'b0000_0000_0000_0001 | Port 1          |

| A                   | В              | 16'b0000_0000_0000_001* | Ports 2 and 3   |

| A                   | В              | 16'b0000_0000_0000_01** | Ports 4 to 7    |

| A                   | В              | 16'b0000_0000_0000_10** | Ports 8 to 11   |

| A                   | В              | 16'b0000_0000_0000_110* | Ports 12 and 13 |

| A                   | В              | 16'b0000_0000_0000_1110 | Port 14         |

| Destination Address | Source Address | Used by Range Matching Algorithm   | Ports             |

|---------------------|----------------|------------------------------------|-------------------|

| A                   | В              | 32'b0000_0000_0000_0000_0**1_****  | Ports 1, 2, and 3 |

| A                   | В              | 32'b0000_0000_0000_0000*_1***_**** | Ports 4 to 11     |

| A                   | В              | 32'b0000_0000_0000_00011_10**_**** | Ports 12 to 14    |

The processor has range encoding implemented in hardware. Range encoding requires both hardware and software support. The software operates both in the control plane and the data plane to implement range operations. Various internal registers are used by the software to implement the range operations.

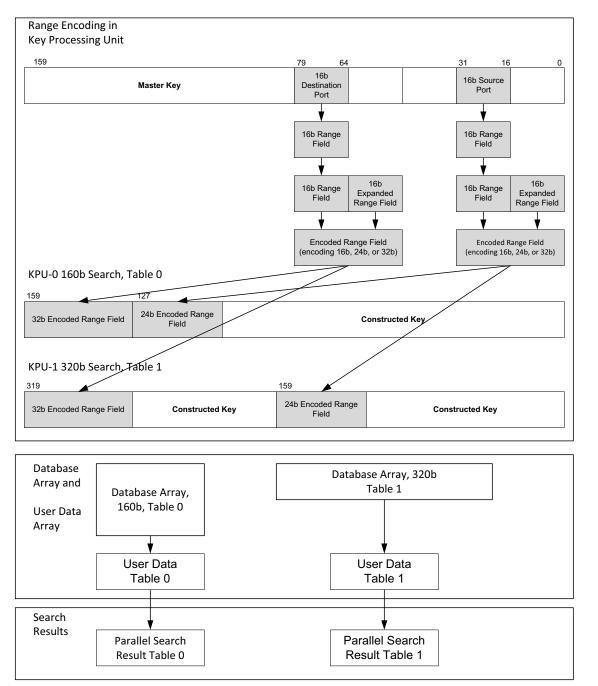

The range encoding can be dynamically applied per LTR. Up to two range fields per search key can be independently selected for range matching, providing efficient range rule compaction. The search profile in the Logical Table register includes range matching registers. See range registers for further details on insertion locations of encoded range fields into parallel search keys and extraction locations of range fields from the master search key.

# 5.3 Naming Convention

Throughout this document, the following naming conventions are used for range matching.

#### Table 5: Naming Conventions

| Name                | Description                                            |  |

|---------------------|--------------------------------------------------------|--|

| Range Encoding      | A form of arithmetic coding; a data compression method |  |

| Range Field         | 16b of the port address requiring range encoding       |  |

| Encoded Range Field | 16b, 24b, or 32b output from the range encoding engine |  |

### 5.4 Considerations

- Range encoding is supported for up to two 16b range fields within master key.

- As shown in Encoded Range Fields, the 16b range fields within master key must start and end on byte boundaries. The device uses all 16-bits of the range field regardless of the number of bits used to classify the port. Potential unused bits in the range field cannot be allocated for other purposes.

- As shown in Encoded Range Fields, encoded range fields can be inserted at any byte location within the constructed key (output of KPU).

- Range insertion per constructed key basis:

- The user specifies the number of bytes of the encoded range field to insert into the constructed key. Two, three, or four byte insertions are allowed. Optimal compression is achieved when all 32b of the encoded range field is inserted. Even with two-byte insertion, the device performs some level of compression.

- The range function is implemented in parallel with the key processing unit (KPU) function. The user must ensure that there is enough room in the constructed search key to insert the encoded range field.

- There can be, at maximum, two ranges (maximum of 32b each) inserted in any constructed key (if 640b contains a key pair, then each key would be able to have two ranges).

- The location of range insertion is programmable. If there are two ranges to be inserted, the second range is inserted after the first one, and the second one occupies higher bit positions than the first one.

- To accommodate the additional bits associated with the encoded range field, the constructed key must provide spare bits, or remove fields from master key, or increase block size.

- The encoded range field insertion location is defined by the LTR with possible locations being 160b, 320b, and/or 640b boundary.

# 5.5 Range Encoding Data Flow

Range Encoding requires both hardware and software support. The software operates both in the control plane and the data plane to implement range operations. Various internal registers are used by the software to implement the range operations.

In the control plane, the Broadcom KBP SDK programs appropriate range values. The KBP SDK has several function calls, including a function call that encodes the 16b Range Field into a 16b, 24b, or 32b encoded range field. The user passes the port ranges to this function, which determines the encoding for most efficient storage. The function returns the range encoded fields to the user to be included in the user's databases.

In the data plane, the user writes the input data, (that is, unencoded master search key) to the buffer. The buffer transfers the data to the KPU and range function. The KPU and range function operate in parallel. The device, using the range function, encodes the selected range field(s) and inserts up to 32b of the encoded range field back into the constructed key.

Figure 12 on page 25 shows a typical sequence where an instruction writes 160b of input data into the context buffer. An instruction such as Write Context Buffer and Compare1 transfers 640b of data from the context buffer to the KPU and range function. In this example, only the least significant 160b of the transfer data is used, the most significant 160b of transfer data is not used, and the database blocks targeted by this instruction must be configured to 160b.

# 5.6 Encoded Range Fields

Figure 12 shows the format of the encoded range fields.

#### Figure 12: Encoded Range Fields per Key

# **Chapter 6: Database Architecture Overview**

# 6.1 Database Entry

Each database record is composed of 80 X-Y values, one X-Y pair for each bit in the entry. When writing to the processor, users can choose to write in the traditional Data Word/Mask Word format or in the X-Y format. Internally, the processor always stores in the encoded, X-Y format. Consequently, database read operations return data in the X-Y format only (a single read operation returns an 'X' value or a 'Y' value, as dictated by the instruction encoding). Table 6 shows the two encoding formats:

#### Table 6: Data/Mask Encoding

| Data | Mask | Data/Mask Description                                                             |  |

|------|------|-----------------------------------------------------------------------------------|--|

| 0    | 0    | Bit matches a '0' only.                                                           |  |

| 0    | 1    | Always hot: bit matches either a '0' or a '1'.<br>Represents an 'X' (don't care). |  |

| 1    | 0    | t matches a '1' only.                                                             |  |

| 1    | 1    | Always hot: bit matches either a '0' or a '1'.<br>Represents an 'X' (don't care). |  |

#### Table 7: X-Y Encoding

| x      | Y       | X-Y Description                                                                         |  |

|--------|---------|-----------------------------------------------------------------------------------------|--|

| 0      | 0       | Always hot: bit matches either a '0' or a '1'.                                          |  |

|        |         | Represents an 'X' (don't care).                                                         |  |

| 0      | 1       | Bit matches a '0' only.                                                                 |  |

| 1      | 0       | Bit matches a '1' only.                                                                 |  |

| 1      | 1       | Always miss: Forces a mismatch for the compare, unless BMR masks off corresponding bit. |  |

| Y = D_ | b AND M | _b                                                                                      |  |

| X = D  | AND M_b |                                                                                         |  |

ECC scan will detect corruption of up to four consecutive bits and two bits anywhere in the 80b word and correct up to 1b error at the time of the ECC scan. The ECC code is extended to 11 bits, by adding three parity bits to the 8b regular ECC code. The three parity bits are defined as follows:

- P0 (Code[8]) = XOR {D0, D3,...,D78}

- P1 (code[9]) = XOR {D1,D4,..., D79}

- P2 (Code[10]) = XOR {D2, D5,..., D80}

Note that D80 is a valid bit, VBIT.

# 6.2 Block Description

The database is divided into a number of internal blocks, dependent on the processor capacity. In case of 80b, 160b, and 320b configurations, each array block works independently. In case of wider widths of 480b and 640b, two array blocks are paired. The valid 480b and 640b block pairs are 0 and 4, 1 and 5, 2 and 6, and 3 and 7. Each of these blocks is configurable into the following organizations: 4k x 80b, 2k x 160b, 1k x 320b, and 512 x 640b.

Two neighboring blocks in a super block pair can be combined to create two blocks of one of the following combinations:

- One block 1k x 480b and one block of 1k x 0b,

- One block 1k x 480b and one block 1k x 80b

- One block 1k x 480b and one block 2k x 80b

- One block 1k x 480b and one block 1k x 160b

- Two blocks of 512 x 640b

Additionally, the blocks can be configured to store other widths (example: 8k x 40b) through the use of block masks.

To program a 640b entry into an Array Block (AB), the 320 LS bits are programmed in the first AB of the block pair and then 320 Most Significant bits are programmed in the second AB of the block pair. Array Block numbers are generated in the final result for 640b compares. For entries 0 through 511, the AB number in the result is the same as the first AB in the block pair. For entries 512 to 1023, the AB number in the result is the same as the second AB in the block pair.

When database ECC scan is enabled and the block is enabled, then all database records in that block take part in the scanning process irrespective of their VBIT status, valid or empty.

| Block Mask       | MSB     | Block M | lask Register 0 |     | LSB  |

|------------------|---------|---------|-----------------|-----|------|

| Register [319:0] | MSB     | Block M | lask Register 1 |     | LSB  |

|                  | MSB     | Block M | lask Register 2 |     | LSB  |

|                  | MSB     | Block M | lask Register 3 |     | LSB  |

|                  |         |         |                 |     |      |

| Database Block   | 12'h000 | MSB     | x               | LSB | VBIT |

|                  |         | MSB     | Y               | LSB |      |

|                  | 12'h001 | MSB     | x               | LSB | VBIT |

|                  |         | MSB     | Y               | LSB |      |

|                  |         |         |                 |     | :    |

|                  | 12'hFFE | MSB     | x               | LSB | VBIT |

|                  |         | MSB     | Y               | LSB |      |

|                  | 12'hFFF | MSB     | Х               | LSB | VBIT |

|                  |         | MSB     | Y               | LSB |      |

#### Table 8: Block Organization

Each 80-bit database record has a Validity Bit, VBIT. The status of the VBIT, valid, '1' or invalid, '0,' determines if the record takes part in compare operations. When a VBIT is set to valid '1,' the database record takes part in a compare operation. When the VBIT is cleared to '0,' that record does not take part in a compare operation.

To invalidate or delete a database entry, clear the VBIT to '0.' Only one VBIT needs to be cleared to '0' for 320b, 480b, and 640b records.

| Table 9: | Invalidate | or Delete | Database | Record |

|----------|------------|-----------|----------|--------|

|----------|------------|-----------|----------|--------|

|               | A to H Represent 80-bit Segments<br>A = [79:0], B = [159:80], C = [239:160], to H = [639:560] |

|---------------|-----------------------------------------------------------------------------------------------|

| 80-bit Entry  | Must clear VBIT of {A} to '0'                                                                 |

| 160-bit Entry | Must clear one location of VBIT in set {A, B} to '0'                                          |

| 320-bit Entry | Must clear one location of VBIT in set {A, B, C, D} to '0'                                    |

| 480-bit Entry | Must clear one location of VBIT in set {A, B, C,, F} to '0'                                   |

| 640-bit Entry | Must clear one location of VBIT in set {A, B, C,, H} to '0'                                   |

### 6.2.1 Superblock

The blocks are grouped into superblocks, each superblock is composed of a set of blocks. For each compare cycle, each superblock can offer one search key to its member blocks. All blocks in a single superblock must share the same search key on a given search operation. However, individual blocks within a superblock can have different block masks. Table 10 details the superblock per core assignments for a processor with 2048k 40b or 1024k 80b records.

Table 10: Superblock and Block Assignments per Core

| Superblock | Blocks                 |

|------------|------------------------|

| 0          | 0, 1, 2, and 3         |

| 1          | 4, 5, 6, and 7         |

| :          | :                      |

| 30         | 120, 121, 122, and 123 |

| 31         | 124, 125, 126, and 127 |

### 6.2.2 Block and Superblock Relationship

For each device the associated blocks and superblocks are listed in Table 11.

Table 11: Device Block and Superblock per Core Details

| 40b Records | Number of Blocks | Block Configuration    | Number of Superblocks |

|-------------|------------------|------------------------|-----------------------|

| 1024k       | 128              | 4k x 80b, configurable | 32                    |

| 512k        | 64               | 4k x 80b, configurable | 16                    |

### 6.2.2.1 Number of Records per Width

For each device, the associated number of records based on block width is listed in Table 12. The native record widths are 80b, 160b, 320b, 480b, or 640b. Other sized records may be stored in a native record width and accessed by the use of block masks. For example, two 40b records may be stored in one 80b record.

#### Table 12: Record Details per Core

|       | 80-bit<br>Records |      | 320-bit<br>Records | 480-bit<br>Records | 640-bit Records |

|-------|-------------------|------|--------------------|--------------------|-----------------|

| 1024k | 512k              | 256k | 128k               | 64k                | 64k             |

| 512k  | 256k              | 128k | 64k                | 32k                | 32k             |

#### Table 13: Configuration of 480b Record (Assumes Native 640b Record)

|                | Option #1 | Optio | on #2 | Optic | on #3 |

|----------------|-----------|-------|-------|-------|-------|

| Record Widths  | 480b      | 480b  | 80b   | 480b  | 160b  |

| No. of Entries | 64k       | 64k   | 128k  | 64k   | 64k   |

### 6.3 Error Detection and Correction

This section describes the following types of error detection for the device.

- Database array soft error detection and correction

- Context Buffer soft error detection

- User data array soft error detection and correction

- Logical table register soft error detection

### 6.3.1 Database Soft Error Detection and Correction

This device implements ECC protection for database soft errors. ECC is calculated and stored automatically by the processor during write operations to database locations. Optionally, Device error GIO\_L can be asserted when any database soft error is detected. Additionally, Database Soft Error bit in the Error Status Register is asserted.

Table 14 outlines all of the different combinations of Database Soft Error Scan and ECC Scan that are possible, and how to select each configuration using Device Configuration Register (DCR) options.

#### Table 14: Database Scan Options

| Database Scan Type        | DCR[6] Soft Error Scan Enable | DCR[7] Invalidation Enable | DCR[8] Auto-Correction Enable |

|---------------------------|-------------------------------|----------------------------|-------------------------------|

| Database Scan Enabled     | 1                             | 0: Detect only             | 0: No correction              |

|                           |                               | 1: Detect and invalidate   | 1: Correction                 |

| Database Scan<br>Disabled | 0                             | X                          | X                             |

### 6.3.2 Context Buffer Soft Error Detection

The context buffer is parity protected. The parity for an entry in the context buffer is checked during accesses to that particular entry, except for writes. Context buffer logic automatically initializes all context buffer location after power up.

The Context Buffer parity is checked only during Read, Context Buffer Write and Compare, and Context Buffer No Write and Compare instructions. Context Buffer parity is not checked for Context Buffer Write and Context Buffer Skip and Compare instructions. Since the data in the context buffer is dynamic, there is no corrective action for a memory error.

Context Buffer parity errors can be monitored by observing GIO\_L signal. Context Buffer Parity Error field (bit TBD) in the Error Status Register is asserted if the corresponding Error Status Mask register bit is enabled (by setting it to 1'b1). Context Buffer is protected by parity (1b per 16b of data). The error checking happens each master key read and if the error is found, 'PktErr' is asserted and the packet error vector bit 'CB Parity Error during compare' is set in the response. In addition to this, the error is captured in an error status register which can be enabled to create interrupt on GIO\_L pin.

When GIO\_L is asserted or an error reply is generated, the Error Status Register should be read to determine the cause of the interrupt. GIO\_L is asserted for database and UDA parity error.

# **Chapter 7: User Data Array**

# 7.1 Overview

The User Data Array (UDA) is a random access memory resource within the processor that can be used for associated data storage as well as other application such as statistics, counters, and algorithmic search. The size of the UDA is device dependent and can be up to 512 Mbits per core. Associated data storage for database search results is the application envisioned for the UDA. The UDA supports flexible access widths, concurrent accesses from multiple request engines, and single-cycle accesses up to 1024 bits. If the search results in a miss, then 0s are returned in the specified AD width. In AD-Only mode, this is the only indication that the search missed. As such, it is not recommended to have all 0s as valid associated data.

The User Data Array also supports a second level of associated data indirection. Contact your local application engineer for additional details.

# 7.2 Features

The UDA provides the following features:

- Total capacity: 512 Mb/256 Mb per core, with option to power-off any segment of memory in unit of 8 Mb.

- UDA blocks: 256/128 per core.

- Block width configurable: 32b, 64b, 128b, 256b.

- Each block is independently configurable.

- Parallelism: Up to eight per core associated data per clock.

- Each associated data can be a different size.

- ECC protection.

- ECC scheme: 1-bit detect and correct, 2-bit detect.

### Table 15: Database Array Capacity per Core

| Database Array per Core | Records                    |

|-------------------------|----------------------------|

| 40 Mb                   | 1024k 40b database records |

| 20 Mb                   | 512k 40b database records  |

### Table 16: User Data Array Capacity Per Core

| User Data Array (Mb) | 32b Associate Data Records |  |  |  |  |  |  |  |

|----------------------|----------------------------|--|--|--|--|--|--|--|

| 512 Mb               | 16M                        |  |  |  |  |  |  |  |

| 256 Mb               | 8M                         |  |  |  |  |  |  |  |

### 7.3 UDA Read/Write Accesses

Each address location in the UDA memory is accessed as a 32b value. As a result, all write and read operations are done on 32-bit locations. The read/write address range of the device is given below.

The UDA also supports 64b read/write access. However, addressing is still at 32b word level. In other words, while doing 64b read or write, the LSb of the UDA address is expected to be 0.

Table 17: UDA Address Range Based on Device Size per Core

| Device Size | Address Range for 32b Access |

|-------------|------------------------------|

| 512 Mbit    | 0x0 to 0xFF_FFF              |

| 256 Mbit    | 0x0 to 0x7F_FFFF             |

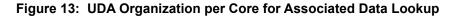

# 7.4 UDA Organization for Associated Data

The user data array is organized into 2 x 256 blocks, 2Mb each. Each block has 2 Mb of capacity and can be configured in widths of 32, 64, 128, or 256 bits. Memory update accesses are always 32 or 64 bits. Each block is read-accessible independent of the other blocks. A total of eight accesses are allowed at the same time. Only two parallel accesses are allowed per 32 Mb and the two parallel access cannot be the same 2 Mb block. Each parallel access can have a different width, as long as the aggregate data size does not exceed 1024 bits.

For power savings, UDA blocks may be powered down in units of 4 consecutive blocks. See UDA configurations registers for further details.

If there are more than four associated data accesses, then the max AD size for result 0 and 4 each is 128b or less. The same rule applies for result pairs 1 and 5, 2 and 6, and 3 and 7.

Each UDA block can be dynamically accessed in multiple bit widths ranging from 32b to 256b. This allows the user to assign associated data of various widths on a per database array block basis. This gives flexibility to the table management software to reassign blocks to different tables as the tables grow or shrink in real-time. As a result, logical tables may be mapped onto noncontiguous blocks within the UDA blocks.

# 7.5 Database to UDA Referencing

The UDA address generation is controlled by the application using registers, where the base addresses and shift parameters are configured on a per Database Array block basis.

The translation from search index results to UDA memory is done on a per database block basis. In particular, each Database Array block has a user-configured base address (BA) as well as shift value and shift direction, as shown below. The BA represents the UDA address corresponding to the first entry in the searched Database Array block. The shift represents the binary division of the DBA address so as to normalize it into continuously increasing 32b AD words. The correspondence between database array block widths and UDA data-widths is shown below, along with the shift parameters. The shift index direction and shift index value must be programmed by the user.

In the examples below, the 15b base address (BA) represents the UDA address where the logical table to which the current database block belongs is referenced from. One base address is available for each database array block. The total number of 32b locations in a 512-Mbit UDA is 16M, which requires a 24b address. The total number of 640b address locations in a database array block is 512, thereby, requiring a 9b address. Thus, the BA bits needed for this case are 15b (24b – 9b).

The address translation is done for each search result after the hit index is derived. Both the index and the derived UDA data are output to support different applications that may require either or both outputs. Additional indirection is available to dynamically move associated data block from one UDA block to another.

### 7.5.1 UDA Base Address Translation

The following are the equations to derive the base address:

BA (base address) for AB (as defined in equation): (FLTA >> 9) >> n, where (2<sup>n</sup> = (ADwidth/32) (1)

BA for the next AB: (ADwidthPrevBlock/ADwidthNextBlock) × (BA for previous AB+ (640/ABwidth)) (2)

FLTA (first level translated address)—physical UDA address derived from the DBA index.

A representation of the base address, in terms of FLTA is given below:

Base address (BA) calculation:

FLTA = ( {BA, 9'b0} + ShiftIndex ) << 0, if AD = 32b FLTA = ( {BA, 9'b0} + ShiftIndex ) << 1, if AD = 64b FLTA = ( {BA, 9'b0} + ShiftIndex ) << 2, if AD = 128b FLTA = ( {BA, 9'b0} + ShiftIndex ) << 3, if AD = 256b

The following subsection provides an example of the base address calculation.

The User Data Array also supports a second level of associated data indirection. Contact your local application engineer for additional details.

Two database array blocks are configured to be 320b width. Assume these blocks are called 0x15 and 0x16. The database address (in unit of 80b words) range of the entries in these blocks is 0x15000 to 0x16FFF. The total number of database entries in the database for these two blocks is 2K 320-bit entries. Thus, 2K entries are required in the UDA to correspond to the 2K database entries. Assume the associated data for these database entries is 64b. The translated address per block is generated by the following:

Since the DBA width is 320, there are 1024 entries per DBA block.

In this example, we are considering that the first DBA entry corresponds to UDM8 (memory is at 64Mb), this means that the address of the UDA entry in unit of 32b words is 0x200000. The table represents the address of the UDA entry in terms of UDA size.

From Table 18 on page 35, FLTA = 0x200000, FLTA[21] = 1b1, BA[11] = 1b1 or BA = 0x800.

- Pre-shift Index of the first entry in 320b database block 0x15 = 0x000.

- Pre-shift Index of the last entry in 320b database block 0x15 = 0xFFC.

- Shifted Index for the first entry in database block 0x15 = 0x000.

- Shifted Index for the last entry in database block 0x15 = 0x3FF (shifted right by 2, from table) DB[11:2].

- FLTA, start = 0x200000 in terms of AD size.

- FLTA, end = 0x2007FE in terms of AD size.

For the next DB, since contiguous addressing is considered, the base address is 0x802.

Use equation 2:  $(64/64) \times (0x800 + 640/320) = 0x802$  or incrementing BA[1]/FLTA[11] derives the same result:

- Pre-shift Index for the first entry in 320b database block 0x16 = 0x000.

- Pre-shift Index for the last entry in 320b database block 0x16 = 0xFFC.

- Shifted Index for the first entry in database block 0x16 = 0x000.

- Shifted Index for the last entry in database block 0x16 = 0x3FF (shifted right by 2, from table) DB[11:2].

- FLTA, start = 0x200800 in terms of AD size.

- FLTA, end = 0x200FFE in terms of AD size.

|     | AD  | AB<br>shift<br>dir | FTA23 | FTA22 | FTA21 | FTA20 | FTA19 | FT <b>A</b> 18 | FTA17 | FTA16 | FTA15 | FTA14 | FTA13 | FTA12 | FTA11 | FTA10 | FTA9 | FT <b>A</b> 8 | FTA7 | FTA6 | FTA5 | FTA4 | FTA3 | FTA2 | FTA1 | FTA0 |

|-----|-----|--------------------|-------|-------|-------|-------|-------|----------------|-------|-------|-------|-------|-------|-------|-------|-------|------|---------------|------|------|------|------|------|------|------|------|

| 640 | 32  | R3                 |       | BA13  | BA12  | BA11  | -     | -              | BA8   | BA7   | -     | BA5   | _     | BA3   |       |       | BA0  | -             | DB10 |      | DB8  |      | DB6  | DB5  |      | DB3  |

| 320 | 32  | R2                 | BA14  | BA13  | BA12  | BA11  | BA10  | BA9            | BA8   | BA7   | BA6   | BA5   | BA4   | BA3   | BA2   | BA1   | DB11 | DB10          | DB9  | DB8  | DB7  | DB6  | DB5  | DB4  | DB3  | DB2  |