# PROGRAMMING GUIDE

# LSI53C040 Enclosure Services Processor

Version 1.1

December 2000

This document contains proprietary information of LSI Logic Corporation. The information contained herein is not to be used by or disclosed to third parties without the express written permission of an officer of LSI Logic Corporation.

LSI Logic products are not intended for use in life-support appliances, devices, or systems. Use of any LSI Logic product in such applications without written consent of the appropriate LSI Logic officer is prohibited.

Document DB15-000100-01, Second Edition (December 2000) This document describes the LSI Logic LSI53C040 Enclosure Services Processor and will remain the official reference source for this product. This guide is intended for use with the SAF-TE Firmware C1 source code release and meets the criteria set within the LSI Logic Software Release Procedure.

#### To receive product literature, visit us at http://www.lsilogic.com.

LSI Logic Corporation reserves the right to make changes to any products herein at any time without notice. LSI Logic does not assume any responsibility or liability arising out of the application or use of any product described herein, except as expressly agreed to in writing by LSI Logic; nor does the purchase or use of a product from LSI Logic convey a license under any patent rights, copyrights, trademark rights, or any other of the intellectual property rights of LSI Logic or third parties.

Copyright © 1999–2000 by LSI Logic Corporation. All rights reserved.

#### TRADEMARK ACKNOWLEDGMENT

The LSI Logic logo design is a registered trademark of LSI Logic Corporation. All other brand and product names may be trademarks of their respective companies.

# Preface

This programming guide assists experienced firmware developers who wish to customize the LSI53C040 SAF-TE Firmware for specialized enclosure management applications, or to develop firmware using the LSI53C040 firmware architecture as a basis. It assumes a thorough knowledge of the "C" programming language and the SAF-TE specification, and understanding of the components and services that will be provided in the enclosure design. For more background material that may provide information on these subjects, refer to the Section "References," and Section "Related Publications," in this document.

This guide contains general considerations for developers who are designing or customizing firmware and includes:

- describing the SCSI portion of the LSI53C040 firmware, including the SCSI commands supported,

- describing the two-wire serial portion of the LSI53C040 firmware,

- describing the LSI53C040 implementation of the firmware for the binary inputs/outputs, and of the LED outputs that provide enclosure monitoring and notification services to the host,

- giving information on the LSI Logic implementation of the SAF-TE command set, and

- describing the firmware configuration utility and the data structures that hold the specific information on the components and services in the enclosure.

#### Audience

This document was prepared for firmware developers who plan on customizing the SAF-TE firmware for enclosure management applications.

#### Organization

This document has the following chapters and appendix:

- Chapter 1, Using the Programming Guide, provides details about the conventions used in this guide, describes the SAF-TE firmware, and lists the features.

- Chapter 2, General Design Considerations, provides design information for firmware developers.

- Chapter 3, SAF-TE Source Code, discusses the Boot Module, Configuration Module, and SAF-TE Module that contains the safte.c source code.

- Chapter 4, **SAF-TE Command Implementation**, lists the SAF-TE commands supported by the LSI53C040 chip.

- Chapter 5, Configuration Data and the Configuration Utility, provides the potential questions that may be asked while running the configuration utility.

- Appendix A, LSI53C040 Board Utilities, discusses the data transfer types.

#### **Related Publications**

LSI53C040 Enclosure Services Processor Technical Manual, Order Number S14042.A

LSI53C040 Enclosure Services Processor SAF-TE Firmware User's Guide, Order Number S14004.A

#### References

Yeralan, Sencer and Ashutosh Ahluwalia. 1997. *Programming and Interfacing the 8051 Microcontroller.*

Ayala, Kenneth J. 1997. *The 8051 Microcontroller: Architecture, Programming, & Applications.* Second Edition.

#### Scope of this Programming Guide

This programming guide only discusses the firmware implementation of the SAF-TE protocol, even though the LSI53C040 device could support the SES protocol. LSI Logic will not be pursuing a SES firmware implementation.

#### **Conventions Used in This Manual**

Hexadecimal numbers are indicated by the prefix "0x" —for example, 0x32CF. Binary numbers are indicated by the prefix "0b" —for example, 0b0011.0010.1100.1111.

This manual makes frequent references to the source code of the LSI53C040 SAF-TE firmware. We use routine names, typed in **bold**, *italics*, and regular text, to indicate the specific section of code being referenced.

#### **Revision Record**

| Revision | Date  | Remarks                                |

|----------|-------|----------------------------------------|

| 1.0      | 5/99  | First Edition.                         |

| 1.1      | 12/00 | Product names changed from SYM to LSI. |

# Contents

| Chapter 1 | Using | g the Pr | ogramming Guide                                 |      |

|-----------|-------|----------|-------------------------------------------------|------|

|           | 1.1   | Introdu  | ction                                           | 1-1  |

|           | 1.2   | Genera   | al Description                                  | 1-2  |

|           | 1.3   | Feature  | ∂S                                              | 1-2  |

|           |       | 1.3.1    | MPIO/MPLED Mapping                              | 1-2  |

|           |       | 1.3.2    | TWS Interface Peripheral Support                | 1-2  |

|           |       | 1.3.3    | SAF-TE Interface                                | 1-3  |

|           |       | 1.3.4    | Programmable Enclosure Configuration Monitoring | 1-4  |

| Chapter 2 | Gene  | ral Desi | gn Considerations                               |      |

|           | 2.1   | 8051/8   | 032 Background                                  | 2-1  |

|           |       | 2.1.1    | 8032 Architecture Features                      | 2-2  |

|           |       | 2.1.2    | Archimedes Compiler Features                    | 2-4  |

|           | 2.2   | The LS   | SI53C040 Firmware                               | 2-7  |

|           | 2.3   | SCSI a   | Ind DMA                                         | 2-8  |

|           | 2.4   | 8032-B   | ased Timer                                      | 2-9  |

|           | 2.5   | TWS B    | us                                              | 2-9  |

|           | 2.6   | Power-   | On/Start-up                                     | 2-10 |

|           | 2.7   | Norma    | Processing                                      | 2-10 |

|           | 2.8   | Interrup | ots                                             | 2-11 |

|           |       | 2.8.1    | 8032 Processor Interrupts                       | 2-11 |

|           |       | 2.8.2    | LSI53C040 Interrupts                            | 2-12 |

|           | 2.9   | Debug    | ging                                            | 2-12 |

|           | 2.10  | Setting  | Up A Development Environment                    | 2-12 |

|           |       | 2.10.1   | Development Tools                               | 2-13 |

|           |       | 2.10.2   | Source Code Composition                         | 2-14 |

|           |       | 2.10.3   | Register Naming Translations                    | 2-14 |

|           |       | 2.10.4   | Calling Trees                                   | 2-20 |

|           | 2.11  | Configu  | uration Examples                                | 2-25 |

|           |     | 2.11.1   | Example 1                            | 2-25 |

|-----------|-----|----------|--------------------------------------|------|

|           |     | 2.11.2   | Example 2                            | 2-28 |

|           |     | 2.11.3   | Example 3                            | 2-29 |

| Chapter 3 | SAF | -TE Sour | ce Code                              |      |

|           | 3.1 | SAF-TE   | E Source Code Overview               | 3-1  |

|           | 3.2 | Boot M   | odule                                | 3-2  |

|           | 3.3 | Configu  | uration Module                       | 3-3  |

|           |     | 3.3.1    | Loader_Options Data Structure        | 3-4  |

|           |     | 3.3.2    | Config Data Structure                | 3-5  |

|           | 3.4 | SAF-TE   | E Module                             | 3-19 |

|           |     | 3.4.1    | Compilation Instructions for safte.c | 3-19 |

|           |     | 3.4.2    | Main Program                         | 3-22 |

|           |     | 3.4.3    | Interrupts                           | 3-39 |

|           |     | 3.4.4    | Error Reporting                      | 3-49 |

|           | 3.5 | Freque   | ntly Asked Questions (FAQ)           | 3-49 |

| Chapter 4 | SAF | -TE Com  | mand Implementation                  |      |

|           | 4.1 | SCSI C   | Commands                             | 4-1  |

|           |     | 4.1.1    | Inquiry                              | 4-1  |

|           |     | 4.1.2    | Read Buffer                          | 4-3  |

|           |     | 4.1.3    | Request Sense                        | 4-4  |

|           |     | 4.1.4    | Send Diagnostic                      | 4-4  |

|           |     | 4.1.5    | Test Unit Ready                      | 4-5  |

|           |     | 4.1.6    | Write Buffer                         | 4-5  |

|           | 4.2 | SAF-TE   | E Read Buffer Commands               | 4-7  |

|           |     | 4.2.1    | Read Enclosure Configuration (0x00)  | 4-7  |

|           |     | 4.2.2    | Read Enclosure Status (0x01)         | 4-9  |

|           |     | 4.2.3    | Read Device Slot Status (0x04)       | 4-14 |

|           |     | 4.2.4    | Read Global Flags (0x05)             | 4-16 |

|           | 4.3 | SAF-TE   | E Write Buffer Commands              | 4-18 |

|           |     | 4.3.1    | Write Device Slot Status (0x10)      | 4-18 |

|           |     | 4.3.2    | Perform Slot Operation (0x12)        | 4-20 |

|           |     | 4.3.3    | Send Global Flags Command (0x15)     | 4-22 |

|           | 4.4 | Unsupp   | ported SAF-TE Commands               | 4-25 |

| Chapter 5  | Configuration Data and the Configuration Utility |         |                                        |      |  |

|------------|--------------------------------------------------|---------|----------------------------------------|------|--|

|            | 5.1 Using the Configuration Utility              |         | he Configuration Utility               | 5-1  |  |

|            |                                                  | 5.1.1   | Myinput.txt File                       | 5-4  |  |

|            | 5.2                                              | Questic | ons in the Configuration Utility       | 5-5  |  |

|            | 5.3                                              | After R | unning the Configuration Utility       | 5-21 |  |

| Appendix A | LSI5                                             | 3C040 B | oard Utilities                         |      |  |

|            | A.1                                              | Data Ti | ansfers                                | A-1  |  |

|            |                                                  | A.1.1   | Serial Port                            | A-1  |  |

|            |                                                  | A.1.2   | ISA                                    | A-2  |  |

|            |                                                  | A.1.3   | SCSI                                   | A-3  |  |

|            |                                                  | A.1.4   | 8067 Utilities                         | A-6  |  |

|            |                                                  | A.1.5   | LSI53C040 Board Layout/Jumper Settings | A-6  |  |

### Index

## **Customer Feedback**

# Figures

| 2.1 | Internal RAM                               | 2-3  |

|-----|--------------------------------------------|------|

| 2.2 | LSI53C040 Memory Map                       | 2-4  |

| 2.3 | System Configuration                       | 2-26 |

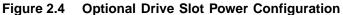

| 2.4 | Optional Drive Slot Power Configuration    | 2-28 |

| 2.5 | Dual Fans and Power Supplies Configuration | 2-30 |

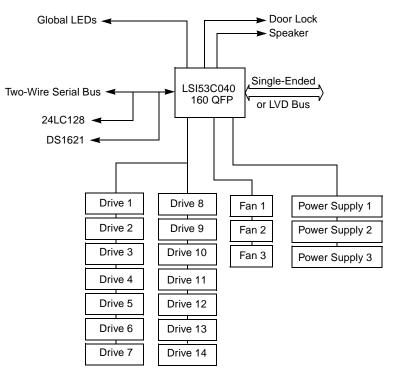

| 3.1 | Main Program                               | 3-23 |

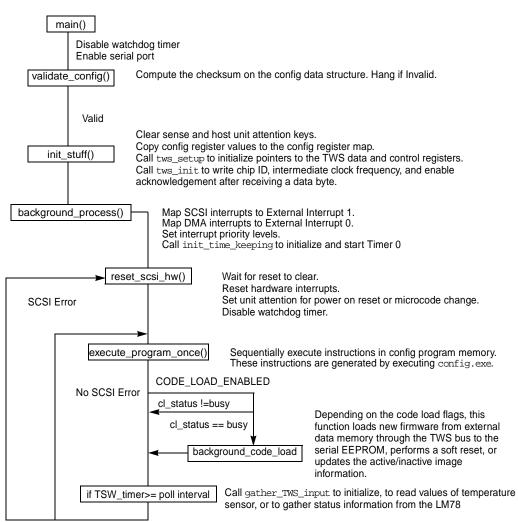

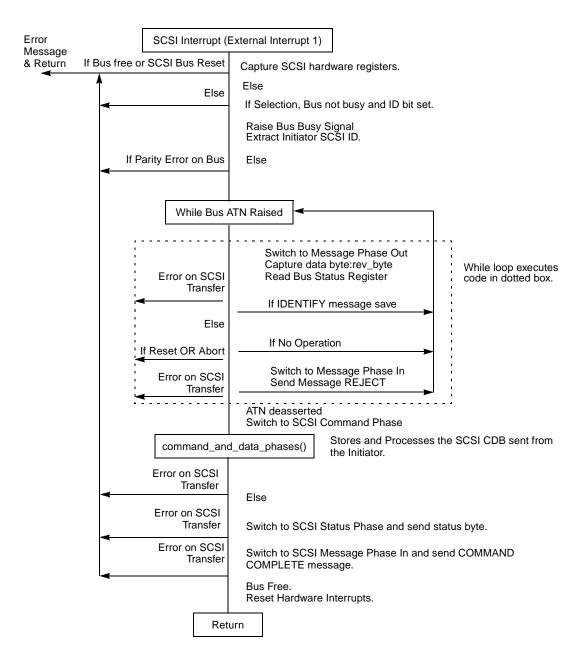

| 3.2 | Flow Diagram of ir_external1()             | 3-43 |

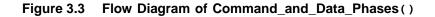

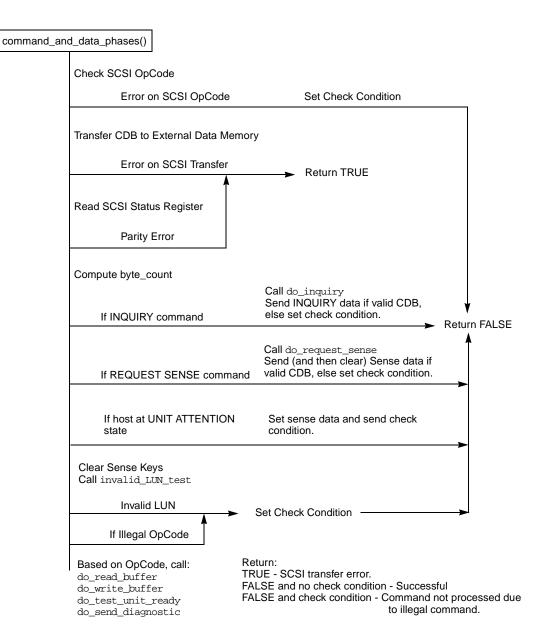

| 3.3 | Flow Diagram of Command_and_Data_Phases()  | 3-44 |

|     |                                            |      |

## Tables

| 2.1 | Source Code Files               | 2-14 |

|-----|---------------------------------|------|

| 2.2 | Special Function Register Names | 2-15 |

| 2.3 | SCSI Core/SFF-8067 Registers    | 2-16 |

| 2.4 | TWS Registers                   | 2-17 |

| 2.5 | Miscellaneous Registers         | 2-17 |

| 2.6 | System Registers                | 2-18 |

| 2.7  | MPLED/MPIO Pin Usage for Example 1                      | 2-26 |

|------|---------------------------------------------------------|------|

| 2.8  | MPLED/MPIO Pin Usage for Example 2                      | 2-29 |

| 2.9  | MPLED/MPIO Pin Usage for Example 3                      | 2-30 |

| 3.1  | Source file - bootload.c - Switches                     | 3-3  |

| 3.2  | Instructions Per Device                                 | 3-13 |

| 3.3  | Mapping of devices to MPIO and MPLED Banks              | 3-14 |

| 3.4  | Switch Name and Action                                  | 3-20 |

| 3.5  | Accumulator Settings                                    | 3-29 |

| 3.6  | TWS High-Level Subroutines                              | 3-30 |

| 3.7  | SAF-TE Mappings                                         | 3-31 |

| 3.8  | TWS Low-level Subroutines                               | 3-32 |

| 3.9  | Subroutine background_code_lode                         | 3-34 |

| 3.10 | Subroutine do_code_load                                 | 3-34 |

| 3.11 | background_code_load operation                          | 3-35 |

| 3.12 | Upper Byte Choices                                      | 3-36 |

| 3.13 | Interrupts Processed by 80C32 Microcontroller           | 3-39 |

| 3.14 | Interrupt Service Routines - General                    | 3-46 |

| 3.15 | Interrupt Service Routines - SCSI Commands              | 3-47 |

| 3.16 | Interrupt Service Routines - SCSI Read                  | 3-48 |

| 3.17 | Interrupt Service Routines - SCSI Write                 | 3-48 |

| 3.18 | Source Code Issues                                      | 3-49 |

| 4.1  | Inquiry Command Response Data                           | 4-2  |

| 4.2  | Read Buffer Data Format                                 | 4-3  |

| 4.3  | Sense Key Information                                   | 4-4  |

| 4.4  | Write Buffer Data Format                                | 4-5  |

| 4.5  | Write Buffer Data Format (Updating SAF-TE Firmware)     | 4-6  |

| 4.6  | Read Enclosure Configuration Return Values              | 4-7  |

| 4.7  | Read Enclosure Status Return Values                     | 4-10 |

| 4.8  | Fan Status Return Values                                | 4-11 |

| 4.9  | Power Supply Status Return Values                       | 4-12 |

| 4.10 | Door Lock Status Return Values                          | 4-13 |

| 4.11 | Speaker Status Return Values                            | 4-13 |

| 4.12 | Read Device Slot Status Command Return Values           | 4-15 |

| 4.13 | Power-On/Reset Default Slot Status                      | 4-16 |

| 4.14 | Read Global Flag Bytes                                  | 4-17 |

| 4.15 | Write Device Slot Status Flag Bytes                     | 4-18 |

| 4.16 | Default LED Settings for Write Device Slot Status Flags | 4-19 |

| 4.17 | Perform Slot Operation Flags                            | 4-20 |

|      |                                                         |      |

| 4.18 | Send Global Flag Bytes                                   | 4-22 |

|------|----------------------------------------------------------|------|

| 4.19 | Global Failure/Global Warning LED Options                | 4-23 |

| 4.20 | Drive Failure/Drive Warning LED Options                  | 4-24 |

| 4.21 | Array Failure/Array Warning LED Options                  | 4-24 |

| 5.1  | Configuration Utility Files                              | 5-2  |

| 5.2  | General Questions                                        | 5-5  |

| 5.3  | Enclosure Components Questions                           | 5-7  |

| 5.4  | Pin Assignment Questions                                 | 5-9  |

| 5.5  | Default LED Settings for Write Device Slot Status Flags  | 5-12 |

| 5.6  | Selections for Custom LED Settings for Write Device Slot |      |

|      | Status Flags                                             | 5-13 |

| 5.7  | Device Slot Operation Questions                          | 5-14 |

| 5.8  | Status Signal Questions                                  | 5-15 |

| 5.9  | TWS Bus Operation Questions                              | 5-17 |

| 5.10 | Questions for Firmware Bootloader                        | 5-19 |

| A.1  | Capture Register Settings                                | A-1  |

| A.2  | Command Line Inputs                                      | A-2  |

| A.3  | Configuration Using Three Serial EEPROMS                 | A-4  |

| A.4  | Configuration Using Two Serial EEPROMS                   | A-5  |

| A.5  | Switch Controls and Address                              | A-7  |

| A.6  | Jumpers and Chip Address                                 | A-7  |

| A.7  | Jumper and Bus                                           | A-8  |

| A.8  | Jumpers and Branch Address                               | A-8  |

| A.9  | Jumper and Code Load                                     | A-8  |

# Chapter 1 Using the Programming Guide

This chapter provides a general overview of the LSI53C040 Enclosure Services Processor Firmware and includes these topics:

- Section 1.1, "Introduction," page 1-1

- Section 1.2, "General Description," page 1-2

- Section 1.3, "Features," page 1-2

# 1.1 Introduction

The LSI53C040 is an enclosure services processor with 28 programmable, multipurpose I/O (MPIO) pins for enclosure monitoring and 24 programmable, multipurpose I/O pins for visual LED indicators. The LSI53C040 firmware includes configuration data tables that allow the user to map specific monitoring functions to each of these pins, so that the firmware can be adapted to any enclosure environment.

The LSI53C040 uses the SAF-TE or SES protocol to detect drive presence, condition a slot for drive insertion or removal, and monitor enclosure services. The fan, power supply, door lock, alarm, and slot drive power are examples of enclosure services.

# **1.2 General Description**

The LSI53C040 SAF-TE firmware controls an 80C32 microcontroller core in the LSI53C040 device. This microcontroller is compatible with the Intel MCS51 family. It runs independently in interrupt mode.

The LSI53C040 SAF-TE firmware contains three major architectural components, each implementing a separate I/O interface to the chip. The SCSI block governs the SCSI interface and implementation of all the SCSI commands used to send data packets to the host. The Two-Wire Serial (TWS) interface bus is primarily used as an input bus. See Section 2.5, "TWS Bus," page 2-9 for more detailed information.

# 1.3 Features

This section describes the LSI53C040 SAF-TE firmware capabilities and associated features, which include MPIO/MPLED Mapping, TWS Interface Peripheral Support, the SAF-TE Interface, and Programmable Enclosure Configuration monitoring.

## 1.3.1 MPIO/MPLED Mapping

- Ability to assign MPIO/MPLED pins to dedicated functions such as drive, power supply, and fan status monitoring

- Automatically configures MPIO/MPLED pins

- Generates listing of assigned pins

- Ability to modify blink patterns for LEDs

## 1.3.2 TWS Interface Peripheral Support

- National Semiconductor LM75 2-Wire Serial Digital Temperature Sensor and Thermal Watchdog

- Dallas Semiconductor DS1621 2-Wire Serial Digital Thermometer and Thermostat

- National Semiconductor LM78 fan, power supply, and temperature monitoring

## 1.3.3 SAF-TE Interface

The SAF-TE interface complies with the SAF-TE Specification R041497 and provides these features:

- Supports Read Buffer Commands

- Read Enclosure Configuration

- Read Enclosure Status

- Read Device Slot Status

- Read Global Flags

- Supports Write Buffer Commands

- Write Device Slot Status

- Performs Slot Operation

- Send Global Commands

- Supports the Upload Firmware command

- Allows selection from one of 11 SCSI IDs (7-0, 15, 14, 13)

- Allows connection from any data line, bits 8 through 15, to any one of the SHID[2:0] (SCSI High ID) pins on the LSI53C040

- Supports Slot Power Control Option

- Supports Over Temperature LED Option

# **1.3.4 Programmable Enclosure Configuration Monitoring**

The enclosure configuration monitoring allows:

- Up to 14 device slots

- Up to 6 fans and power supplies (single or dual input status)

- Up to 15 binary temperature sensors (single input status)

- Up to 4 temperature sensors (TWS)

- Optional Ready device for use (slot power control) and Prepare device for insertion/removal output signals

- Programmable Vendor, Product, and Enclosure ID

- Host Controllable Door Lock and Speaker Option

- Selection of one or two LED's per device slot

- Global LED's option for enclosure, drive, and array status

# Chapter 2 General Design Considerations

This chapter provides design information for firmware developers and includes these topics:

- Section 2.1, "8051/8032 Background," page 2-1

- Section 2.2, "The LSI53C040 Firmware," page 2-7

- Section 2.3, "SCSI and DMA," page 2-8

- Section 2.4, "8032-Based Timer," page 2-9

- Section 2.5, "TWS Bus," page 2-9

- Section 2.6, "Power-On/Start-up," page 2-10

- Section 2.7, "Normal Processing," page 2-10

- Section 2.8, "Interrupts," page 2-11

- Section 2.9, "Debugging," page 2-12

- Section 2.10, "Setting Up A Development Environment," page 2-12

- Section 2.11, "Configuration Examples," page 2-25

# 2.1 8051/8032 Background

The user is encouraged to become familiar with the 8032 8-bit microcontroller prior to reading this guide. The primary differences between the 8051 and the 8032 are the internal RAM (256 bytes vs. 128 bytes for the 8051), also the 8032 has one additional timer. Several excellent resources are available to aid the user in becoming familiar with the 8032, including those listed in the Preface of this guide.

This section covers some of the key highlights of the 8032 architecture and some important Archimedes compiler features. The remainder of the chapter provides an overview of the LSI53C040 firmware and general design considerations necessary to use this firmware most effectively.

### 2.1.1 8032 Architecture Features

The architectural features of the 8032 microcontroller are key to the understanding and use of the LSI53C040 firmware. These features include: Section 2.1.1.1, "Register Banks," page 2-2, Section 2.1.1.2, "Memory Areas," page 2-2, and Section 2.1.1.3, "Special Function Registers," page 2-4.

#### 2.1.1.1 Register Banks

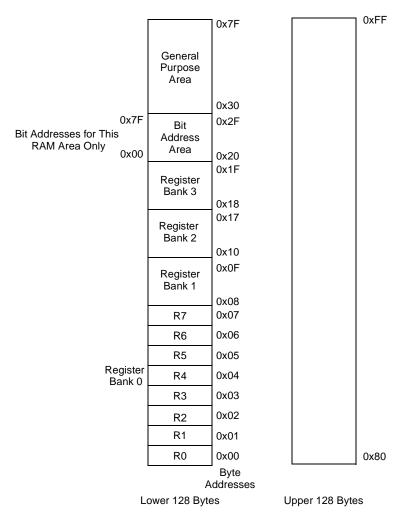

Four register banks that contain eight registers each in the 8032 reside in the lower 128 bytes of the internal RAM. See Figure 2.1 for an example of these register banks.

#### 2.1.1.2 Memory Areas

The 8032 architecture supports a number of physically separate memory areas for program and data. Each memory area offers certain advantages and disadvantages. Refer to the *Intel 8-bit Embedded Controllers* databook or other 8051 reference material for more information about the 8032 memory architecture. The following sections briefly discuss program memory, the internal data memory, and the external data memory.

**Program Memory** – Since the 8032 is a ROMless variant of the 8051, an external 16 Kbytes memory is required to hold the program code. The LSI53C040 has the ability to automatically download this program code from a serial EEPROM over the TWS bus into the external 16 Kbytes memory space.

**Internal Data Memory** – The 8032 contains 256 bytes of internal data memory, which can be read and written. The first 128 bytes of internal data memory are both directly addressable and indirectly addressable. The upper 128 bytes of data memory (from 0x80 to 0xFF) can be addressed only indirectly. With indirect addressing, the referenced register contains the address of the register or cell that actually contains the data to be used. There is also a 16-byte area starting at 0x20 that is bit-addressable. See Figure 2.1 for more detailed information.

Figure 2.1 Internal RAM

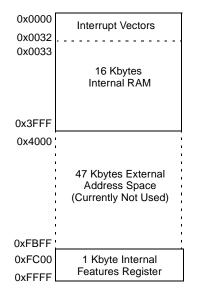

**External Data Memory Map** – The address decode block in the LSI53C040 decodes addresses that are generated by the microcontroller. Additionally, it multiplexes memory space accesses between the different register and memory blocks according to the memory map. See Figure 2.2 for an example of this memory map.

Figure 2.2 LSI53C040 Memory Map

### 2.1.1.3 Special Function Registers

The 8032 provides a distinct memory area for accessing Special Function Registers (SFRs). SFRs are used in the program to control timers, counters, serial I/Os, port I/Os, and peripherals. SFRs reside from address 0x80 to 0xFF, and can be accessed by bits, bytes, and words. The special function registers are listed in Table 2.2.

## 2.1.2 Archimedes Compiler Features

The user should be familiar with several Archimedes compiler features that are related to the above 8032 features before reading the source code.

#### 2.1.2.1 Control Directives

The four control directives are: AREGS/NOAREGS, REGISTERBANK, and SMALL.

The **AREGS** control causes the compiler to use absolute addressing for registers R0 through R7. Absolute addressing improves the efficiency of the generated code. **PUSH** and **POP** instructions function only with direct or absolute addresses. By using the **AREGS** directive, functions can directly push and pop registers.

The **NOAREGS** control disables absolute addressing for registers R0 through R7. Functions that are compiled with **NOAREGS** are not dependent on the register bank and may use all 8051 register banks. This directive may be used for functions that are called from other functions using different register banks.

The **REGISTERBANK** control selects the specific register bank to use for subsequent functions declared in the source file. Resulting code may use the absolute form of register access when the absolute register number can be computed. The **using** function attribute supersedes the effects of the **REGISTERBANK** directive.

The **SMALL** memory model is used to compile the firmware for performance reasons. This results in all function variables and local data segments being placed in the internal data memory of the 8032 by default. This results in smaller code size and faster execution. Since the internal memory size is very limited (256 bytes), larger or infrequently used variables may be declared to be in any of the 8032 memory ranges. Since this is the compiler's default memory model, a **#pragma small** is not needed in the source file, and **SMALL** does not have to be on the C51 command line.

#### 2.1.2.2 Compiler Keywords

A list of compiler keywords are:

- \_at\_ variables may be located at absolute memory locations in the C program source modules using the \_at\_ keyword.

- **sbit** the **sbit** data type allows the user to access bit-addressable SFRs.

- data directly accessible internal data memory; fastest access to variables (128 bytes).

- **bdata** bit-addressable internal data memory; allows mixed bit and byte access (16 bytes).

- idata indirectly addressable internal data memory; accessed across the full internal address space (256 bytes).

- pdata paged (256 bytes) external data memory (16 Kbytes).

- xdata external data memory (refers to any location in the full 64 Kbytes of external data memory).

- code program memory (16 Kbytes).

- sfr SFRs are declared in the same fashion as other variables. The only difference is that the data type specified is sfr rather than char or int.

- **interrupt** an extension for standard C function declarations that indicates that the function is an interrupt function.

- **using** specifies which register bank the function uses.

#### 2.1.2.3 Generic Pointers vs. Memory-Specific Pointers

Due to the unique architecture of the 8051 and its derivatives, the compiler provides two different types of pointers: generic pointers and memory-specific pointers.

Generic pointers are always stored using three bytes. The first byte is for the memory type, the second is for the high-order byte of the offset, and the third is for the low-order byte of the offset. Generic pointers may be used to access any variable regardless of its location in 8051 memory space.

Memory-specific pointers always include a memory type specification in the pointer declaration and always refer to a specific memory area. Because the memory type is specified at compile-time, the memory type byte required by generic pointers is not needed by memory-specific pointers. Like generic pointers, the user may specify the memory area in which a memory-specific pointer is stored. Memory-specific pointers may be used to access variables in the declared 8051 memory area only. Memory-specific pointers provide the most efficient method of accessing data objects, but at the cost of reduced flexibility.

For more information, refer to your C compiler documentation, specifically the sections covering directives and language extensions.

<u>Note:</u> The user must be aware that this compiler does **not** generate re-entrant code, that function parameters are **not** passed on the stack, and that interrupt level routines and background routines **cannot** share subroutines. Virtually all of the source code is written in C. Assembly language is only needed for stack initialization before control is passed to the C code.

# 2.2 The LSI53C040 Firmware

The heart of the LSI53C040 architecture is its 52 input and output pins (28 MPIO pins and 24 MPLED pins). The user may specify (by using the configuration utility) an almost unlimited number of configurations. The SAF-TE firmware was designed to make these configurations simple to implement by using this utility. Additionally, the SAF-TE firmware is coupled with a software state machine that polls all of the binary inputs and drives all of the binary outputs. Simultaneously, the firmware maintains copies of all the necessary SAF-TE/SCSI command responses so that the SCSI interrupt software can return these responses to a host/initiator at any time.

This state machine design allows the user to specify all of the inputs and outputs without having to change the 8032 firmware. In addition, this design actually simplifies and shortens the size of the 8032 firmware, by moving much of the decision making process to the configuration utility. Consequently, more memory is available in the 8032 for user enhancements. Refer to Chapter 5 for more detailed information about configuration data and the configuration utility.

The program and data for this state machine design is passed from the configuration utility to the firmware by using a data structure called **config**. In addition, the **config** data structure also contains all the information gathered by the configuration utility, such as the SCSI ID, TWS devices to be supported, scanning intervals, etc.

The 8032 microcontroller is at the core of the LSI53C040 device and runs at 40 MHz. This microcontroller provides more than sufficient processing power to complete the work to be done by the LSI53C040. The environmental monitoring protocols, such as SAF-TE and SES, do

not require much SCSI traffic. Therefore, the LSI53C040 is an excellent choice for enclosure monitoring functions, although attention to certain software details is necessary to make effective use of its features.

# 2.3 SCSI and DMA

The most important of those details is the SCSI interface. The DMA engine in the LSI53C040 helps improve the overall speed of the SCSI interface, but that alone is not enough. Because this core is relatively slow, the software is designed to complete the SCSI work as quickly as possible.

The SCSI interface is done at interrupt level. The 8032 has 6 interrupt sources, but only two interrupt levels. SCSI is done at the lower interrupt level, while DMA is done at the higher interrupt level. This is necessary because the 8032 is placed in a low power mode during DMA, and the DMA interrupt is used to "wake up" the 8032 when DMA is completed.

<u>Note:</u> The 8032 must be placed in low power mode so that it is not executing instructions; that is, the 8032 cannot run while the DMA machine is running.

DMA must be done to complete the SCSI work. Since the SCSI code is running at interrupt level and since there are only two interrupt levels, the SCSI interrupt must be a low level interrupt, and the DMA must be a high level interrupt.

The SCSI code is designed to be able to supply command responses immediately after commands are received, so there is no delay between the time a command is received and the time the response is sent. This feature makes efficient use of the SCSI bus and of the slower LSI53C040 core. It also means that the SCSI code does not need to disconnect from the initiator/host after the command is received, and then reconnect after the data is ready to send, minimizing the overall time spent on the SCSI bus. This is necessary because the LSI53C040 cannot arbitrate for the high SCSI bus (not all 8 bits), so the LSI53C040 cannot arbitrate for the bus to perform the reconnection/reselection whenever the LSI53C040 is placed at a high SCSI ID [15:8]. The LSI53C040 could disconnect and reconnect if it were placed at a low ID [7:0], but that would place unwanted restrictions on the general use of this code.

# 2.4 8032-Based Timer

An 8032-based timer is also operated at interrupt level. This makes the time keeping more accurate than polling, and since the routine is of minimal size it does not seriously affect performance. Currently this time keeping is only used to control the periodic scanning of the TWS input devices, so timing accuracy is not important. However, the time keeping feature may be used in the future for more time-critical functions.

# 2.5 TWS Bus

During normal operation, the TWS bus is only used as an input bus. The TWS bus is also used for booting (or autodownload from flash), and to update the contents of the flash by using the SCSI bus, but these are not part of normal operation. The devices currently supported on the TWS bus are the Dallas 1621 and the National LM75 and LM78. These devices do not need to be monitored constantly, and some of them (most notably the LM78) need to be "left alone" for a sufficient period of time so that they can update all of their collected data. This means that these parts should be polled periodically. The host/initiator will probably/realistically poll the SAF-TE software every few minutes, so the SAF-TE software need only poll the TWS parts every few seconds. The software can poll the TWS parts continuously or as infrequently as every 8.5 minutes. Typically, the software will be configured to poll every 2 seconds. This interval is specified by the user with the configuration utility. The user can request that the software poll continuously (that is, every 0 seconds), but LSI Logic does not recommend this.

The TWS polling routines (mentioned above) collect their data and place that data in the SCSI/SAF-TE command response packets (just as the state machine does) so that these packets always contain up-to-date information for immediate transmission to the host/initiator when it is requested.

# 2.6 Power-On/Start-up

The first job during power-on/start-up is to test the reliability of the **config** data structure. The structure is checked for correct length and checksum. If either of these is wrong, the SAF-TE software will not run. Nearly all of the information in the **config** data structure is user-specific, and virtually all of the firmware is **not** specific to any user, so the software cannot signal that the **config** structure is corrupt. It is expected that the users customizing this software will make changes to light a failure LED or otherwise signal the general failure of the SAF-TE system for this condition, as well as for other similar errors.

Once validated, the information in the **config** data structure can be used to initialize the SCSI hardware, the TWS hardware, and the 52 I/O lines. When initialization is completed, interrupts are enabled and normal (background) processing begins.

# 2.7 Normal Processing

The background process first checks the health of the SCSI interrupt level software. If unhealthy, the hardware is reinitialized and the SCSI interrupt is enabled.

The background process handles the TWS polling if it is time. The background process also makes one pass through the state machine program to update the status of all the I/O pins. This process is repeated indefinitely.

The SCSI interrupt level code attempts to handle all normal SCSI errors in a straight-forward manner. If any abnormal errors occur, the interrupt software takes the simplest approach - it goes bus free. This is always a valid approach to errors by a SCSI target, plus it gets the LSI53C040 core off the bus as quickly as possible. Since there are few commands and no variants, the SAF-TE protocol works well in a production environment (the assumption is that issues relating to the host and target software have been resolved). When the SCSI interrupt software goes bus free, it signals the background process that it has done so by disabling the SCSI interrupt. When the background process starts the next pass of its infinite loop (above), it detects the unhealthy state (as mentioned above), reinitializes the hardware, and re-enables the interrupt.

# 2.8 Interrupts

This section provides information on the 8032 processor and LSI53C040 interrupts.

## 2.8.1 8032 Processor Interrupts

The 8032 processor has two external interrupts (INT0 and INT1), which may be set to be level or edge triggered depending upon the setting of the control bits in the TCON register.

IT0 = H -> interrupt on falling edge of INT0 (edge triggered)

$IT0 = L \rightarrow interrupt \text{ if } INT0 = LOW \qquad (level triggered)$  $IT1 = H \rightarrow interrupt \text{ on falling edge of } INT1 (edge triggered)$  $IT1 = L \rightarrow interrupt \text{ if } INT1 = LOW \qquad (level triggered)$

Both of these external interrupts may be configured as inputs from any of the LSI53C040 core interrupts.

Other interrupt sources from the 8032:

SERIAL RX TX TIMER0 TIMER1 TIMER2

## 2.8.2 LSI53C040 Interrupts

The LSI53C040 interrupts may be input on either INT0 or INT1 of the 8032 core external interrupts. Refer to Section 3.4.3, "Interrupts," page 3-39 for interrupt details about the SCSI Core, DMA Core, TWS (2), Timers, and SFF-8067. The interrupt registers are:

- Interrupt Status Register (0xFE04): Find source of interrupt.

- Interrupt Mask Register (0xFE0D): H = enable L = disable

- Interrupt Destination Register (0xFE0E): routing to INT0 and INT1

# 2.9 Debugging

Debugging may be done using **printf()** calls with the output going to the serial port of the 8032. You may then use any terminal emulator to capture the output from the serial port. The serial port uses software flow control using XON/XOFF. The configuration for the serial port is:

19200 baud, N-8-1 with XON/XOFF flow control (19200 bits per second, no parity, 8 data bits, 1 stop bit)

# 2.10 Setting Up A Development Environment

Development may be done using a DOS shell under Windows NT 4.0 and running batch files to run the make process.

Before you start, verify that the Archimedes tools have been installed into the C:\C251 directory, the Borland C++ Version 4.5 has been installed into the C:\BC45 directory, and the SAF-TE source code has been placed in the C:\SAFTE directory.

To set up a development environment, follow these steps:

- Step 1. Install Archimedes C-51

- Step 2. Install Borland C++ Version 4.5

- Step 3. Change the path statement in MAKEBOOT.BAT to include:

C:\BC45\BIN;C:\C251\BIN

Step 4. Set the following environment variables in MAKEBOOT.BAT:

C511NC = C:\C251\INC C51LIB = C:\C251\LIB C2511NC= C:\C251\INC C251LIB= C:\C251\LIB

Step 5. Your development environment should now be setup and you are ready to run MAKEALL.BAT at the command prompt from the C:\SAFTE directory to create the .HEX files to download into the EEPROM on your SAFTE board.

### 2.10.1 Development Tools

Company: Borland

Product: Borland C++

Version: 4.5

<u>Note:</u> Use this product to compile the configuration program that allows the user to assign a specific configuration for the LSI53C040 board.

Company: Archimedes Software

Product: 8051/251 Development Suite

Version: 5.50bA

Includes: Compiler, Assembler, SimCASE for Windows

WEB URL: http://www.archimedesinc.com

**Phone:** (425) 822-6300

<u>Note:</u> The 8051 tools are the only tools currently needed, and purchasing the 251 tools is not required. Future releases of the firmware may use updated versions of the 8051 compiler, (such as 8051-IDE-V6NT).

This information was available from Archimedes Software as of October 13, 1998:

| Part Number    | Price  |

|----------------|--------|

| 8051-IDE-V6NT  | \$1995 |

| 8051-CASM-V6NT | \$1495 |

## 2.10.2 Source Code Composition

Table 2.1 shows the lines of code associated with each of the files that comprise the source code:

| Filename     | Lines of Code | Blanks +<br>Comments | Code + Blanks +<br>Comments |

|--------------|---------------|----------------------|-----------------------------|

| bootinit.asm | 56            | 79                   | 135                         |

| bootload.c   | 370           | 160                  | 530                         |

| config.c     | 1931          | 421                  | 2352                        |

| config.h     | 145           | 49                   | 194                         |

| loader.h     | 28            | 17                   | 45                          |

| reg040.h     | 107           | 108                  | 215                         |

| reg51.h      | 63            | 18                   | 81                          |

| safeinit.asm | 13            | 15                   | 28                          |

| safte.c      | 2371          | 1508                 | 3879                        |

| Total        | 5084          | 2375                 | 7459                        |

Table 2.1 Source Code Files

As shown above, the majority of the code is written in "C" and very little is actually written in assembler.

# 2.10.3 Register Naming Translations

This section provides detailed information about the 8032 Registers, LSI53C040 Registers, TWS Registers, and miscellaneous registers.

#### 2.10.3.1 8032 Registers

Standard 8051 register names are currently used for the 8032 core. Table 2.2 shows the register name, address, and description.

| Special Function<br>Register (SFR) Name | Address | Description               |

|-----------------------------------------|---------|---------------------------|

| P0                                      | 0x80    | Port 0                    |

| P1                                      | 0x90    | Port 1                    |

| P2                                      | 0xA0    | Port 2                    |

| P3                                      | 0xB0    | Port 3                    |

| PSW                                     | 0xD0    | Program Status Word       |

| ACC                                     | 0xE0    | Accumulator               |

| В                                       | 0xF0    | B Register                |

| SP                                      | 0x81    | Stack Pointer             |

| DPL                                     | 0x82    | Data Pointer High         |

| DPH                                     | 0x83    | Data Pointer Low          |

| PCON                                    | 0x87    | Power Control             |

| TCON                                    | 0x88    | Timer/Counter Control     |

| TMOD                                    | 0x89    | Timer/Counter Mode        |

| TLO                                     | 0x8A    | Timer/Counter 0 Low Byte  |

| TL1                                     | 0x8B    | Timer/Counter 1 Low Byte  |

| ТНО                                     | 0x8C    | Timer/Counter 0 High Byte |

| TH1                                     | 0x8D    | Timer/Counter 1 High Byte |

| IE                                      | 0xA8    | Interrupt Enable          |

| IP                                      | 0xB8    | Interrupt Priority        |

| SCON                                    | 0x98    | Serial Control            |

| SBUF                                    | 0x99    | Serial Data Buffer        |

Table 2.2

Special Function Register Names

### 2.10.3.2 LSI53C040 Registers

The following registers have been named differently than in the LSI53C040 Technical Manual. These are memory mapped into external data space of the 8032 at the addresses shown, and are all 8-bit registers.

| Firmware Register Name       | Address | LSI53C040<br>Register Name |

|------------------------------|---------|----------------------------|

| SCSI_DATA_REG                | 0xFC00  | CSD or ODR                 |

| INITIATOR_COMMAND_REG        | 0xFC01  | ICR                        |

| MODE_REG                     | 0xFC02  | MR                         |

| TARGET_COMMAND_REG           | 0xFC03  | тс                         |

| SCSI_BUS_STATUS_REG          | 0xFC04  | CSB or SER                 |

| BUS_STATUS_REG               | 0xFC05  | BSR or SDR                 |

| DMA_START_TARGET_RECEIVE_REG | 0xFC06  | SDTR                       |

| RESET_PARITY_INTERRUPT_REG   | 0xFC07  | RPI or SDIR                |

| SCSI_HIGH_DATA_REG           | 0xFC08  | CSDHI                      |

| HIGH_SELECT_ENABLE_REG       | 0xFC0C  | SENHI                      |

| DMA_STATUS_REG               | 0xFC10  | DS                         |

| DMA_TRANSFER_LENGTH_REG      | 0xFC11  | DTL                        |

| DMA_ADDR_LOW_REG             | 0xFC12  | DSDL                       |

| DMA_ADDR_HIGH_REG            | 0xFC13  | DSDH                       |

| DMA_INTERRUPT_REG            | 0xFC14  | DMAI                       |

Table 2.3 SCSI Core/SFF-8067 Registers

| Firmware Register Name | Address | LSI53C040<br>Register Name |

|------------------------|---------|----------------------------|

| TWS_0_DATA             | 0xFD00  | none                       |

| TWS_0_CSR              | 0xFD01  | none                       |

| TWS_1_DATA             | 0xFD02  | none                       |

| TWS_1_CSR              | 0xFD03  | none                       |

| LOAD_CHECKSUM          | 0xFD04  | none                       |

| LOAD_ADDR_H            | 0xFD05  | reserved                   |

| LOAD_ADDR_L            | 0xFD06  | reserved                   |

Table 2.4 TWS Registers

### Table 2.5 Miscellaneous Registers

| Firmware Register Name | Address | LSI53C040<br>Register Name |

|------------------------|---------|----------------------------|

| WDT_CON                | 0xFE00  | WDTC                       |

| WDT_SECOND             | 0xFE01  | WDSC                       |

| WDT_FINAL              | 0xFE02  | WDFC                       |

| MISC_CON               | 0xFE03  | MCR                        |

| INT_STATUS             | 0xFE04  | ISR                        |

| TIM_1_CON              | 0xFE05  | T1C                        |

| TIM_1_THRESHOLD        | 0xFE06  | T1TH                       |

| TIM_1_SECOND           | 0xFE07  | T1SC                       |

| TIM_1_FINAL            | 0xFE08  | T1FC                       |

| TIM_2_CON              | 0xFE09  | T2C                        |

| TIM_2_THRESHOLD        | 0xFE0A  | T2T                        |

| TIM_2_SECOND           | 0xFE0B  | T2SC                       |

| Firmware Register Name | Address | LSI53C040<br>Register Name |

|------------------------|---------|----------------------------|

| TIM_2_FINAL            | 0xFE0C  | T2FC                       |

| INT_MASK               | 0xFE0D  | IMR                        |

| INT_DESTINATION        | 0xFE0E  | IDR                        |

# Table 2.5 Miscellaneous Registers (Cont.)

# Table 2.6System Registers

| Firmware Register Name | Address  | LSI53C040<br>Register Name |

|------------------------|----------|----------------------------|

| POW_CON_0_MASK         | 0xFF00   | RES                        |

| POW_CON_0              | 0xFF01   | POCO                       |

| POW_CON_1_MASK         | 0xFF02   | RES                        |

| POW_CON_1              | 0xFF03   | POCI                       |

| LED_BLINK              | 0xFF04   | LBR                        |

| SYS_CON                | 0xFF05   | SYSCTRL                    |

|                        |          | •                          |

| IO_0_OUT               | 0xFF08   | MPO0                       |

| IO_0_ENABLE            | 0xFF09   | MPE0                       |

| IO_0_IN                | 0xFF0A   | MPI0                       |

| IO_0_MASK              | 0xFF0B   | MPLM0                      |

| IO_0_LATCH             | 0xFF0C   | MPL0                       |

| IO_0_PULLDOWN          | 0xFF0D   | MPPE0                      |

|                        | <b>-</b> | •                          |

| IO_1_OUT               | 0xFF10   | MPO1                       |

| IO_1_ENABLE            | 0xFF11   | MPE1                       |

| IO_1_IN                | 0xFF12   | MPI1                       |

| Firmware Register Name | Address | LSI53C040<br>Register Name |

|------------------------|---------|----------------------------|

| IO_1_MASK              | 0xFF13  | MPLM1                      |

| IO_1_LATCH             | 0xFF14  | MPL1                       |

| IO_1_PULLDOWN          | 0xFF15  | MPPE1                      |

|                        |         |                            |

| IO_2_OUT               | 0xFF18  | MPO2                       |

| IO_2_ENABLE            | 0xFF19  | MPE2                       |

| IO_2_IN                | 0xFF1A  | MPI2                       |

| IO_2_MASK              | 0xFF1B  | MPLM2                      |

| IO_2_LATCH             | 0xFF1C  | MPL2                       |

| IO_2_PULLDOWN          | 0xFF1D  | MPPE2                      |

|                        |         |                            |

| IO_3_OUT               | 0xFF20  | MPO3                       |

| IO_3_ENABLE            | 0xFF21  | MPE3                       |

| IO_3_IN                | 0xFF22  | MPI3                       |

| IO_3_MASK              | 0xFF23  | MPLM3                      |

| IO_3_LATCH             | 0xFF24  | MPL3                       |

| IO_3_PULLDOWN          | 0xFF25  | MPPE3                      |

|                        |         |                            |

| LED_00_OUT             | 0xFF30  | MLOOL                      |

| LED_01_OUT             | 0xFF31  | MLO                        |

| LED_00_IN              | 0xFF32  | MLIOL                      |

| LED_01_IN              | 0xFF33  | MLIOH                      |

| LED_00_MASK            | 0xFF34  | MLLMOL                     |

| LED_01_MASK            | 0xFF35  | MLLM0H                     |

| LED_00_LATCH           | 0xFF36  | MLLOL                      |

# Table 2.6 System Registers (Cont.)

| Firmware Register Name | Address | LSI53C040<br>Register Name |

|------------------------|---------|----------------------------|

| LED_01_LATCH           | 0xFF37  | MLLOH                      |

|                        |         |                            |

| LED_10_OUT             | 0xFF38  | MLO1L                      |

| LED_11_OUT             | 0xFF39  | MLO1H                      |

| LED_10_IN              | 0xFF3A  | MLI1L                      |

| LED_11_IN              | 0xFF3B  | MLI1H                      |

| LED_10_MASK            | 0xFF3C  | MLLM1L                     |

| LED_11_MASK            | 0xFF3D  | MLLM1H                     |

| LED_10_LATCH           | 0xFF3E  | MLL1L                      |

| LED_11_LATCH           | 0xFF3F  | MLL1H                      |

|                        |         |                            |

| LED_20_OUT             | 0xFF40  | MLO2L                      |

| LED_21_OUT             | 0xFF41  | MLO2H                      |

| LED_20_IN              | 0xFF42  | MLI2L                      |

| LED_21_IN              | 0xFF43  | MLI2H                      |

| LED_20_MASK            | 0xFF44  | MLLM2L                     |

| LED_21_MASK            | 0xFF45  | MLLM2H                     |

| LED_20_LATCH           | 0xFF46  | MLL2L                      |

| LED_21_LATCH           | 0xFF47  | MLL2H                      |

## Table 2.6 System Registers (Cont.)

# 2.10.4 Calling Trees

The three source files that have calling trees are:

- Config.C

- Bootload.C

- Safte.C

All names are function names with the names in all caps being macros.

#### Example:

а

b

c d

the function 'a' has one subfunction 'b' 'b' has two subfunctions 'c' and 'd' 'c' and 'd' have no subfunctions in this example.

#### 2.10.4.1 Summary Calling Tree of Config.C

main abort ..printf .. fprintf ..exit init pin data ask\_questions YorN abort .. fprintf ..fgets ..sscanf ..toupper ask\_text abort .. fprintf ..fgets ..strlen ask scsi id ask\_MtoN abort .. fprintf ..fgets ..sscanf abort zerotoN ask\_MtoN .. fprintf zerotoN ask\_MtoN ask\_pins abort

```

.. fprintf

..fgets

..sscanf

..strcmp

abort

ask_map

abort

.. fprintf

..fgets

..sscanf

ask LM78

ask_MtoN

YorN

..printf

...sprintf

.. fprintf

...sprintf

..printf

..fgets

..sscanf

assign_DM_addrs

abort

..memset

..printf

.. fprintf

fill_config_structure

swap_2_bytes

fill_program

fill_instruction

swap_2_bytes

.. fprintf

fill_output_pin_instruction

abort

fill_instruction

..printf

..min

..printf

checksum

..memset

.. fprintf

create_hex_file

abort

..fopen

..printf

.. fprintf

..fclose

fill_loader_structure

swap_2_bytes

..printf

```

## 2.10.4.2 Summary Calling Tree of Bootload.C

main

tws\_setup

tws\_init

tws\_read

tws\_poll\_bb

tws\_poll\_lrb

tws\_poll\_pin

delay

..moveit

moveit2

#### 2.10.4.3 Summary Calling Tree of Safte.C

```

main

validate config

checksum

init stuff

tws setup

tws_init

background process

init time_keeping

reset_scsi_hw

execute program once

background code load

tws_setup

tws_memory_write

tws write

tws poll bb

tws_poll_lrb

gather_TWS_input

gather_LM78_input

tws setup

tws write

tws read

tws poll bb

tws poll lrb

tws_poll_pin

tws setup

tws write

tws_read

..memset

check condition

ir external0

ir external1

req ack

command_and_data_phases

check condition

do inquiry

invalid_LUN_test

min

send data bytes

req ack

do request sense

min

send_data_bytes

invalid_LUN_test

do read buffer

check_condition

do read enclosure configuration

```

min send data bytes do\_read\_enclosure\_status min send data bytes do\_read\_device\_slot\_status min send data bytes do\_read\_global\_flags min send data bytes do\_send\_diagnostic do test unit ready do write buffer check\_condition get data bytes req ack do\_write\_device\_slot\_status do perform slot operation check condition do send global flags do code load check condition get\_data\_bytes ir serial ir timer0 ir timer1 ir timer2 max

# 2.11 Configuration Examples

The following examples show specific monitoring capabilities of the LSI53C040. Numerous configurations are possible subject to the 28 MPIO and 24 MPLED I/O pins.

# 2.11.1 Example 1

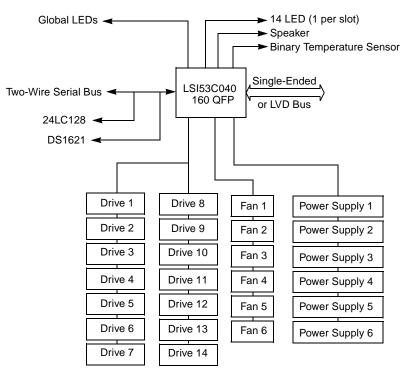

This example (Figure 2.3) shows an implementation supporting the maximum number of SCSI Devices (14) on an LVD bus, six power supplies, and six fans without any external logic. Note that the devices are on the LVD bus due to the initiator and the LSI53C040 each consuming a SCSI ID.

### Figure 2.3 System Configuration

Table 2.7 below summarizes the MPIO/MPLED pin count required for this implementation. There are seven other available MPLEDs for LED functions.

#### Table 2.7 MPLED/MPIO Pin Usage for Example 1

| SAF-TE Feature                              | MPIO Pins | MPLED Pins |

|---------------------------------------------|-----------|------------|

| Device Present signal                       | 14        |            |

| Device Slot LEDS                            |           | 14         |

| Drive Ready for Use signal                  |           |            |

| Drive Ready for<br>Insertion/Removal signal |           |            |

| Fan Monitoring (single input)               | 6         |            |

| Power Supply (single input)                 | 6         |            |

| Fan Monitoring (dual input)                 |           |            |

| SAF-TE Feature            | MPIO Pins | MPLED Pins |

|---------------------------|-----------|------------|

| Power Supply (dual input) |           |            |

| Binary Temperature Sensor | 1         |            |

| Speaker                   | 1         |            |

| Door Lock                 |           |            |

| Global Enclosure LED      |           | 1          |

| Global Array LED          |           | 1          |

| Global Drive LED          |           | 1          |

| TOTAL                     | 28        | 17         |

# Table 2.7 MPLED/MPIO Pin Usage for Example 1 (Cont.)

# 2.11.2 Example 2

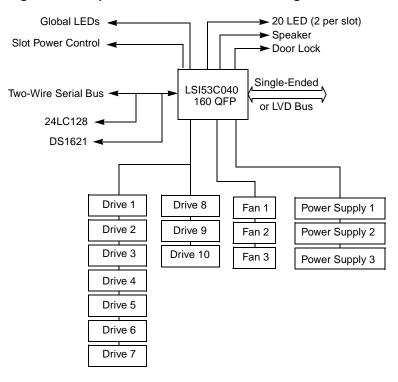

This example (Figure 2.4) shows a configuration using the optional drive slot power feature. Up to 10 drives with two LEDs per drive slot, 3 single input fans, three single input power supplies, one speaker, and one door lock are supported.

Table 2.8 below summarizes the MPIO/MPLED pin count required for this implementation. There is one additional available MPLED for other LED functions.

| SAF-TE Feature                              | MPIO Pins | MPLED Pins |

|---------------------------------------------|-----------|------------|

| Device Present signal                       | 10        |            |

| Device Slot LEDS                            |           | 20         |

| Drive Ready for Use signal                  | 10        |            |

| Drive Ready for<br>Insertion/Removal signal |           |            |

| Fan Monitoring (single input)               | 3         |            |

| Power Supply (single input)                 | 3         |            |

| Fan Monitoring (dual input)                 |           |            |

| Power Supply (dual input)                   |           |            |

| Binary Temperature Sensor                   |           |            |

| Speaker                                     | 1         |            |

| Door Lock                                   | 1         |            |

| Global Enclosure LED                        |           | 1          |

| Global Array LED                            |           | 1          |

| Global Drive LED                            |           | 1          |

| TOTAL                                       | 28        | 23         |

Table 2.8 MPLED/MPIO Pin Usage for Example 2

## 2.11.3 Example 3

This example (Figure 2.5) shows a configuration with dual input fans and power supplies. Up to 14 drives with one LED per drive slot, three dual input fans, three dual input power supplies, one speaker, and one door lock are supported.

Figure 2.5 Dual Fans and Power Supplies Configuration

Table 2.9 below summarizes the MPIO/MPLED pin count required for this implementation. One additional MPLED is available for other LED functions.

#### Table 2.9 MPLED/MPIO Pin Usage for Example 3

| SAF-TE Feature                              | MPIO Pins | MPLED Pins        |

|---------------------------------------------|-----------|-------------------|

| Device Present signal                       | 14        |                   |

| Device Slot LEDS                            |           | 14                |

| Drive Ready for Use signal                  | 10        |                   |

| Drive Ready for<br>Insertion/Removal signal |           |                   |

| Fan Monitoring (single input)               |           |                   |

| Power Supply (single input)                 |           |                   |

| Fan Monitoring (dual input)                 | 2         | 4 (Used as MPIOs) |

| SAF-TE Feature            | MPIO Pins | MPLED Pins        |  |

|---------------------------|-----------|-------------------|--|

| Power Supply (dual input) |           | 6 (Used as MPIOs) |  |

| Binary Temperature Sensor |           |                   |  |

| Speaker                   | 1         |                   |  |

| Door Lock                 | 1         |                   |  |

| Global Enclosure LED      |           | 1                 |  |

| Global Array LED          |           | 1                 |  |

| Global Drive LED          |           | 1                 |  |

| TOTAL                     | 28        | 23                |  |

# Table 2.9 MPLED/MPIO Pin Usage for Example 3 (Cont.)

# Chapter 3 SAF-TE Source Code

This chapter discusses the SAF-TE source code and includes these topics:

- Section 3.1, "SAF-TE Source Code Overview," page 3-1

- Section 3.2, "Boot Module," page 3-2

- Section 3.3, "Configuration Module," page 3-3

- Section 3.4, "SAF-TE Module," page 3-19

- Section 3.5, "Frequently Asked Questions (FAQ)," page 3-49

For additional information about supporting serial, ISA, SCSI, and 8067 data transfers, refer to Appendix A, "LSI53C040 Board Utilities."

# 3.1 SAF-TE Source Code Overview

The SAF-TE source code is comprised of the executable config.exe, a partial boot file, and the C-source file safte.c. The boot and configuration module sections provide a brief overview regarding their structures. The SAF-TE Module section includes compilation instructions, and description of the safte.c source code main program. The safte.c program is designed to run as firmware on the LSI53C040 chip. Additionally, this module discusses Interrupt Service Routines and Error Reporting. The FAQ section provides the firmware developer with answers to potential questions that may arise from using the safte.c source code.

# 3.2 Boot Module

The boot module consists of the concatenation of the user configurable component, loader.hex, and the generic boot component, bootload.hex. In Chapter 5, "Configuration Data and the Configuration Utility," the combined file that is referenced below

boot.hex = loader.hex + bootload.hex

is downloaded to the boot EEPROM on new boards either by placing the chip in a TWS programmer or the code can be downloaded over the ISA bus to the serial EEPROM (demonstration boards only). Once firmware is present on the LSI53C040 board, the boot code can be updated in exactly the same manner as the firmware. See Section 3.4.2.3, "Firmware Update," page 3-33 for more information.

On a power up, the values of the pull-up resistors A8–A11 determine the TWS bus and the chip address on that bus from which the boot code is automatically downloaded. Execution of the boot code results in the contents of the file loader.hex being saved into address HMA\_LOADER\_OPTIONS (3FE0h) of external data memory. In addition, the SAF-TE firmware is being downloaded from the serial EEPROM into external data memory. The serial EEPROM that contains the SAF-TE firmware is specified by the contents of loader.hex.

<u>Note:</u> The automatic firmware downloads can be disabled by modifying the jumper settings on the LSI53C040 board. See the section entitled "Power On Configuration Options," in the *LSI53C040 Enclosure Services Processor Technical Manual* for specific information. The maximum size of the firmware is limited to 12912 or 0x2FA0 bytes.

The generic boot component, bootload.hex, is created by compiling the C-source file bootload.c, the assembly source code bootload.asm, linking the results, and creating the hex output file. The directory 8051 contains a makefile that will execute using the Borland 4.5 make function or the Watcom 11.0 Microsoft make clone, *nmake*. To recompile the bootload.hex component, type on the command line:

```

c:\8051> nmake clean c:\8051> nmake all

```

The first component will delete the object, hex, and other intermediate files, while the second option will generate new files. Note that individual targets may be recompiled or linked by following the *make* command with the target specification.

Finally, the bootload.c source file contains four switches that can be set to change the characteristics of the resulting boot code. Each of the switches is defined in Table 3.1.

| Define             | Action when TRUE                                                                                                                                |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| LOADER_DEBUG       | Enables Timer 2 to be the clock on the serial output line. Enables error and status messages and display of external memory values during boot. |

| LOADER_DELAY_LEDS  | Turns on then off each LED in sequence during boot.                                                                                             |

| LOADER_MEMORY_TEST | Enables the test byte 0x55 to be written<br>to external memory for test purposes.<br>(When FALSE, the memory test does<br>nothing.)             |

| HALF_SPEED         | Sets the overflow rate for Timer 2.<br>Requires LOADER_DEBUG to be TRUE.                                                                        |

Table 3.1

Source file - bootload.c - Switches

Currently, these switches cannot be altered through compile time options. The source code #Define statements must be modified. Default settings have all switches set to FALSE.

# 3.3 Configuration Module

The utility config.exe is designed to allow users to configure the SAF-TE software to meet their unique requirements. Upon execution, this utility populates the **loader\_options** and **config** data structures, then saves these structures in the Intel formatted files loader.hex and config.hex. The data format for these files is:

```

:numbytes address fill data sum

```

where:

| numbytes | is the number of bytes of data (stored as 1 byte)       |

|----------|---------------------------------------------------------|

| address  | is a 2 byte address where data is to be written         |

| fill     | has the value 00                                        |

| data     | is the data to be written (a maximum of 16 bytes)       |

| sum      | is a 1 byte checksum over address and data in that line |

Generation of the executable file config.exe can be accomplished by executing one of the two makefiles in the *config* directory. If a Watcom 11.0 compiler is resident, use the makefile entitled *makefile.watcom* and run with the command *nmake*. If a Borland 4.5 compiler is resident, use the makefile entitled *makefile.bc45* and run with the command *make*. The result of the execution of config.exe is independent of which compiler is used. To recompile the config.exe file, type on the command line:

c:\config> nmake clean c:\config> nmake config.exe (or just nmake)

The first component will delete the object and executable files, while the second will generate new files.

<u>Note:</u> See makefile.txt for more information. However, to use the *makefile.watcom*, type on the command line:

```

c:\config>nmake\Fmakefile.watcom clean

name\Fmakefile.watcom config.exe

```

## 3.3.1 Loader\_Options Data Structure

The **loader\_options** data structure, defined in loader.h, stores the bus number, bus speed, chip identification, beginning address, and the maximum image length for the "first" and "second" images. Additionally, this data structure stores the bus and address of the EEPROM that contains the boot code. By default, upon power up, the "first" image is defined as active and the "second" image is defined as inactive. The file loader.hex is only 68 bytes, with writes beginning at address 0x0006 in external data memory (Program Tag LMA\_LOADER\_OPTIONS).

Note: Of the 68 bytes contained in the loader.hex file, only 21 bytes are data. The remaining 47 bytes consist of the Intel format and checksum bytes.

# 3.3.2 Config Data Structure

The **config** data structure, defined in config.h, stores the enclosure configuration and data to be returned in response to any of the SAF-TE read commands. Additionally, this data structure polls intervals for refreshing enclosure status information, register storage, data memory, and program memory. The program memory stores the state machine that is generated by user responses to mappings of the MPLED and MPIO pins. To emphasize, config.hex was created for a specific system. Changes to that system will require change to this configuration file and the firmware. The initial write address for config.hex is address 0x0040 in external data memory (Program Tag CONFIG\_BASE\_ADDRESS). Execution of the utility is described in Chapter 5, "Configuration Data and the Configuration Utility."

The **config** data structure can be thought of as having ten different elements or sections. The developer must understand how these elements are populated and their function is essential if the safte.c source code is modified. The main elements of the **config** data structure are:

- 1. General information Contains miscellaneous configuration information.

- 2. Enclosure configuration Lists the total number of fans, power supplies, etc.

- 3. Inquiry Response Information Contains the data to be returned in response to an inquiry command.

- 4. Timer Setup Information Specifies the polling interval and the 80C32 Timer 1 and Timer 2 initialization values.

- 5. TWS Temperature Sensor Information (on TWS bus) Contains user specified sensor type and ID value.

- 6. LM78 Configuration Contains the user specified configuration for each LM78 (a maximum of one per bus).

- 7. TWS Bus Configuration Contains the user specified bus speed and ID information.

- Register and Device State Maps Not configurable regions. The register maps save the LSI53C040 system registers and the device state map is used to decode the Device-To-State member of the state machine.

- Data memory Contains the LED responses to different states, SCSI ID values, and initialization values. Data memory is modified during firmware execution.

- 10. Program memory Contains the state machine instructions. Program memory is not modified during firmware execution.

For illustration purposes, a simple config.hex file was dissected and its contents are listed below. In the listing, **bold** indicates a user input, *italics* indicate a computed value based on user inputs, and regular text indicates values that cannot be altered by the user.

1. General Information:

config structure length = 0xB105 Scsi ID (in bit form) = 0x80

<u>Note:</u> IDs between (0–7) represented as (1<<ID) << 8 while the three highest IDs are 0x0080, 0x0040 and 0x0020 respectively.

```

Scsi lun = 0x00

```

```

Parity (1 = enabled/0 = disabled) = 0

Code load (1 = enabled/ 0 = disabled) = 0

Temperature Units (1 = Celsius/0 = Fahrenheit) = 1

Read Enclosure Status command length = 0x0F

Read device slot status command length = 0x08

Write device slot status command length = 0x06

Data Memory Index: Read Enclosure Status = 0x42

Data Memory Index: Temperature = 0x4C

Data Memory Index: Temperature Bits = 0x4E

Data Memory Index: SCSI ID Data = 0x48

Data Memory Index: Device Slot Status = 0x51

Data Memory Index: Slot Operation = 0x59

Data Memory Index: Global Flags = 0x5F

```

2. Enclosure Configuration:

```

Number of Fans (1-single, 1-dual, 1-TWS) = 3

Number of Power Supplies (1-single, 1-dual, 1-TWS) = 3

Number of Device Slots = 2

Number of Door Locks = 1

Number of Temperature Values (TWS sensors) = 2

Number of Speakers = 1

Number of Temperature Bits (single wire sensors) = 82

```

Note: If Celsius, bit #7 is 1; else bit #7 is 0.

3. Inquiry Response Information:

Peripheral Qualifier = 0x00 ANSI Version = 0x02 Response Format = 0x02 Additional Length = 0x31 **Vendor ID = tester#1 Product ID = this\_is\_product!** Firmware Revision Level = B004 **Enclosure ID = enclos1 Channel ID = 0** Interface ID = SAF-TE Specification Level = 1.00

4. Timer Setup Information:

Timer High = 0x0E Timer Low = 0xE0 Timer 1 Rollover = 0x12 Timer 2 Rollover = 0x06 **TWS Poll Interval = 20 (sec)**  5. TWS Temperature Sensor Information:

| Sensor<br>Number | Chip<br>ID | Chip<br>Type | Chip<br>Label | State<br>0 = unitialized<br>1 = initialized |

|------------------|------------|--------------|---------------|---------------------------------------------|

| 0                | 0x9A       | 0x01         | LM75          | 0                                           |

| 1                | 0x97       | 0x02         | DS1621        | 0                                           |

| 2                | 0x42       | 0x00         | Unknown       | 0                                           |

| 3                | 0x42       | 0x00         | Unknown       | 0                                           |

Chip ID = 0x90 | (address << 1) | bus # (for LM75 and DS1621)

Chip ID = 0x50 | (address << 1) | bus # (for LM78)

6. LM78 Configuration:

**LM78 on Bus # 0** (User specified NO LM78 on Bus 0) State (*0=uninitialized/1=initialized/0xFF=nonexistent*) = 0xFF No. of Errors during initialization = 0x00 Fan Divisor = 0x00(Fan Divisor = (first\*64 + second\*16))

| Power<br>Supply | Minimum<br>Voltage | Maximum<br>Voltage | Data Memory<br>Index |

|-----------------|--------------------|--------------------|----------------------|

| 0               | 0x00               | 0x00               | 0x00                 |

| 1               | 0x00               | 0x00               | 0x00                 |

| 2               | 0x00               | 0x00               | 0x00                 |

| 3               | 0x00               | 0x00               | 0x00                 |

| 4               | 0x00               | 0x00               | 0x00                 |

| 5               | 0x00               | 0x00               | 0x00                 |

| 6               | 0x00               | 0x00               | 0x00                 |

| Fan<br>Number | Maximum<br>Speed | Data Memory<br>Index |

|---------------|------------------|----------------------|

| 0             | 0x00             | 0x00                 |